**UNIVERSIDADE DO ESTADO DE SANTA CATARINA – UDESC

CENTRO DE CIÊNCIAS TECNOLÓGICAS – CCT

PROGRAMA DE PÓS-GRADUAÇÃO STRICTO SENSU EM COMPUTAÇÃO APLICADA**

**DISSERTAÇÃO DE MESTRADO**

**TRATAMENTO DE REQUISITOS NÃO-FUNCIONAIS EM SISTEMAS DE TEMPO-REAL EMBARCADOS IMPLEMENTADOS EM VHDL/FPGA**

**MARCELA LEITE**

**JOINVILLE, 2014**

**MARCELA LEITE**

**TRATAMENTO DE REQUISITOS NÃO-FUNCIONAIS EM

SISTEMAS DE TEMPO-REAL EMBARCADOS IMPLEMENTADOS

EM VHDL/FPGA**

Dissertação apresentada ao Curso de Pós-Graduação Stricto Sensu em Computação Aplicada, na Universidade do Estado de Santa Catarina, como requisito parcial para obtenção do grau de Mestre em Computação Aplicada.

Orientador: Dr. Marco A. Wehrmeister

Coorientador: Dr. Cristiano D. Vasconcellos

**JOINVILLE, SC

2014**

L533t Leite, Marcela

Tratamento de requisitos não-funcionais em

sistemas de tempo-real embarcados implementados em

FPGA / Marcela Leite. - 2014.

178 p. : il. ; 21 cm

Orientador: Marco Aurélio Wehrmeister

Coorientador: Cristiano Damiani Vasconcellos

Bibliografia: p. 143-150

Dissertação (mestrado) - Universidade do Estado

de Santa Catarina, Centro de Ciências Tecnológicas,

Programa de Pós-Graduação em Computação Aplicada,

Joinville, 2014.

1. VHDL. 2. Aspectos. 3. Requisitos não-

funcionais. I. Wehrmeister, Marco Aurélio. II.

Vasconcellos, Cristiano Damiani. III. Universidade

do Estado de Santa Catarina. Programa de Pós-

Graduação em Computação Aplicada. IV. Título.

CDD: 005.1 - 20.ed.

**MARCELA LEITE**

**TRATAMENTO DE REQUISITOS NÃO-FUNCIONAIS EM**

**SISTEMAS DE TEMPO-REAL EMBARCADOS**

**IMPLEMENTADOS EM VHDL/FPGA**

Dissertação apresentada ao Curso de Mestrado Acadêmico Computação Aplicada como requisito parcial para obtenção do título de Mestre em Computação Aplicada na área de concentração “Ciência da Computação”.

**Banca Examinadora**

Orientador:

Prof. Dr. Marco Aurélio Wehrmeister

UTFPR

Coorientador:

Prof. Dr. Cristiano Damiani Vasconcellos

CCT/UDESC

**Membros**

Prof. Dr. Gian Ricardo Berkenbrock

UFSC

Prof. Dr. Carlos Eduardo Pereira

UFRGS

Prof. Dr. Fabiano Baldo

CCT/UDESC

**Joinville, SC, 21 de março de 2014.**

Aos meus pais Ivonete Senem Leite e

Germano Leite.

## **AGRADECIMENTOS**

Primeiramente gostaria de agradecer ao meu orientador Dr. Marco A. Wehrmeister por seu empenho, paciência e apoio, tanto ao ministrar as disciplinas do mestrado quanto ao orientar minha dissertação.

Especial agradecimento aos professores que ministraram as disciplinas do mestrado pois o conhecimento repassado em suas disciplinas foi muito importante para o amadurecimento científico desse aluno. Agradeço também a todos os colegas de metrado que compartilharam seus conhecimentos e aos colegas do grupo BDES Diogo e Johnny que participaram desse projeto.

Agradeço especialmente ao meu namorado Antônio J. Fidélis, por seu apoio e companheirismo durante toda a realização do mestrado e a toda minha família por seu apoio e compreensão pelos momentos ausentes. Acima de tudo, agradeço a Deus por proporcionar esse momento.

## RESUMO

LEITE, Marcela. **Tratamento de Requisitos Não-Funcionais em Sistemas de Tempo-Real Embarcados Implementados em VHDL/FPGA.** 2014. 178f. Dissertação (Mestrado Acadêmico em Computação Aplicada - Área: Engenharia de Software) - Universidade do Estado de Santa Catarina. Programa de Pós-Graduação em Computação Aplicada, Joinville, 2014.

Este trabalho apresenta uma abordagem de desenvolvimento de sistemas embarcados implementados em FPGA, que agrega técnicas de MDE e AOSD com o objetivo de sistematizar e automatizar o processo de desenvolvimento. Propõe-se o tratamento e gerenciamento dos requisitos não funcionais para sistemas embarcados desenvolvidos na plataforma FPGA, com o uso do paradigma orientado a aspectos e de métricas que possibilitem o controle no cumprimento das restrições do projeto. Para tanto, a geração do código VHDL a partir do modelo especificado na UML foi implementada neste trabalho. Para essa transformação, um conjunto de regras de mapeamento dos elementos da UML para VHDL foi criado. A partir da análise da literatura foi detalhado um conjunto de requisitos não funcionais para projetos implementados em FPGA, que constituem o *framework* de aspectos para essa plataforma. Novos aspectos foram incluídos no DERAF e implementadas regras de mapeamento para esses. Foram desenvolvidos três estudos de caso utilizando a abordagem e o conjunto de regras de mapeamento criado, nos quais foram implementados três aspectos que tratam requisitos não funcionais dessas aplicações. Com as regras de mapeamento implementadas, foi possível a geração completa do código VHDL, funcional e sintetizável. O uso das métricas identificadas permitiu uma avaliação mais precisa da eficácia da utilização da abordagem proposta. Os resultados encontrados, mostram que a utilização da orientação a aspectos para o tratamento de requisitos não funcionais na descrição de hardware em VHDL, melhora o desempenho do sistema, tem alto impacto sobre o sistema final e contribui para o atendimento de requisitos de projeto como *time-to-market*, reusabilidade e manutenibilidade.

**Palavras-chave:** VHDL. Aspectos. Requisitos não funcionais.

## **ABSTRACT**

This work proposes a design approach for FPGA-based embedded system. Such an approach integrates concepts and techniques from Model Driven Engineering and Aspect Oriented Software Development approaches, in order to systematize and automate the design process. AOSD concepts are used to handle non-functional requirements in FPGA-based embedded system development, in conjunction with a set of metrics to control the project constraints. A subset of relevant non-functional requirements for FPGA-based embedded system, as well as a set of metrics to evaluate these requirements, have been identified through a survey of literature. This subset of non-functional requirements composes an aspect-oriented framework for the FPGA platform, including aspects and their implementation in VHDL. In this sense, new aspects have been included in the Distributed Real-time Aspects Framework (DERAF). Moreover, to support the proposed approach, a code generation tool was enhanced to enable the generation of VHDL descriptions from UML models. A set of mapping rules have been defined to perform this UML-to-VHDL transformation. In order to validate the proposed approach, three case studies have been performed. The obtained results demonstrate the feasibility of combining AOSD and MDE in order to handle non-functional requirements in the design of systems through hardware description languages, such as VHDL. In addition, the modularization achieved by using AOSD affects positively the final embedded system, improving the overall system performance, as well as it contributes to the fulfillment of system requirements, *time-to-market*, reusability and manutenability of design artifacts, such as models and component descriptions.

**Key-words:** VHDL. Aspects. Non-Functional Requirements.

## LISTA DE ILUSTRAÇÕES

|                                                                                                                                                      |     |

|------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 1 – Ambiente de desenvolvimento e produção. . . . .                                                                                           | 32  |

| Figura 2 – Arquitetura genérica de uma FPGA. . . . .                                                                                                 | 34  |

| Figura 3 – Classificação dos requisitos não funcionais. . . . .                                                                                      | 39  |

| Figura 4 – Fluxo do processo de geração de código. . . . .                                                                                           | 44  |

| Figura 5 – Etapas da ferramenta GenERTiCA. . . . .                                                                                                   | 44  |

| Figura 6 – Exemplos de diagramas ACOD e JPDD. . . . .                                                                                                | 46  |

| Figura 7 – Requisitos Não-Funcionais para Projetos baseados em<br>FPGA. . . . .                                                                      | 63  |

| Figura 8 – Exemplo de relatório de utilização de recursos da FPGA. . . . .                                                                           | 70  |

| Figura 9 – Exemplo de relatório de informações de tempo e roteamento do circuito. . . . .                                                            | 71  |

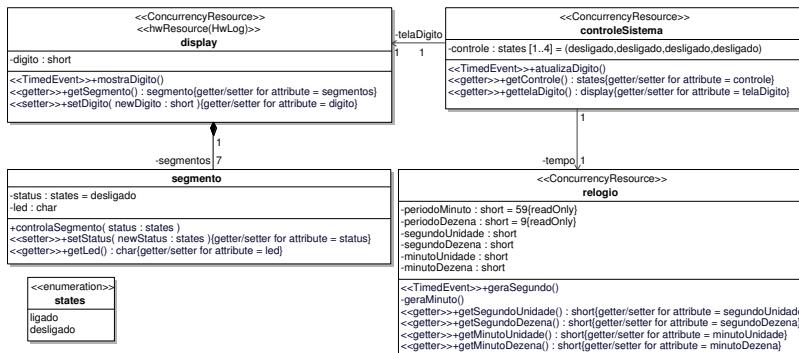

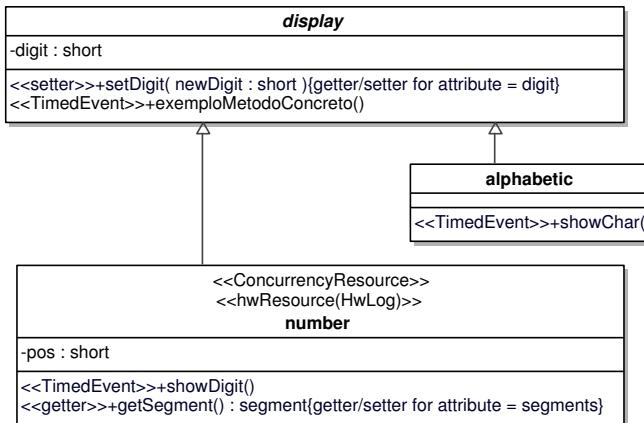

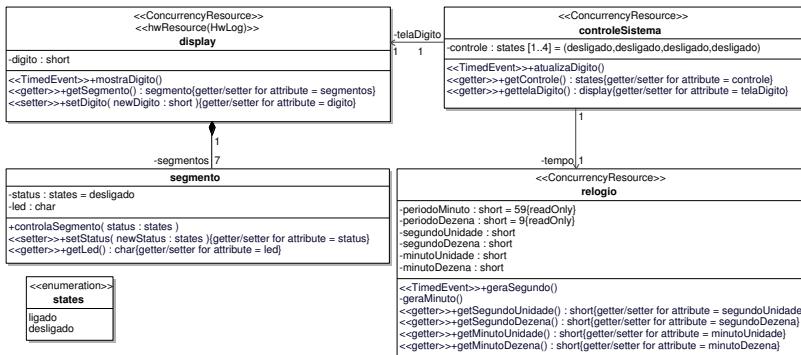

| Figura 10 – Diagrama de classes do projeto Display. . . . .                                                                                          | 76  |

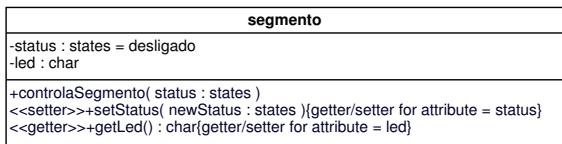

| Figura 11 – Classe <i>Segmento</i> . . . . .                                                                                                         | 76  |

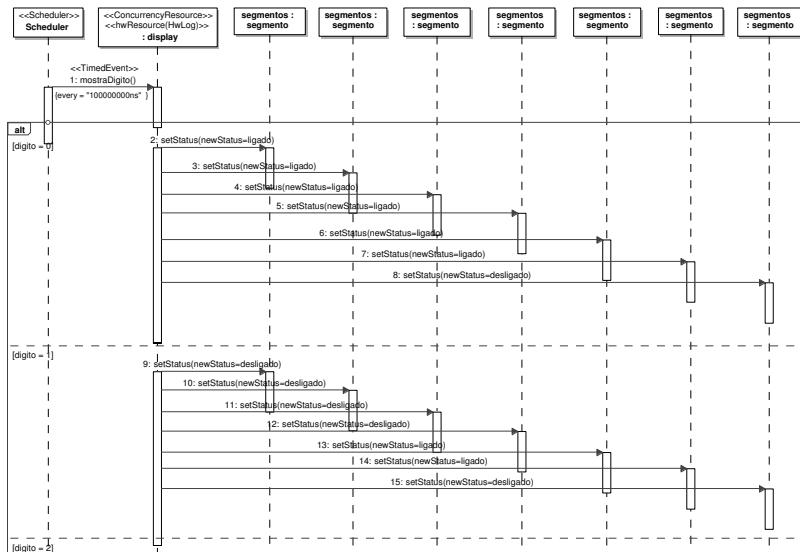

| Figura 12 – Extrato do diagrama de sequência do método <i>mostraDisplay</i> da classe <i>Display</i> . . . . .                                       | 77  |

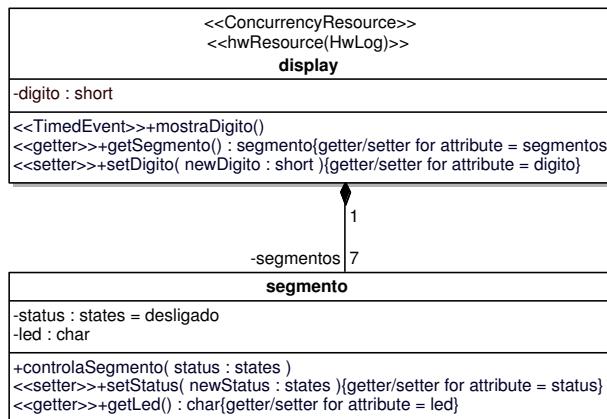

| Figura 13 – Associação das classes <i>Segmento</i> e <i>Display</i> . . . . .                                                                        | 79  |

| Figura 14 – Associação de generalização da classe <i>Display</i> . . . . .                                                                           | 80  |

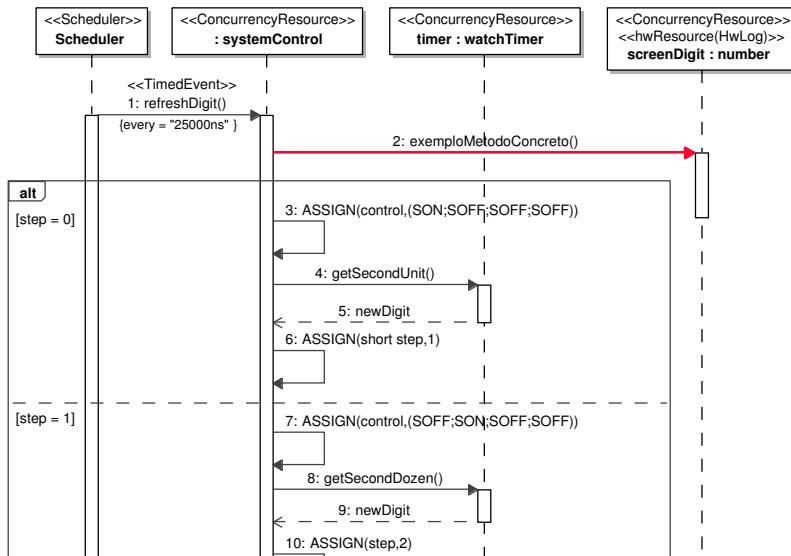

| Figura 15 – Diagrama de sequência para o método <i>exemploMetodoConcreto</i> . . . . .                                                               | 81  |

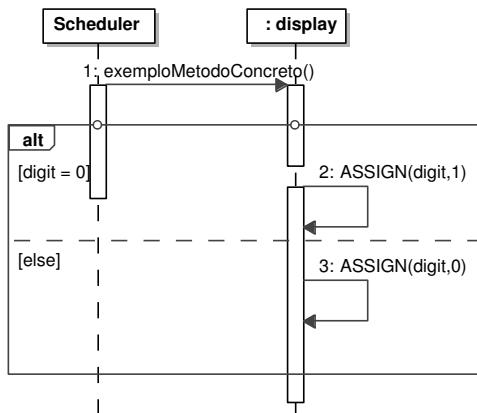

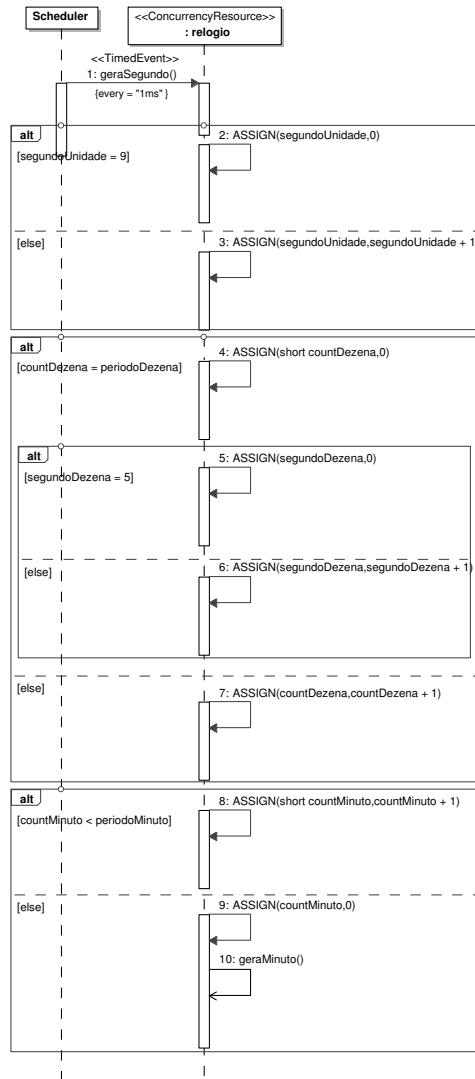

| Figura 16 – Extrato do diagrama de sequência do método <i>geraSegundo</i> e diagrama do método <i>geraMinuto</i> da classe <i>Segmento</i> . . . . . | 85  |

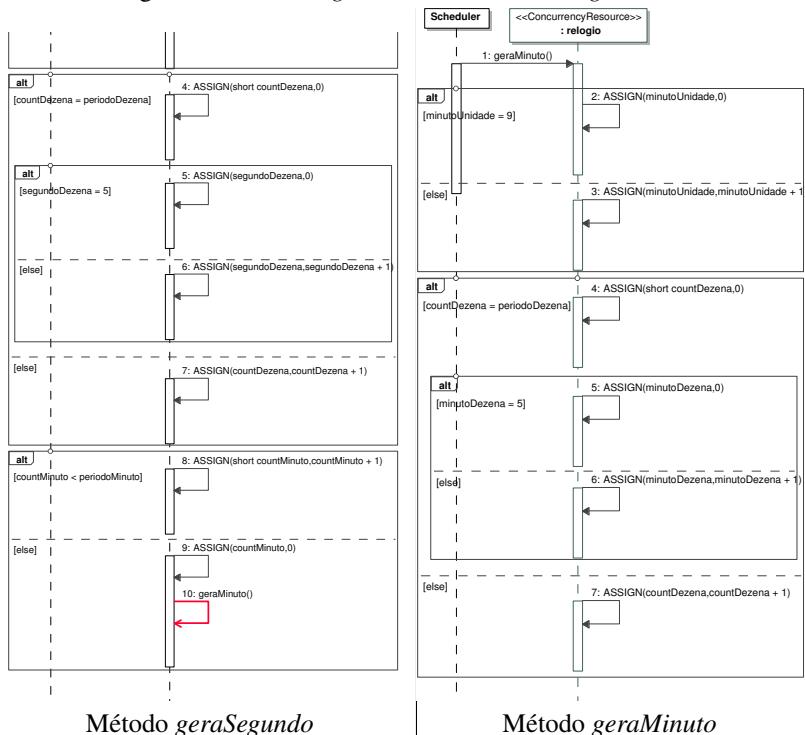

| Figura 17 – Diagrama de sequência para o método <i>refreshDigit</i> da classe <i>systemControl</i> . . . . .                                         | 88  |

| Figura 18 – Classe <i>systemControl</i> . . . . .                                                                                                    | 89  |

| Figura 19 – Definição do Aspecto <i>PeriodicTiming</i> . . . . .                                                                                     | 95  |

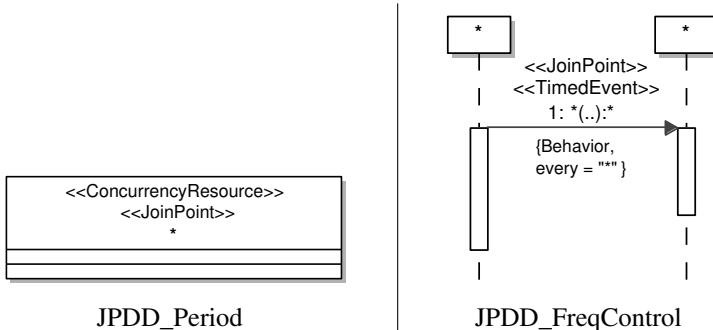

| Figura 20 – Diagramas JPDD para o aspecto <i>PeriodicTiming</i> . . . . .                                                                            | 96  |

| Figura 21 – Definição do aspecto <i>DataFreshness</i> . . . . .                                                                                      | 99  |

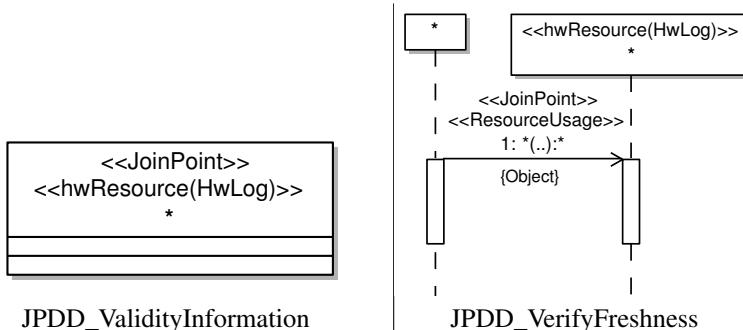

| Figura 22 – Diagramas JPDD para o aspecto <i>DataFreshness</i> . . . . .                                                                             | 100 |

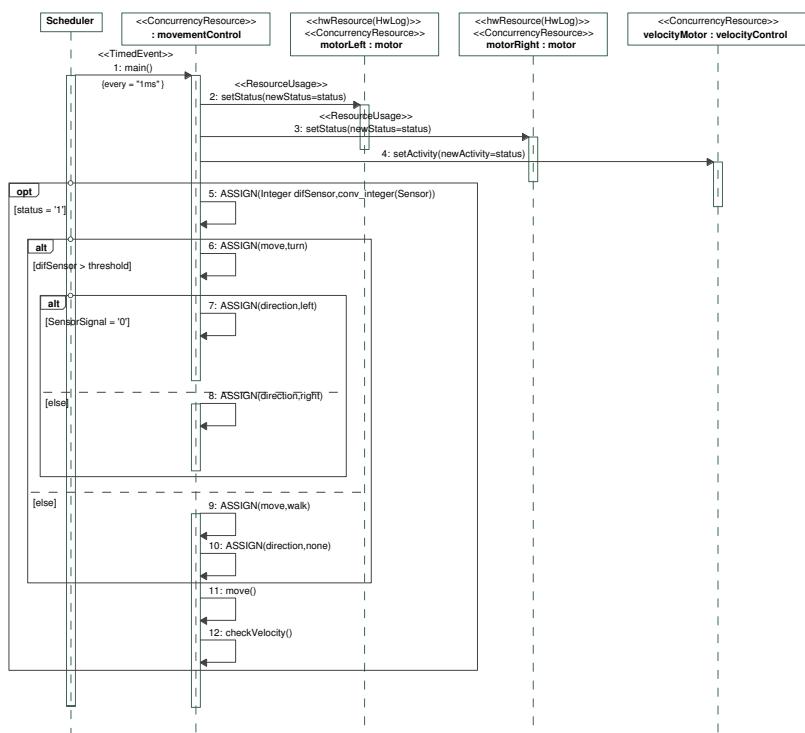

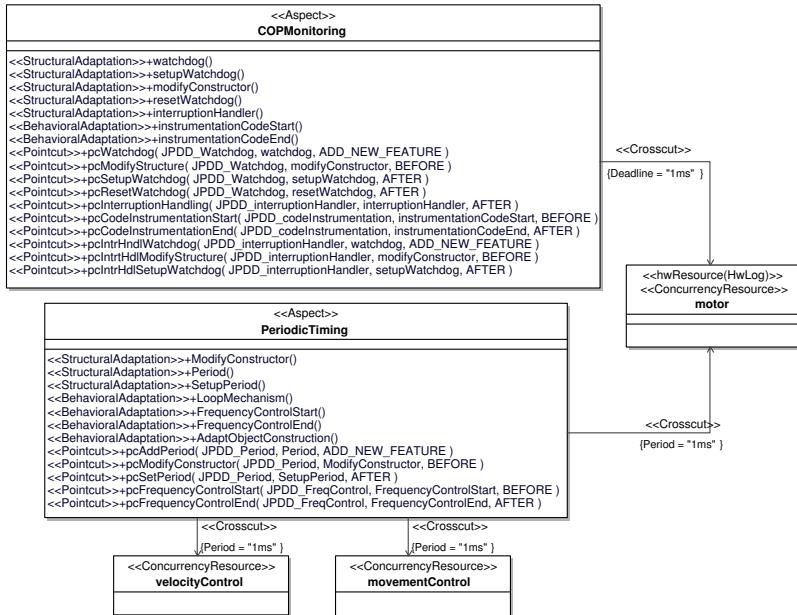

| Figura 23 – Definição do aspecto <i>COPMonitoring</i> . . . . .                                                                                      | 103 |

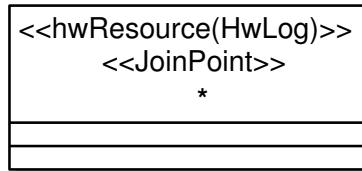

| Figura 24 – Diagrama JPDD <i>JPDD_Watchdog</i> do aspecto <i>COPMonitoring</i> . . . . .                                                             | 103 |

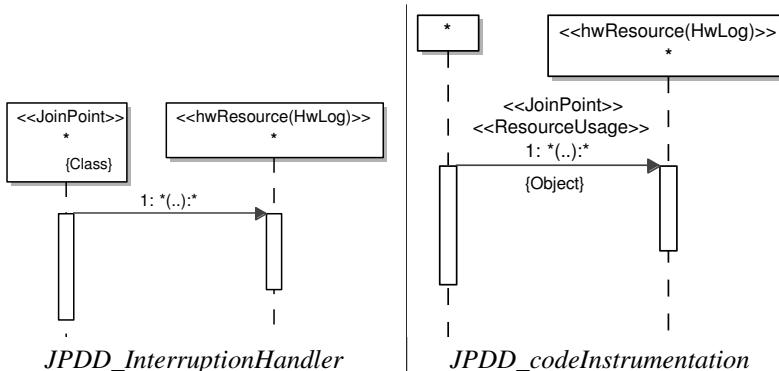

| Figura 25 – Diagramas JPDD para o aspecto <i>COPMonitoring</i> . . . . .                                                                             | 104 |

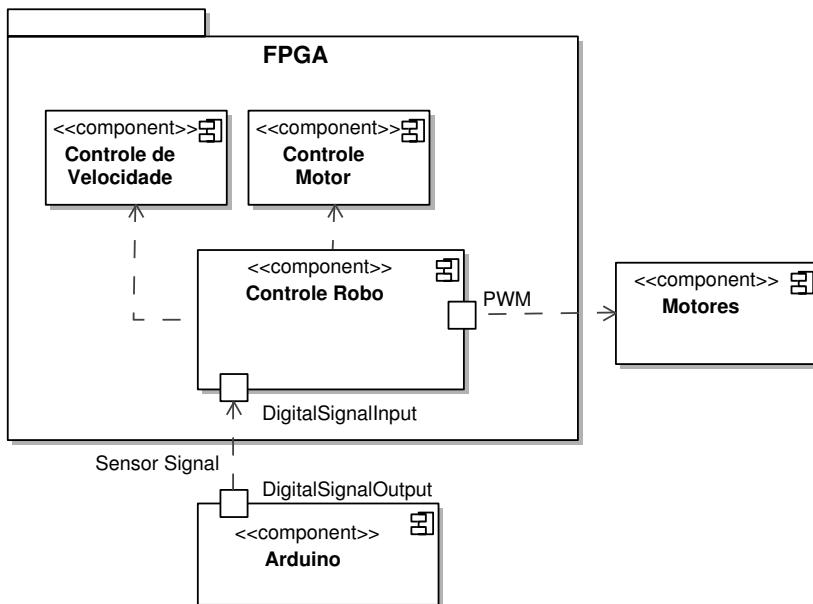

| Figura 26 – Diagrama de componentes do projeto Controle de Robô. . . . .                                                                             | 111 |

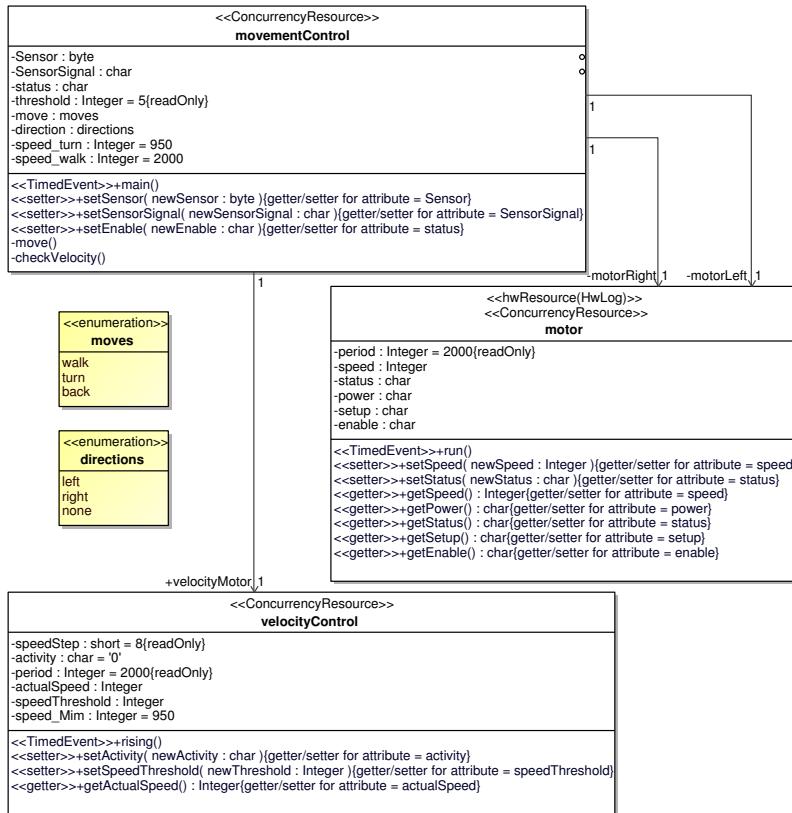

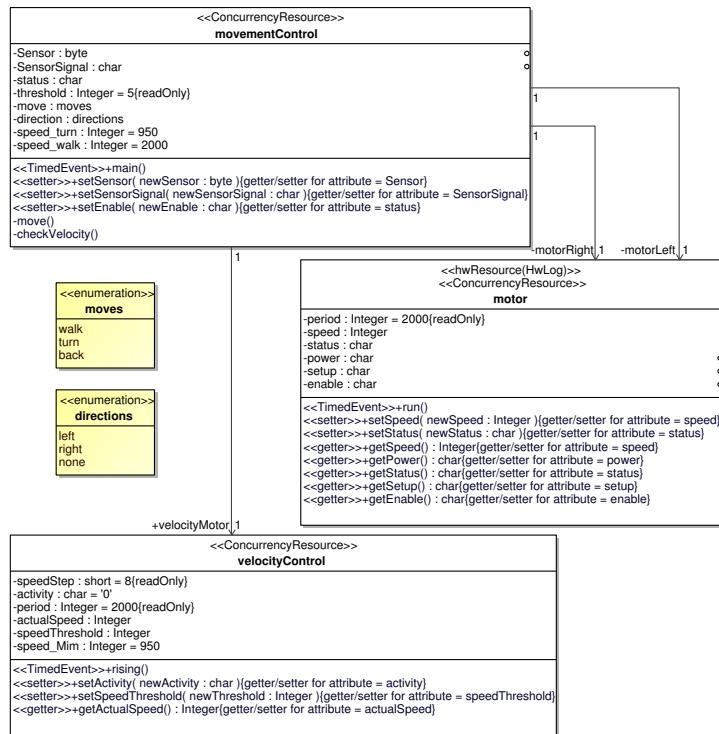

| Figura 27 – Diagrama de classes do Controle de Robô Autônomo. . . . .                                                                                | 112 |

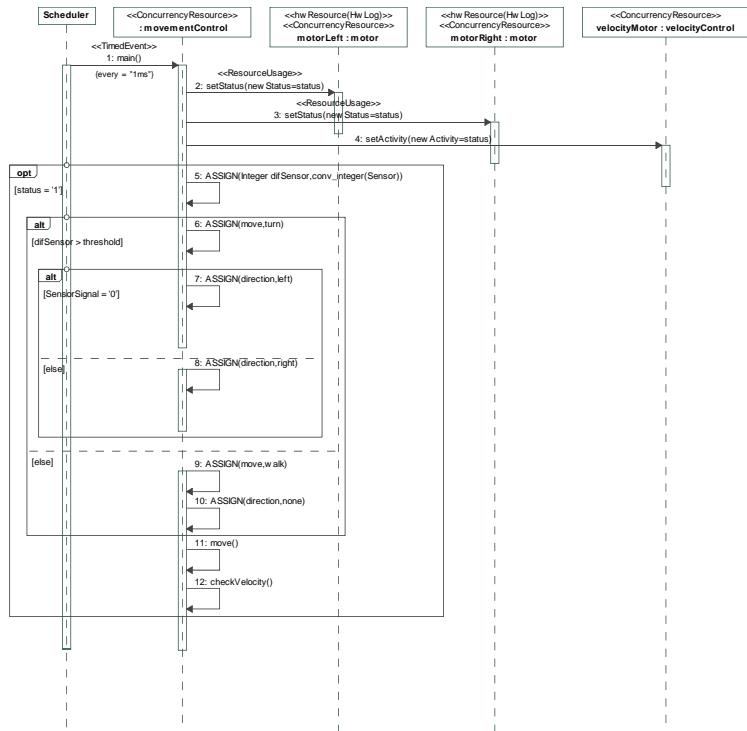

| Figura 28 – Diagrama de sequência do método <i>main</i> da classe <i>movementControl</i> . . . . .                                                   | 113 |

| Figura 29 – Diagrama ACOD do projeto Robô. . . . .                                                                                                   | 115 |

|                                                                                                                      |     |

|----------------------------------------------------------------------------------------------------------------------|-----|

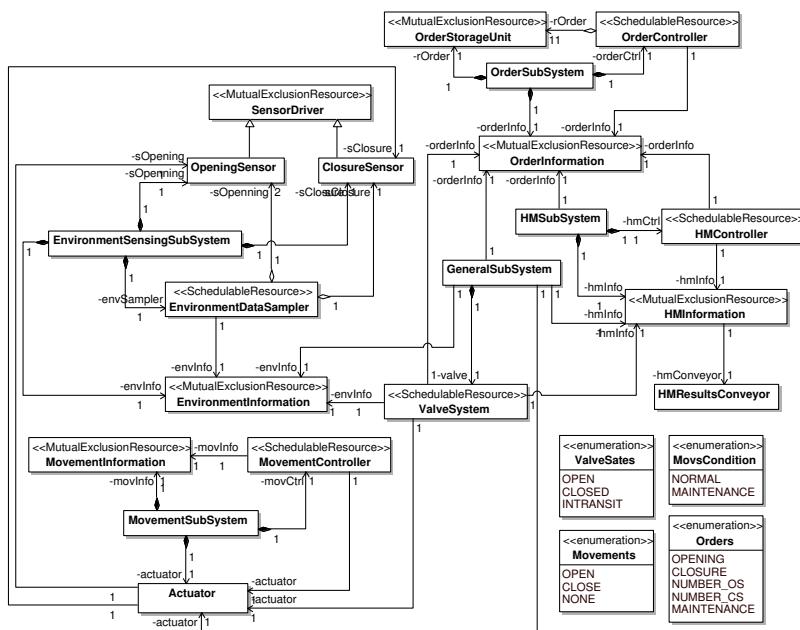

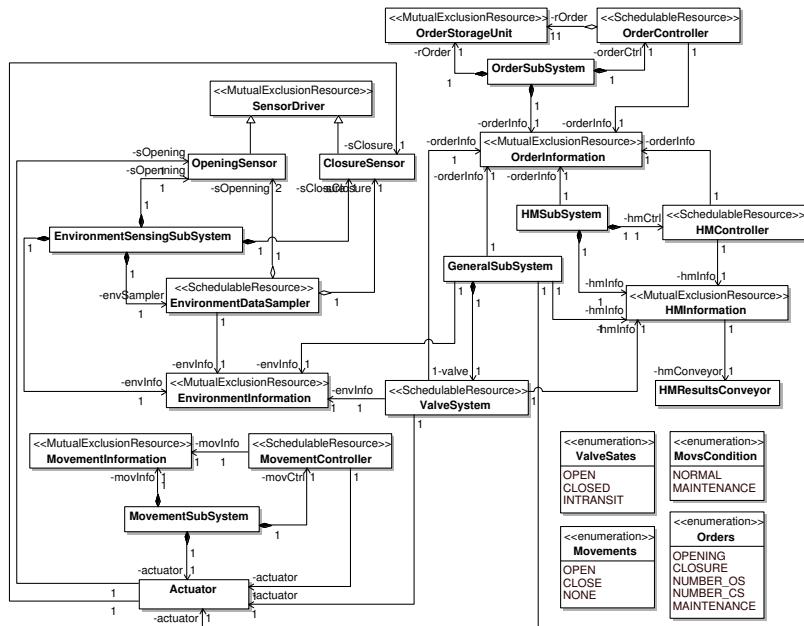

| Figura 30 – Diagrama de classes do Controle de Válvula proposto por Moreira (2012). . . . .                          | 123 |

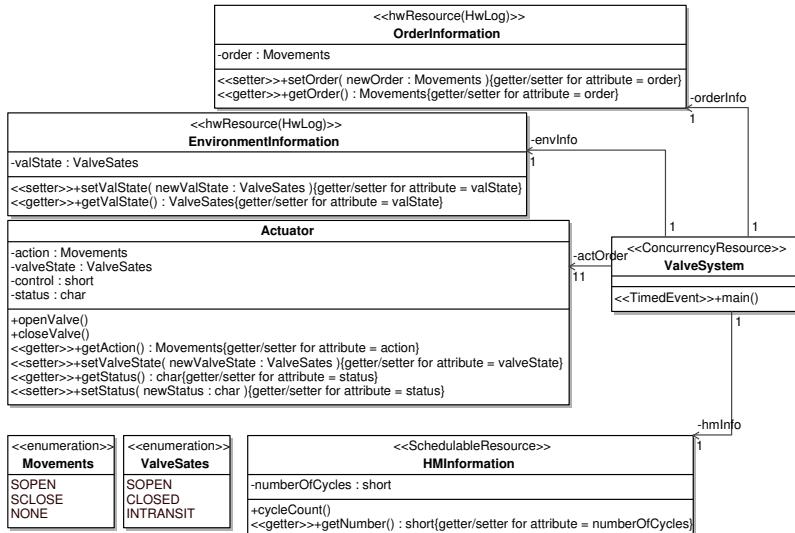

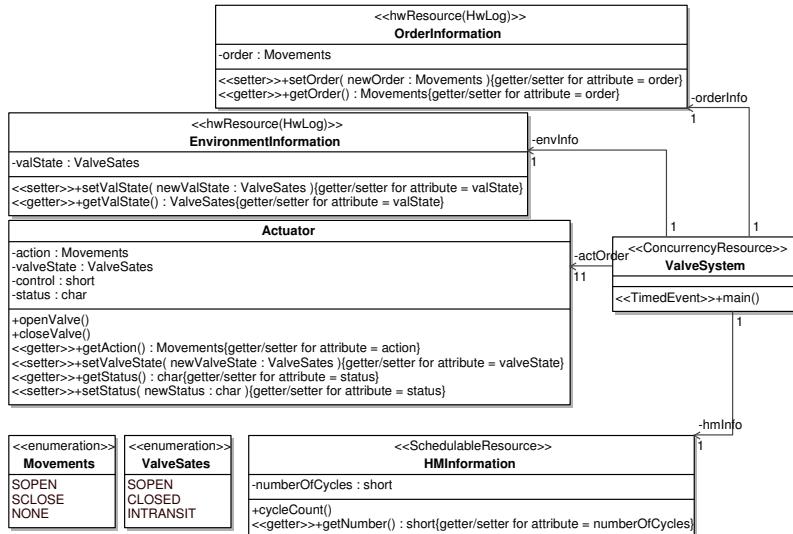

| Figura 31 – Diagrama de classes resumido do Controle de Válvula. . . . .                                             | 124 |

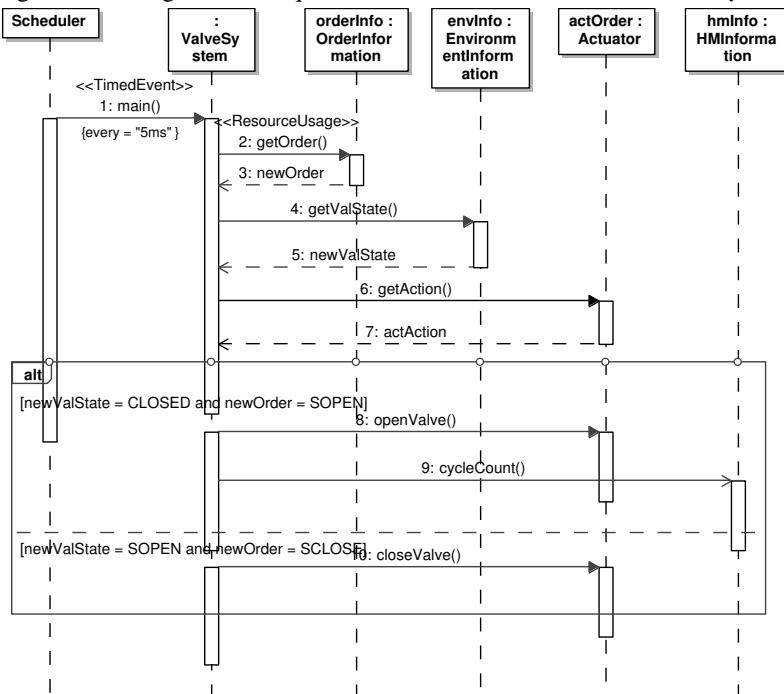

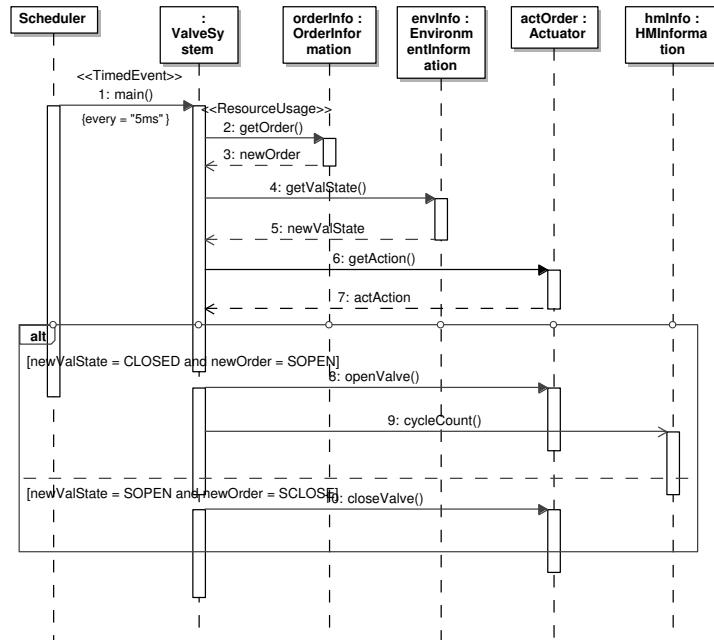

| Figura 32 – Diagrama de sequência do método <i>main</i> da classe <i>ValveSystem</i> . . . . .                       | 125 |

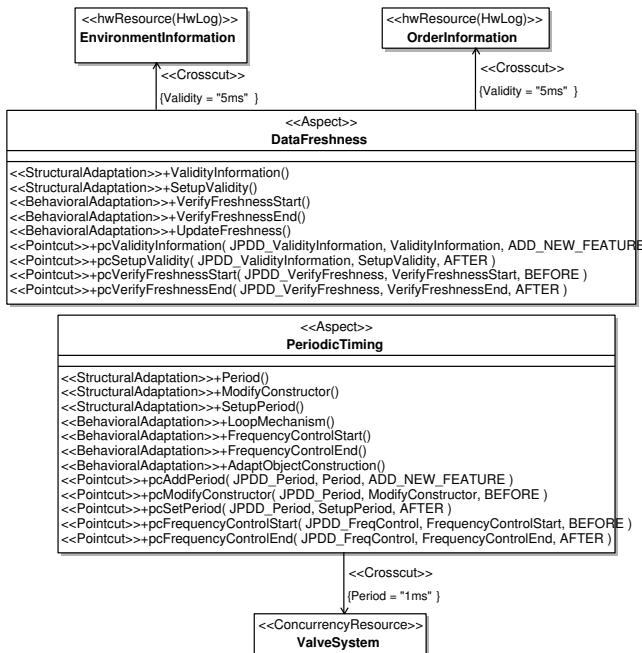

| Figura 33 – Diagrama ACOD do projeto Válvula resumido. . . . .                                                       | 126 |

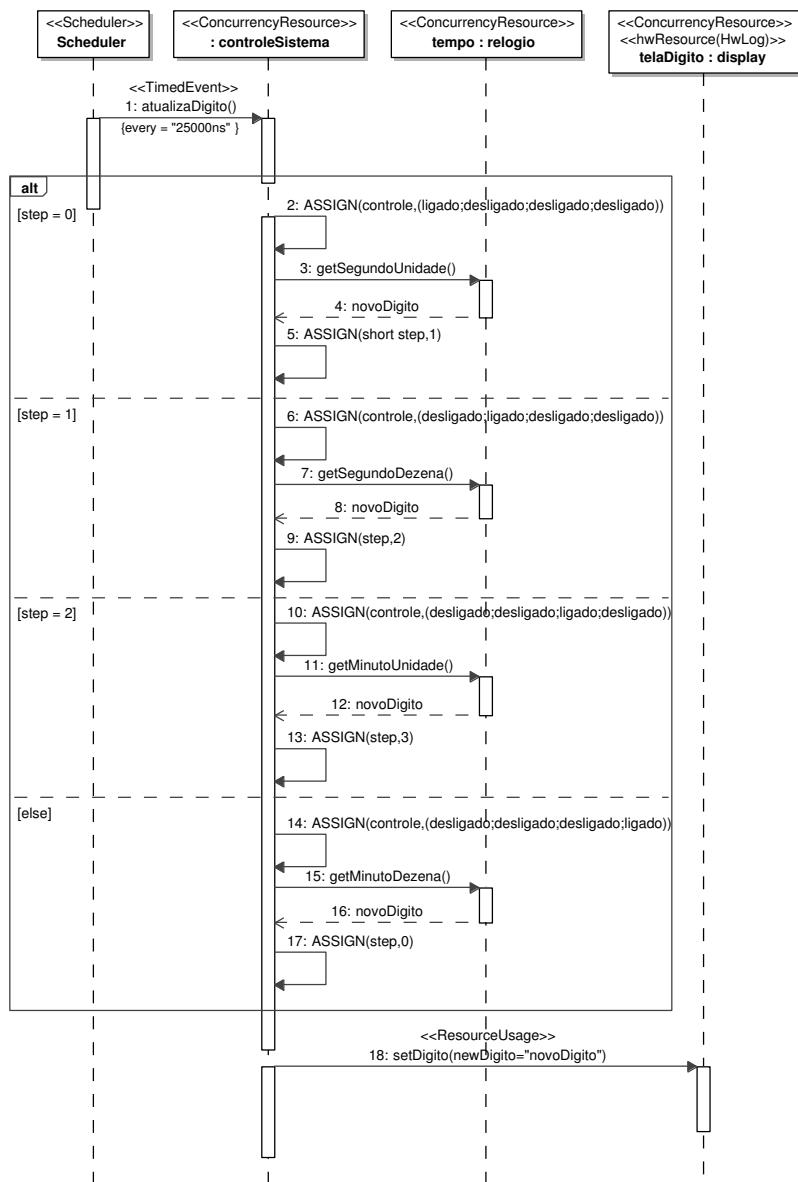

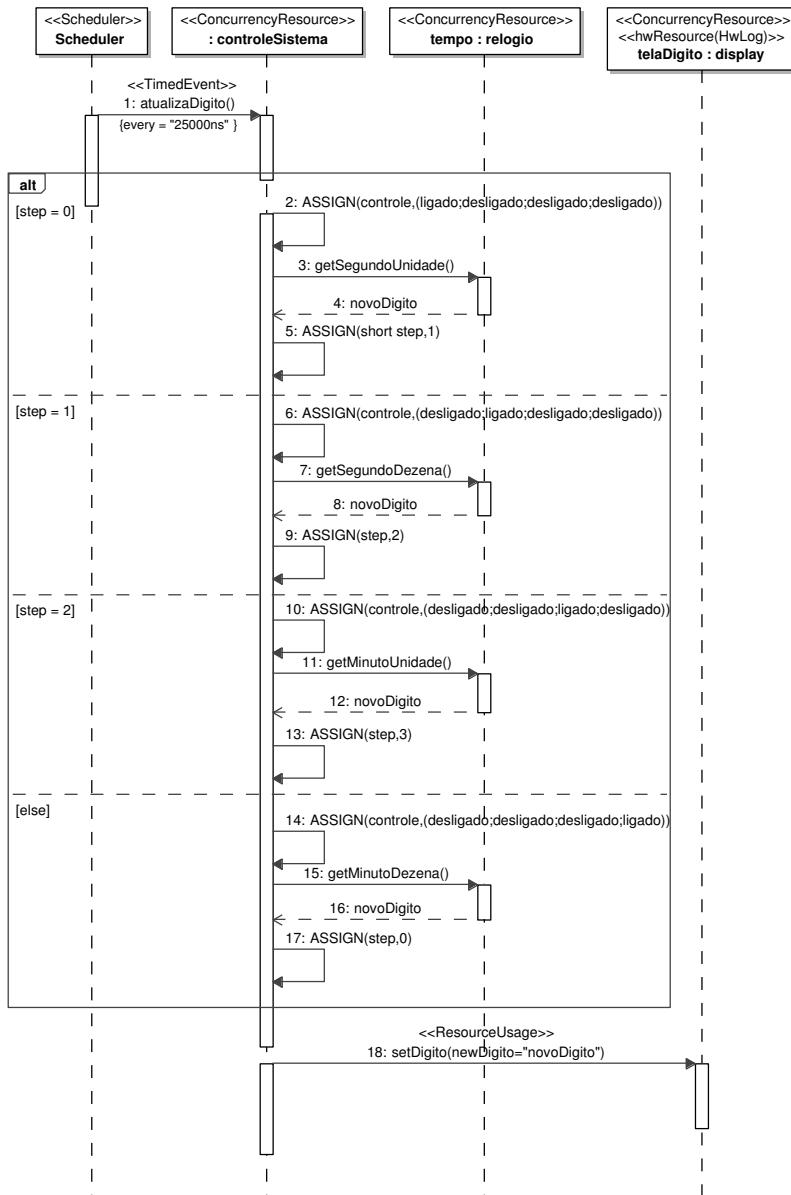

| Figura 34 – Diagrama de sequência do método <i>atualizaDigito</i> da classe <i>controleSistema</i> . . . . .         | 131 |

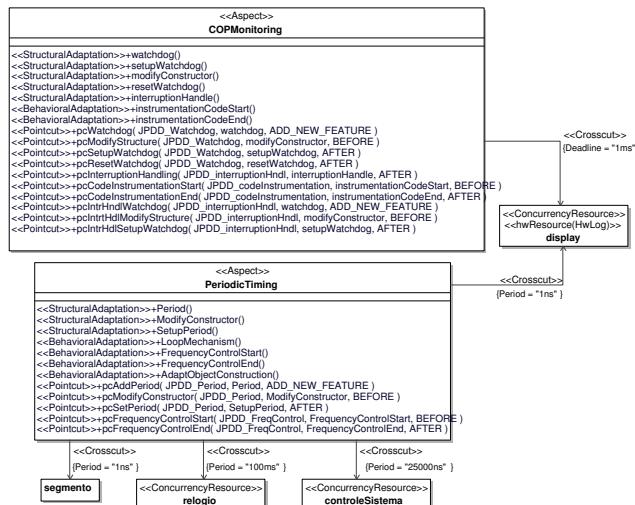

| Figura 35 – Diagrama ACOD do projeto Relógio. . . . .                                                                | 133 |

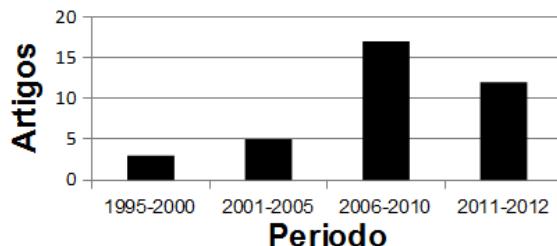

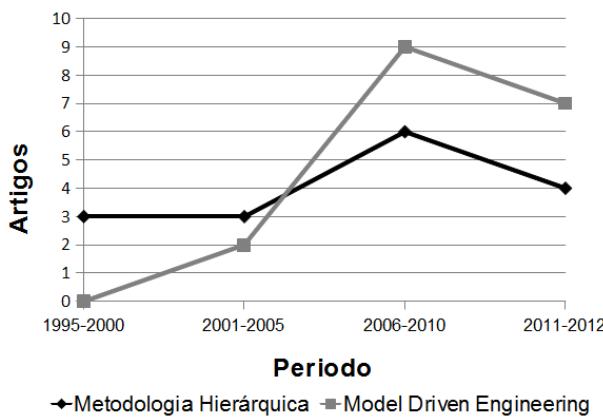

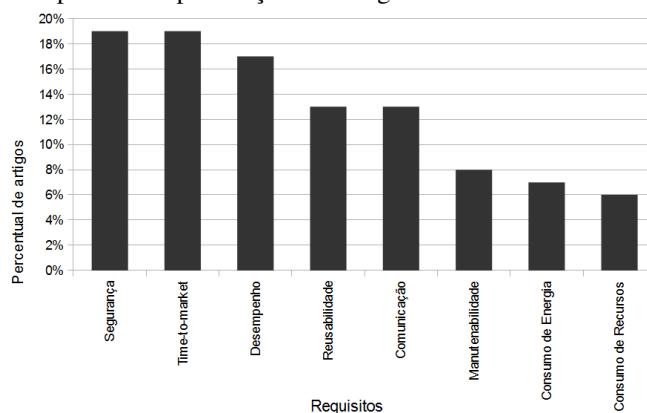

| Figura 36 – Análise do número de artigos. . . . .                                                                    | 159 |

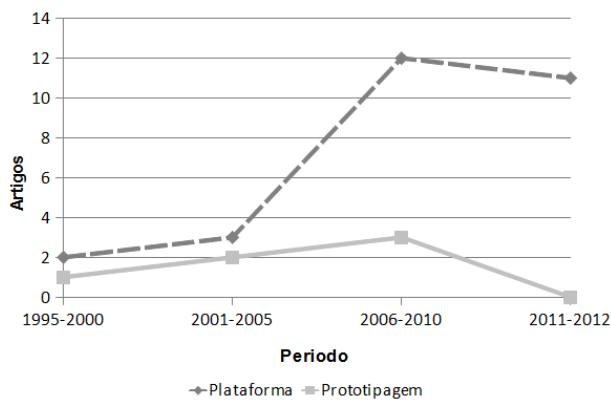

| Figura 37 – Análise da utilização das FPGAs como plataforma. . . . .                                                 | 159 |

| Figura 38 – Análise das abordagens utilizadas em relação ao período de publicação dos artigos. . . . .               | 160 |

| Figura 39 – Análise dos requisitos não funcionais abordados em relação ao período de publicação dos artigos. . . . . | 161 |

| Figura 40 – Diagrama de classes do Controle de Robô Autônomo. . . . .                                                | 163 |

| Figura 41 – Diagrama de sequência do método <i>main</i> da classe <i>movementControl</i> . . . . .                   | 164 |

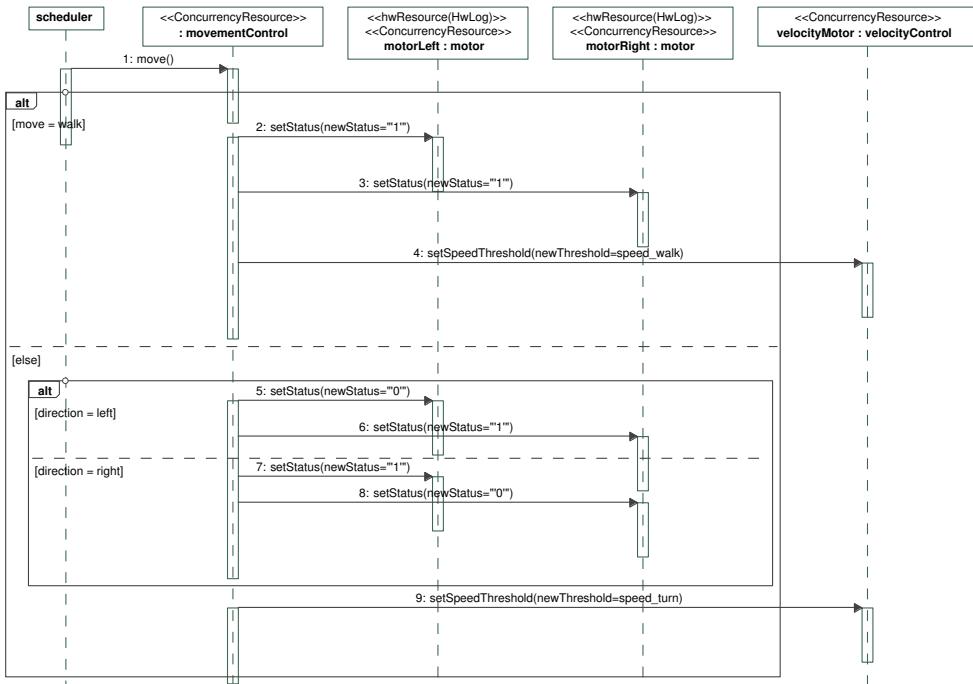

| Figura 42 – Diagrama de sequência do método <i>move</i> da classe <i>movementControl</i> . . . . .                   | 165 |

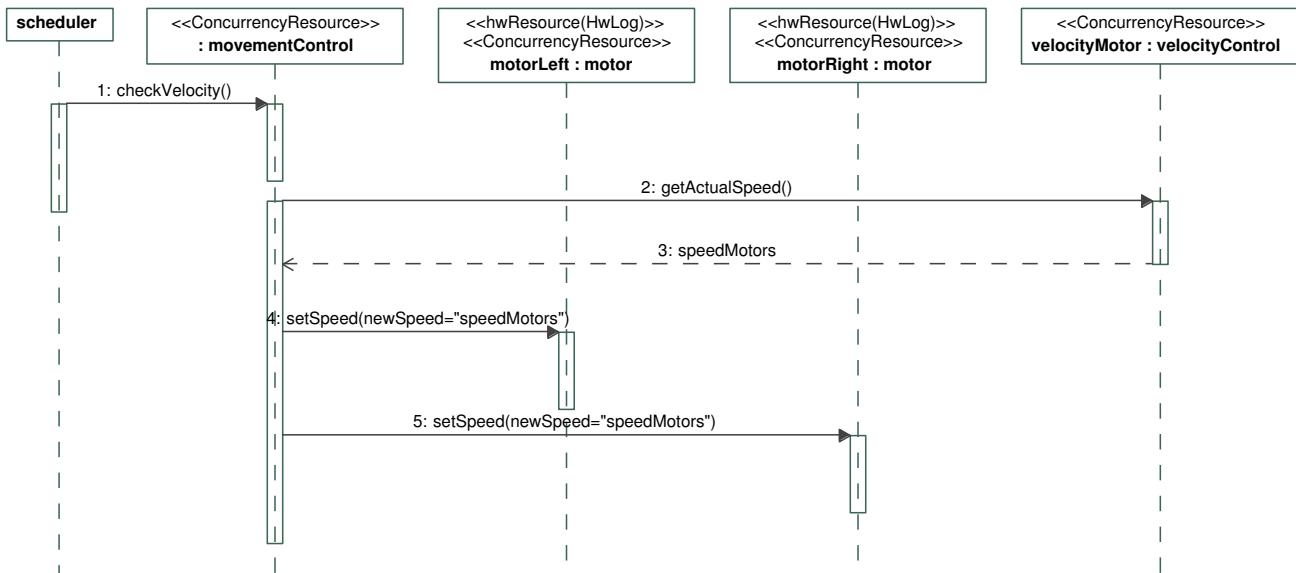

| Figura 43 – Diagrama de sequência do método <i>checkVelocity</i> da classe <i>movementControl</i> . . . . .          | 166 |

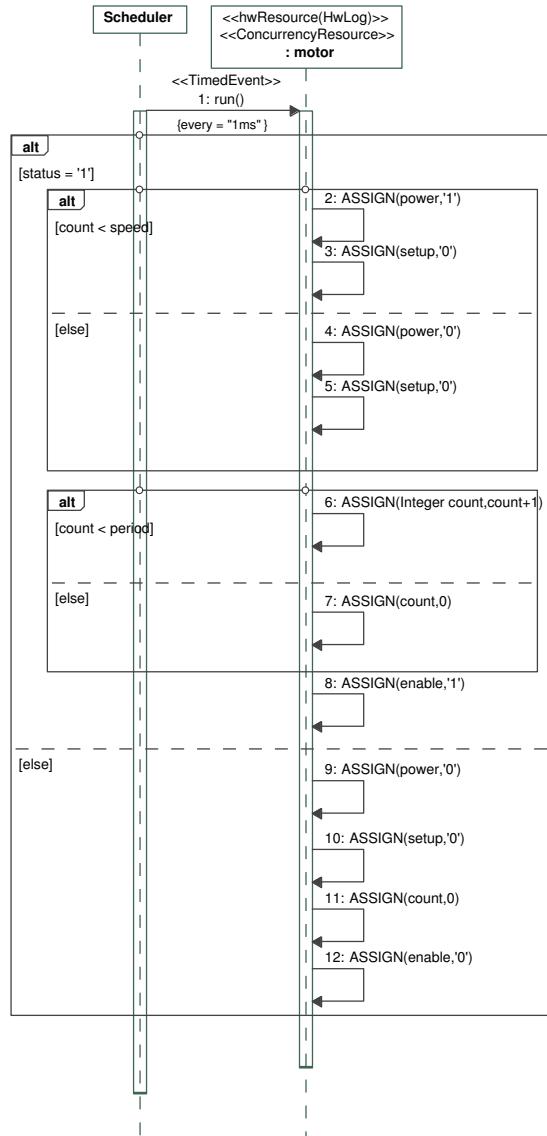

| Figura 44 – Diagrama de sequência do método <i>run</i> da classe <i>motor</i> . . . . .                              | 167 |

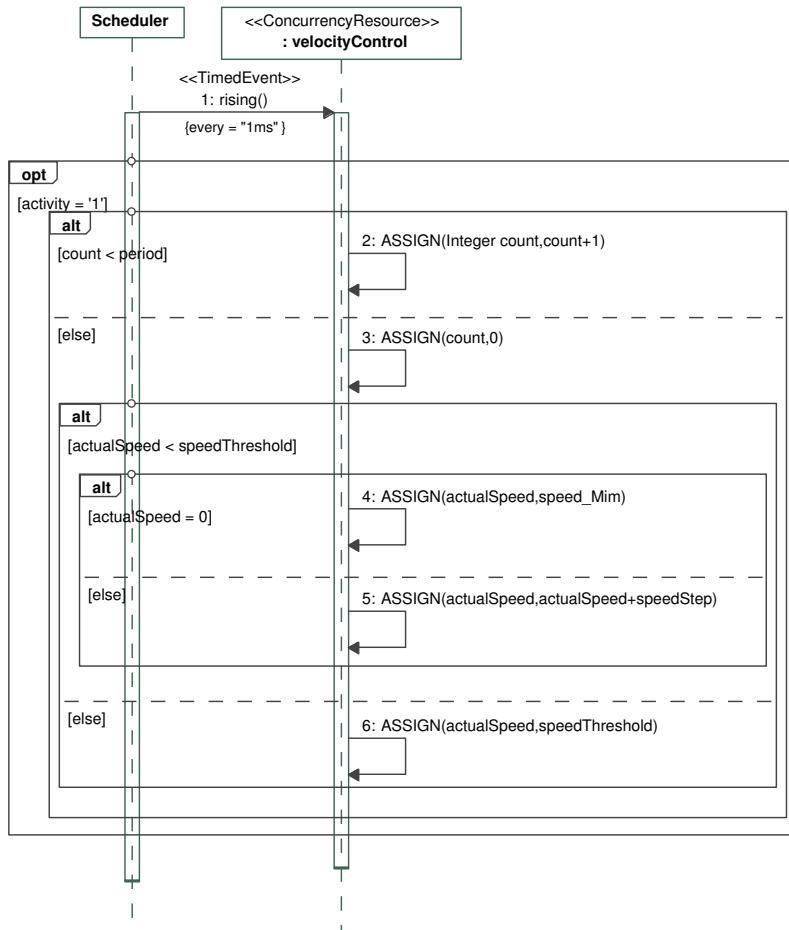

| Figura 45 – Diagrama de sequência do método <i>rising</i> da classe <i>velocityControl</i> . . . . .                 | 168 |

| Figura 46 – Diagrama de classes do Controle de Válvula proposto por Moreira (2012). . . . .                          | 169 |

| Figura 47 – Diagrama de classes resumido do Controle de Válvula. . . . .                                             | 170 |

| Figura 48 – Diagrama de sequência do método <i>main</i> da classe <i>ValveSystem</i> . . . . .                       | 171 |

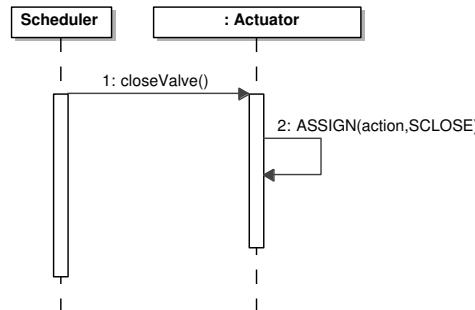

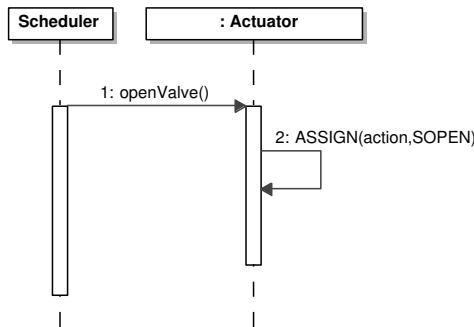

| Figura 49 – Diagrama de sequência do método <i>closeValve</i> da classe <i>Actuator</i> . . . . .                    | 171 |

| Figura 50 – Diagrama de sequência do método <i>openValve</i> da classe <i>Actuator</i> . . . . .                     | 172 |

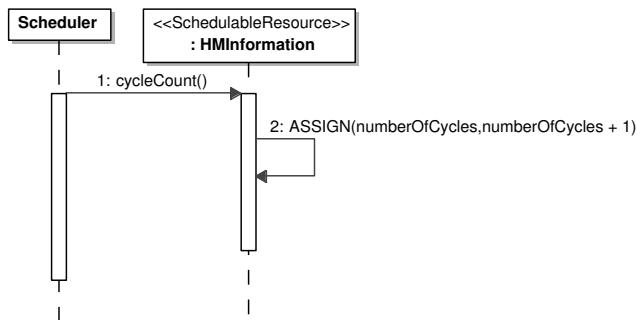

| Figura 51 – Diagrama de sequência do método <i>cycleCount</i> da classe <i>HMIInformation</i> . . . . .              | 172 |

| Figura 52 – Diagrama de classes do projeto Display. . . . .                                                          | 173 |

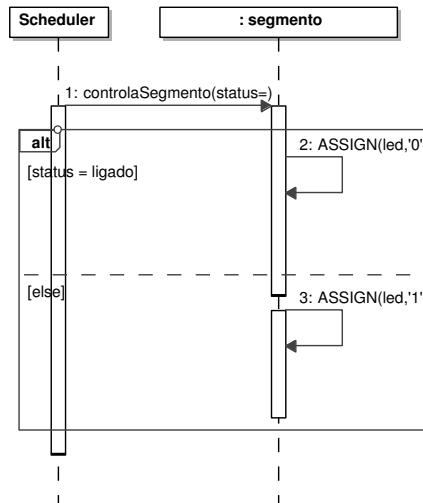

| Figura 53 – Diagrama de sequência do método <i>controlaSegmento</i> da classe <i>Segmento</i> . . . . .              | 173 |

| Figura 54 – Diagrama de sequência do método <i>atualizaDigito</i> da classe <i>controleSistema</i> . . . . .         | 174 |

|                                                                                                           |     |

|-----------------------------------------------------------------------------------------------------------|-----|

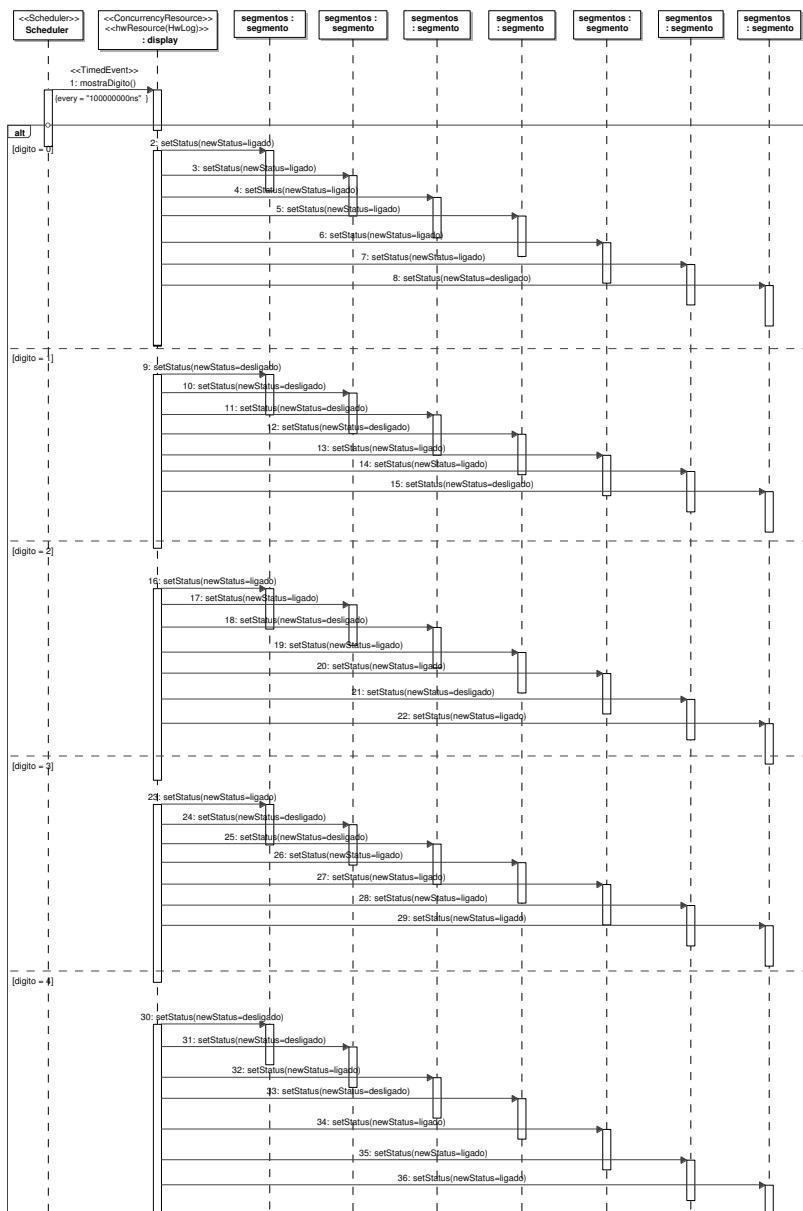

| Figura 55 – Diagrama de sequência do método <i>mostraDigito</i> da classe <i>Display</i> .                | 175 |

| Figura 56 – Continuação do diagrama de sequência do método <i>mostraDigito</i> da classe <i>Display</i> . | 176 |

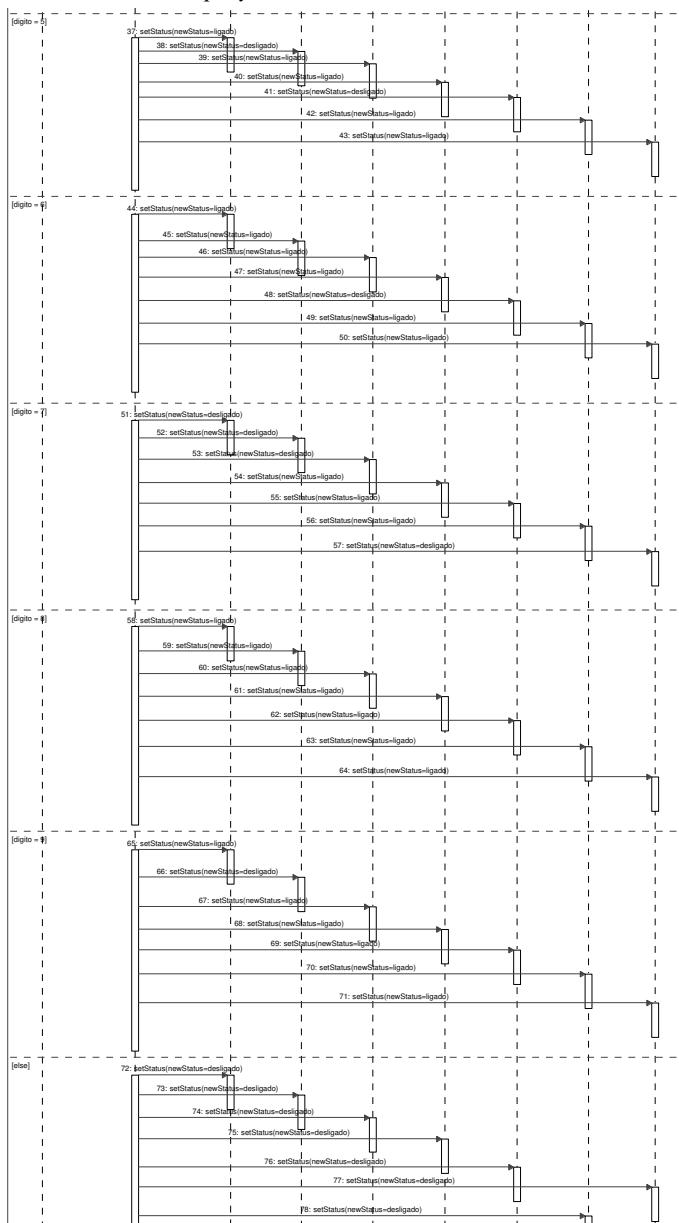

| Figura 57 – Diagrama de sequência do método <i>geraSegundo</i> da classe <i>Relogio</i> .                 | 177 |

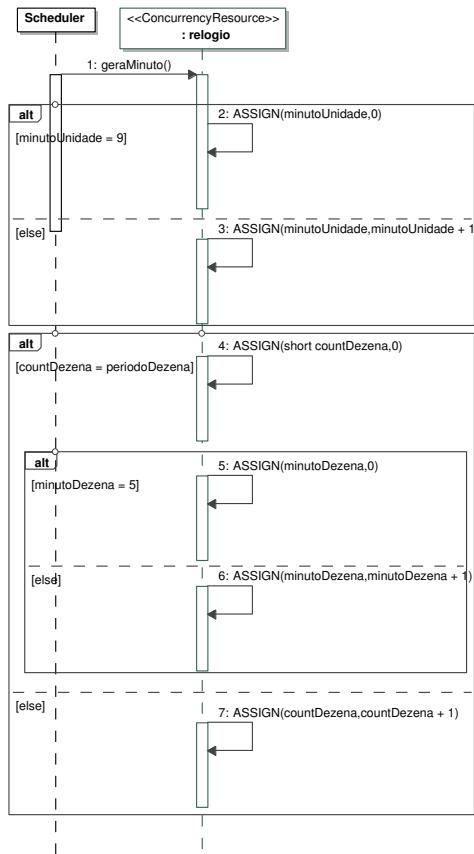

| Figura 58 – Diagrama de sequência do método <i>geraMinuto</i> da classe <i>Relogio</i> .                  | 178 |

## LISTA DE TABELAS

|                                                                                                                         |     |

|-------------------------------------------------------------------------------------------------------------------------|-----|

| Tabela 1 – Conceitos mapeados em Moreira (2012) . . . . .                                                               | 58  |

| Tabela 2 – Métricas dos requisitos não funcionais para projetos de FPGA. . . . .                                        | 69  |

| Tabela 3 – Conceitos mapeados. . . . .                                                                                  | 75  |

| Tabela 4 – Pontos de adaptação para VHDL. . . . .                                                                       | 93  |

| Tabela 5 – Pontos de adaptação para VHDL não abordados. . . . .                                                         | 108 |

| Tabela 6 – Especificação Spartan6 XC6LX16. . . . .                                                                      | 110 |

| Tabela 7 – Análise do tamanho do projeto Controle de Robô Autônomo. . . . .                                             | 118 |

| Tabela 8 – Análise do desempenho do projeto Controle de Robô Autônomo. . . . .                                          | 120 |

| Tabela 9 – Análise do tamanho do projeto Controle de Robô Autônomo. Comparativo da utilização dos aspectos. . . . .     | 121 |

| Tabela 10 – Análise do desempenho do projeto Controle de Robô Autônomo. Comparativo da utilização dos aspectos. . . . . | 121 |

| Tabela 11 – Análise de reusabilidade e impacto dos aspectos do projeto Controle de Robô Autônomo. . . . .               | 122 |

| Tabela 12 – Análise do tamanho do projeto Controle de Válvula. . . . .                                                  | 129 |

| Tabela 13 – Análise do desempenho do projeto Controle de Válvula. . . . .                                               | 129 |

| Tabela 14 – Análise de reusabilidade e impacto dos aspectos do projeto Controle de Válvula. . . . .                     | 129 |

| Tabela 15 – Análise do tamanho do projeto Relógio. . . . .                                                              | 134 |

| Tabela 16 – Análise do desempenho do projeto Relógio. . . . .                                                           | 135 |

| Tabela 17 – Análise de reusabilidade e impacto dos aspectos do projeto Relógio. . . . .                                 | 135 |

| Tabela 18 – Análise de reusabilidade e impacto dos aspectos. . . . .                                                    | 137 |

| Tabela 19 – Análise do esforço de modelagem. . . . .                                                                    | 137 |

| Tabela 20 – Critérios de seleção e priorização dos artigos . . . . .                                                    | 155 |

| Tabela 21 – Artigos selecionados para a pesquisa bibliográfica . . . . .                                                | 156 |

| Tabela 22 – Artigos incluídos e excluídos na pesquisa . . . . .                                                         | 157 |

| Tabela 23 – Comparação da priorização dos artigos inicial e após a análise . . . . .                                    | 158 |

## **LISTA DE ABREVIATURAS E SIGLAS**

|           |                                                                |

|-----------|----------------------------------------------------------------|

| AB        | Aspectual Bloat                                                |

| ACOD      | Aspects Crosscutting Overview Diagram                          |

| ADH       | Aspect Described Hardware-Description-Language                 |

| ADL       | Architecture Description Languages                             |

| AMoDE-RT  | Aspect-oriented Model-Driven Engineering for Real-Time systems |

| ANOffM    | Access Number Off-Chip Memory                                  |

| ANOnM     | Access Number On-Chip Memory                                   |

| AOP       | Aspect-Oriented Programming                                    |

| AOSD      | Aspect-Oriented Software Development                           |

| ASIP      | Application-Specific Instruction-Set Processors                |

| CDLOC     | Concern Diffusion over Lines of Code                           |

| CI        | Circuitos Integrados                                           |

| CPT       | Critical Path Time                                             |

| DERAF     | Distributed Embedded Real-time Aspects Framework               |

| DERCS     | Distributed Embedded Real-time Compact Specification           |

| ECF       | Energy Consumption/Functionality                               |

| FF        | Flip-Flop                                                      |

| FPGA      | Field-Programmable Gate Array                                  |

| FR        | Fault Rate                                                     |

| FRIDA     | From RequIrements to Design using Aspects                      |

| GenERTiCA | Generation of Embedded Real-Time Code based on Aspects         |

| HDL       | Hardware Description Language                                  |

| HRM       | Hardware Resource Modeling                                     |

| IEEE      | Institute of Electrical and Electronics Engineers              |

| IOBs      | Input/Output Blocks                                            |

| JPDD      | Join Point Designation Diagrams                                |

| LOC       | Lines of Code                                                  |

| LOAC      | Lines of Adaptation Code                                       |

|       |                                                         |

|-------|---------------------------------------------------------|

| LOWC  | Lines of Woven Code                                     |

| LUT   | Look-Up Table                                           |

| MARTE | Modeling and Analysis of Real-Time and Embedded systems |

| MDE   | Model Driven Engineering                                |

| MF    | Maximum Frequency                                       |

| MS    | Memory Size                                             |

| NoC   | Network on Chip                                         |

| NPU   | Number of Processing Units                              |

| OS    | Occupied Slices                                         |

| PIM   | Platform Independet Model                               |

| POO   | Programação Orientada a Objetos                         |

| PSM   | Platform Specific Model                                 |

| PWM   | Pulse Width Modulation                                  |

| SoC   | System-on-Chip                                          |

| RF    | Risk Factor                                             |

| RSM   | Repetitive Structure Modeling                           |

| TR    | Tangling Ratio                                          |

| UML   | Unified Model Language                                  |

| VHDL  | Very high speed integrated circuit HDL                  |

| VSL   | Value Specification Language                            |

| WCD   | Worst Case Delay                                        |

| WCET  | Worst Case Execution Time                               |

| WS    | Word Size                                               |

| XML   | eXtensible Markup Language                              |

## SUMÁRIO

|          |                                                                                  |           |

|----------|----------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>INTRODUÇÃO</b>                                                                | <b>23</b> |

| 1.1      | CONTEXTUALIZAÇÃO DO TRABALHO                                                     | 24        |

| 1.2      | OBJETIVOS E ESCOPO DO TRABALHO                                                   | 27        |

| 1.3      | CONTRIBUIÇÕES DO TRABALHO                                                        | 28        |

| 1.4      | ORGANIZAÇÃO DO TEXTO                                                             | 28        |

| <b>2</b> | <b>FUNDAMENTAÇÃO TEÓRICA</b>                                                     | <b>31</b> |

| 2.1      | SISTEMAS EMBARCADOS                                                              | 31        |

| 2.2      | SISTEMAS DE TEMPO-REAL                                                           | 32        |

| 2.3      | FIELD-PROGRAMMABLE GATE ARRAY                                                    | 33        |

| 2.4      | VHDL                                                                             | 35        |

| 2.5      | REQUISITOS NÃO-FUNCIONAIS                                                        | 37        |

| 2.6      | ORIENTAÇÃO A ASPECTOS                                                            | 39        |

| 2.7      | A METODOLOGIA AMoDE-RT                                                           | 43        |

| <b>3</b> | <b>REVISÃO DA LITERATURA</b>                                                     | <b>49</b> |

| 3.1      | TRATAMENTO DE REQUISITOS NÃO-FUNCIONAIS                                          | 49        |

| 3.2      | METODOLOGIAS DE DESENVOLVIMENTO                                                  | 52        |

| 3.3      | PROGRAMAÇÃO ORIENTADA A ASPECTOS EM SISTEMAS EMBARCADOS                          | 55        |

| 3.4      | TRABALHOS BASE                                                                   | 58        |

| 3.5      | DISCUSSÃO                                                                        | 59        |

| <b>4</b> | <b>DESENVOLVIMENTO</b>                                                           | <b>63</b> |

| 4.1      | ANÁLISE E AVALIAÇÃO DOS REQUISITOS NÃO-FUNCIONAIS PARA PROJETOS BASEADOS EM FPGA | 63        |

| 4.1.1    | <b>Escalabilidade</b>                                                            | 64        |

| 4.1.2    | <b>Reusabilidade</b>                                                             | 65        |

| 4.1.3    | <b>Consumo de Energia</b>                                                        | 65        |

| 4.1.4    | <b>Área Ocupada</b>                                                              | 66        |

| 4.1.5    | <b>Segurança</b>                                                                 | 67        |

| 4.1.6    | <b>Desempenho</b>                                                                | 67        |

| 4.1.7    | <b>Atraso</b>                                                                    | 68        |

| 4.1.8    | <b>Prazos</b>                                                                    | 68        |

| 4.2      | MÉTRICAS DE AVALIAÇÃO                                                            | 68        |

| 4.3      | GERAÇÃO AUTOMÁTICA DO CÓDIGO VHDL                                                | 73        |

| 4.3.1    | <b>Regras de Mapeamento para Requisitos Funcionais</b>                           | 73        |

| 4.3.1.1  | <b>Atributos</b>                                                                 | 74        |

| 4.3.1.2  | <b>Associações</b>                                                               | 79        |

|                |                                                                     |            |

|----------------|---------------------------------------------------------------------|------------|

| <b>4.3.1.3</b> | <b>Herança . . . . .</b>                                            | <b>80</b>  |

| <b>4.3.1.4</b> | <b>Métodos Assíncronos . . . . .</b>                                | <b>84</b>  |

| <b>4.3.1.5</b> | <b>Métodos Síncronos . . . . .</b>                                  | <b>86</b>  |

| <b>4.3.1.6</b> | <b>Métodos anotados com o estereótipo TimedEvent . . . . .</b>      | <b>88</b>  |

| <b>4.3.1.7</b> | <b>Discussão . . . . .</b>                                          | <b>89</b>  |

| <b>4.3.2</b>   | <b>Regras de Mapeamento para RNF . . . . .</b>                      | <b>90</b>  |

| <b>4.3.2.1</b> | <b>Pointcuts . . . . .</b>                                          | <b>92</b>  |

| <b>4.3.2.2</b> | <b>Aspectos DERAF . . . . .</b>                                     | <b>94</b>  |

| <b>4.3.2.3</b> | <b>Discussão . . . . .</b>                                          | <b>107</b> |

| <b>5</b>       | <b>VALIDAÇÃO EXPERIMENTAL . . . . .</b>                             | <b>109</b> |

| <b>5.1</b>     | <b>INTRODUÇÃO . . . . .</b>                                         | <b>109</b> |

| <b>5.2</b>     | <b>CONTROLE DE ROBÔ AUTÔNOMO . . . . .</b>                          | <b>110</b> |

| <b>5.2.1</b>   | <b>Aplicação dos Aspectos . . . . .</b>                             | <b>114</b> |

| <b>5.2.2</b>   | <b>Análise dos Resultados . . . . .</b>                             | <b>118</b> |

| <b>5.3</b>     | <b>CONTROLE AUTOMÁTICO DE VÁLVULA . . . . .</b>                     | <b>122</b> |

| <b>5.3.1</b>   | <b>Aplicação dos Aspectos . . . . .</b>                             | <b>126</b> |

| <b>5.3.2</b>   | <b>Análise dos Resultados . . . . .</b>                             | <b>128</b> |

| <b>5.4</b>     | <b>RELÓGIO . . . . .</b>                                            | <b>129</b> |

| <b>5.4.1</b>   | <b>Aplicação dos Aspectos . . . . .</b>                             | <b>132</b> |

| <b>5.4.2</b>   | <b>Análise dos Resultados . . . . .</b>                             | <b>134</b> |

| <b>5.5</b>     | <b>DISCUSSÃO . . . . .</b>                                          | <b>135</b> |

| <b>6</b>       | <b>CONCLUSÕES E TRABALHOS FUTUROS . . . . .</b>                     | <b>139</b> |

| <b>6.1</b>     | <b>CONCLUSÕES . . . . .</b>                                         | <b>139</b> |

| <b>6.2</b>     | <b>TRABALHOS FUTUROS . . . . .</b>                                  | <b>141</b> |

|                | <b>Referências . . . . .</b>                                        | <b>143</b> |

|                | <b>Apêndices</b>                                                    | <b>151</b> |

|                | <b>APÊNDICE A – Metodologia da Pesquisa Bibliográfica . . . . .</b> | <b>153</b> |

| <b>A.1</b>     | <b>FRASE DE BUSCA E PESQUISA . . . . .</b>                          | <b>153</b> |

| <b>A.2</b>     | <b>CATALOGAÇÃO E PRIORIZAÇÃO DE LEITURA . . . . .</b>               | <b>154</b> |

| <b>A.3</b>     | <b>DISCUSSÃO . . . . .</b>                                          | <b>156</b> |

|                | <b>APÊNDICE B – Diagramas dos Estudos de Caso</b>                   | <b>163</b> |

| <b>B.1</b>     | <b>CONTROLE DE ROBÔ AUTÔNOMO . . . . .</b>                          | <b>163</b> |

| <b>B.2</b>     | <b>CONTROLE AUTOMÁTICO DE VÁLVULA . . . . .</b>                     | <b>169</b> |

| <b>B.3</b>     | <b>RELÓGIO . . . . .</b>                                            | <b>170</b> |

## 1 INTRODUÇÃO

A computação está cada vez mais presente em nosso cotidiano como, por exemplo, em dispositivos eletrônicos, eletrodomésticos, veículos ou automação predial, entre outros. Esses dispositivos, constituídos por hardware e software, são desenvolvidos para um conjunto restrito de funções e, em geral, estão embutidos em algum equipamento ou sistema maior, sendo denominados sistemas embarcados (WOLF, 2008). A *engenharia de sistemas* trata do processo de desenvolvimento dos sistemas embarcados, envolvendo o hardware e software (SOMMERVILLE, 2007). A complexidade do processo de desenvolvimento desses sistemas tem aumentado devido ao aumento da complexidade das funcionalidades e do tamanho das aplicações fornecidas. Por essa razão, a *engenharia de software* vem emprestando vários conceitos e abstrações tais como diagramas de comportamento e estrutura de objetos, para lidar com esses desafios e agilizar o processo de desenvolvimento.

Sistemas embarcados são compostos por microprocessadores complexos denominados *System-on-Chip* (SoC)<sup>1</sup>, que requerem dos desenvolvedores muito mais conhecimentos e habilidades do que a programação de softwares convencionais. É necessário conhecer o hardware em detalhe, ter o domínio dos componentes da plataforma e do tratamento dos requisitos do projeto que será desenvolvido para obter o melhor desempenho a um baixo custo. Um exemplo são os dispositivos *Field-Programmable Gate Array* (FPGA) onde é o desenvolvedor que implementa a arquitetura e comportamento do hardware, e não apenas a codificação de um software.

Os sistemas embarcados estão sujeitos a rígidas restrições devido às suas características de tempo-real, consumo de energia e tamanho. Tais requisitos impactam fortemente no projeto desses sistemas. Esses requisitos se referem aos aspectos arquiteturais, de qualidade de projeto e ao comportamento do sistema. Há uma crescente necessidade no tratamento dos requisitos do projeto, principalmente os relacionados aos recursos de hardware e restrições temporais, devido a grande utilização dos sistemas embarcados em aplicações de tempo-real (MONMASSON; CIRSTEIA, 2007; SALEWSKI; TAYLOR, 2008).

O gerenciamento dos requisitos não funcionais é outro fator que diferencia o desenvolvimento de sistemas embarcados dos sistemas convencionais. Para gerenciar é necessário medir os indicadores do atendimento dos requisitos não funcionais. Para isso é importante a definição de métricas e sua aplicação. Assim, outro ramo de pesquisa é a validação dos requisitos não funcionais do projeto com o uso de métricas no processo de desenvolvimento (REDIN et al., 2008; CORREA et al., 2010).

---

<sup>1</sup> Sistemas embarcados desenvolvidos dentro de um único chip.

Nesse contexto, pesquisadores em engenharia de software vem desenvolvendo várias ferramentas e metodologias de suporte ao desenvolvimento de sistemas embarcados. Uma de suas vertentes é a automatização do processo de desenvolvimento com o uso da engenharia guiada por modelos, do inglês *Model Driven Engineering* (MDE) (WEHRMEISTER, 2009). A abordagem MDE propõe o desenvolvimento de projetos a partir da transformação de modelos e geração automática de código (SELIC, 2003). Nesta, o principal artefato é o modelo, que pode ser, por exemplo, descrito por meio de uma especificação UML, do inglês *Unified Modeling Language*, assim como outros modelos utilizados de acordo com o domínio da aplicação.

Metodologias para o tratamento e gerenciamento dos requisitos não funcionais em sistemas embarcados também vem surgindo. Abordagens de desenvolvimento orientado a objetos e a aspectos vem sendo propostas como solução para esse problema. O desenvolvimento orientado a aspectos já é comum no desenvolvimento de software devido aos benefícios que traz ao projeto como manutenibilidade e reutilização de código (RASHID et al., 2010). A orientação a aspectos agora é proposta para o desenvolvimento de sistemas embarcados (WEHRMEISTER; PEREIRA; RAMMIG, 2013).

Esta dissertação explora os desafios de desenvolvimento de sistemas embarcados de tempo-real, buscando uma solução para o tratamento e gerenciamento dos requisitos não funcionais. Nesta dissertação é apresentada uma metodologia que possibilita a especificação em alto-nível dos requisitos não funcionais e a automatização do processo de codificação desses sistemas.

## 1.1 CONTEXTUALIZAÇÃO DO TRABALHO

O desenvolvimento de sistemas embarcados, simples ou complexos, está cada vez mais ágil, requerendo plataformas eficientes e automatizadas para reduzir o tempo de projeto e seu custo (SHIMIZU et al., 2004). Além disso, a busca por componentes de hardware mais baratos e adaptáveis tem motivado a utilização de FPGAs. O aperfeiçoamento de circuitos FPGA os torna uma opção interessante de hardware para sistemas embarcados complexos por serem flexíveis e possuírem custo/benefício economicamente atraente (MONMASSON; CIRSTEAD, 2007; SALEWSKI; TAYLOR, 2008).

Muitos pesquisadores avaliaram a utilização das FPGAs na indústria e verificaram seu potencial para a aplicação em sistemas embarcados (MONMASSON; CIRSTEAD, 2007; SALEWSKI; TAYLOR, 2008; TAHOORI et al., 2009). Entretanto, aqueles pesquisadores observaram o avanço do hardware em contrapartida a defasagem das ferramentas de desenvolvimento e técnicas para o uso desta tecnologia. De fato, a limitação das ferramentas para o desenvolvimento de sistemas implementados em FPGAs tem dificultado sua

adoção pela indústria (MONMASSON et al., 2011). Além disso, as FPGAs possuem características especiais em relação às demais plataformas de sistemas embarcados. Um exemplo é a descrição textual especificada em Linguagem de Descrição de Hardware (*Hardware Description Language - HDL*), que, para as FPGAs, define a arquitetura e comportamento do hardware e não apenas um conjunto de instruções que será executado por um processador tradicional.

Alguns autores sugerem introduzir níveis de abstração mais altos ao projeto para lidar com a complexidade no desenvolvimento de sistemas embarcados (GOKHALE; BALASUBRAMANIAN; LU, 2004; DENG; SCHMIDT; GOKHALE, 2006; ANNE et al., 2009; DRIVER et al., 2010; QIU; ZHANG, 2011). Uma abordagem semelhante vem sendo proposta para o desenvolvimento de projetos implementados em FPGAs (QUADRI; MEFTALI; DEKEYSER, 2008; MUCK et al., 2011; CARDOSO et al., 2012). Segundo Sommerville (2007), *abstrair* significa utilizar modelos ou linguagens de programação de alto-nível, que removam ou ocultem detalhes de implementação, tornando o processo de compreensão e desenvolvimento mais simples. Isso implica em ocultar detalhes de implementação como, por exemplo, os requisitos não funcionais nas fases iniciais de desenvolvimento. No entanto, abstrair detalhes de implementação é um desafio para o desenvolvimento de sistemas embarcados que lidam com várias restrições de projeto, tais como consumo de energia, memória e área, mesmo nas fases iniciais do projeto (MONMASSON; CIRSTEA, 2007; SALEWSKI; TAYLOR, 2008). Esse desafio é uma brecha para o desenvolvimento de sistemas embarcados que ainda não foi tratado e explorado o suficiente. Esse estudo pode aperfeiçoar os processos e metodologias de desenvolvimento de sistemas embarcados e avançar o estado-da-arte da *engenharia de sistemas*.

A MDE vem sendo proposta como uma solução para agilizar o processo de desenvolvimento de sistemas embarcados, melhorando a produtividade e o *time-to-market* do produto (QUADRI; MEFTALI; DEKEYSER, 2008; WEHRMEISTER, 2009; QUADRI; MEFTALI; DEKEYSER, 2010; MOREIRA, 2012). A abordagem MDE utiliza-se de níveis mais abstratos para a modelagem dos sistemas como, por exemplo, modelos especificados na linguagem UML. A partir de mecanismos de transformação, um Modelo Independente de Plataforma (*Platform Independet Model ou PIM*) de execução é transformado em um Modelo Específico à Plataforma (*Platform Specific Model ou PSM*) para uma arquitetura escolhida e, neste momento, são adicionados os detalhes e restrições relativos à plataforma escolhida. A UML possui uma extensão específica para a modelagem de sistemas embarcados chamada MARTE (*Modeling and Analysis of Real-Time and Embedded systems*), que fornece pacotes para modelar tanto o software quanto o hardware. Com isso,

torna-se viável o processo de automatização do desenvolvimento de sistemas embarcados, contando com ferramentas e linguagens apropriadas para cada nível de abstração. Contudo, é necessário um mapeamento entre o artefato representado pelo modelo e o artefato que será gerado no código.

A UML foi desenvolvida com base no paradigma orientado a objetos. Assim a conversão de modelos para código orientado a objetos se torna natural. Entretanto quando se trata de hardware existem outros paradigmas envolvidos, devido a sua natureza concorrente e estrutural. Esse problema é mais claro em projetos implementados em FPGAs, onde a descrição do hardware resultará em sua estrutura lógica e comportamental. A linguagem VHDL (do inglês *Very high speed integrated circuit HDL*) é um dos padrões para descrição de hardware e se assemelha com uma linguagem estruturada. VHDL possui construções e elementos que não estão diretamente associados a nenhum artefato ou abstração da UML. Tais características tornam mais complexa a transformação de um modelo UML orientado a objetos para uma descrição de hardware que pode ser implementada em FPGA, sendo o mapeamento destas regras de implementação um desafio no projeto de sistemas embarcados com FPGA.

A falta de ferramentas apropriadas para lidar com tais requisitos em um nível mais abstrato do projeto é um desafio para a utilização de abordagens MDE em projetos implementados em FPGA. Os requisitos não funcionais influenciam durante todo o ciclo de desenvolvimento do projeto podendo estar ou não vinculados a alguma funcionalidade. Alguns autores propõem a utilização do paradigma orientado a aspectos para separar e modularizar a implementação dos requisitos não funcionais dos funcionais, possibilitando melhor gerenciamento e manutenção desses (ENGEL; SPINCYK, 2008; MUCK et al., 2011; CARDOSO et al., 2012; MEIER; HANENBERG; SPINCYK, 2012). O paradigma de Desenvolvimento de Software Orientado a Aspectos (do inglês *Aspect-Oriented Software Development, AOSD*) visa a separação de preocupações transversais com o uso de um tipo de abstração chamada *aspecto* (ELRAD; FILMAN; BADER, 2001). AOSD busca separar o tratamento de aspectos que estão presentes em todo o projeto, influenciando diversas funcionalidades, em módulos específicos, que são entrelaçados durante a compilação do código. O principal benefício apontado nesta abordagem é a reutilização do tratamento desses requisitos não funcionais, assim como a sua manutenção.

Esse trabalho aborda dois problemas: (i) o mapeamento dos elementos e comportamentos da UML para o código VHDL e (ii) o tratamento dos requisitos não funcionais em um nível mais alto de abstração com o emprego do paradigma orientado a aspectos. Assim, este trabalho apresenta uma abordagem para o desenvolvimento automatizado de projetos implementados em

FPGAs. Esta abordagem permite o desenvolvimento dos sistemas com a aplicação de técnicas da MDE, utilizando a UML como linguagem de modelagem para a geração automática de código VHDL. Os requisitos não funcionais do projeto são tratados pela aplicação de conceitos e técnicas utilizadas no paradigma de AOSD, permitindo separar o tratamento/gerenciamento de requisitos funcionais dos não funcionais. Esta proposta visa tornar o processo de desenvolvimento mais sistemático e controlado por meio de métricas. Foi desenvolvido um novo conjunto de regras de mapeamento dos elementos da UML para VHDL, com base nos conceitos apresentados em (MOREIRA, 2012). Esse conjunto de regras permite a transformação da especificação em alto nível do sistema embarcado para uma descrição do hardware em VHDL.

Em uma segunda etapa, foram identificados e implementados requisitos não funcionais com a abordagem orientada a aspectos. Os aspectos foram incluídos nas regras de mapeamento, permitindo a geração do código que instrumenta o projeto para o tratamento das restrições dos requisitos não funcionais. Por fim, para validar a abordagem, as regras de mapeamento e os aspectos desenvolvidos, foram desenvolvidos três estudos de caso de sistemas embarcados na plataforma FPGA. Esses estudos de caso permitiram avaliar a aplicabilidade e eficiência dos elementos desenvolvidos neste trabalho.

## 1.2 OBJETIVOS E ESCOPO DO TRABALHO

Considerando a problemática apresentada, o objetivo principal deste trabalho é: *Propor uma abordagem para o tratamento dos requisitos não funcionais para a plataforma FPGA com o uso de técnicas da MDE e AOSD, implementando o mapeamento de elementos de um modelo UML especificando um sistema embarcado, para construções na linguagem de descrição de hardware VHDL.*

O objetivo principal deste trabalho pode ser dividido nos seguintes objetivos específicos:

- Definir o mapeamento dos elementos da UML para construções da linguagem VHDL;

- Criar o conjunto de regras de mapeamento na ferramenta GenERTiCA para a geração do código VHDL a partir do modelo UML;

- Estender o *framework* DERAf, incluindo novos requisitos não funcionais, identificados na revisão da literatura;

- Criar um conjunto de regras de mapeamento para os requisitos não funcionais implementados;

- Realizar estudos de caso para avaliação da abordagem e das regras propostas;

- Avaliar o tratamento dos requisitos não funcionais utilizando as métricas identificadas.

### 1.3 CONTRIBUIÇÕES DO TRABALHO

A principal contribuição desse trabalho é a evidência de que é possível e benéfico a especificação de sistemas embarcados baseados em FPGA em alto nível de abstração a partir de modelos UML. Assim como o tratamento e gerenciamento dos requisitos não funcionais em projetos de sistemas embarcados na plataforma FPGA com o uso de AOSD, é possível e benéfico para o projeto. Este trabalho também fornece as seguintes contribuições:

- Definição de conceitos para a transformação dos modelos UML para construções da linguagem VHDL e suas limitações;

- Identificação de requisitos não funcionais importantes para a plataforma FPGA;

- Definição de conceitos para o tratamento de requisitos não funcionais na plataforma FPGA e seu mapeamento em aspectos que os tratam;

- Definição de *Pointcuts* para a linguagem VHDL e seus impactos;

- Extensão do DERAF e da ferramenta GenERTiCA para implementar a transformação proposta do modelo UML para VHDL;

- Implementar o tratamento dos requisitos não identificados para a linguagem VHDL com o uso de conceitos da orientação a aspectos;

- Identificação de métricas para a avaliação de projetos implementados em FPGA;

- Análise do impacto da utilização da abordagem proposta na plataforma FPGA.

### 1.4 ORGANIZAÇÃO DO TEXTO

O texto desta dissertação encontra-se organizado como indicado nos parágrafos a seguir.

No Capítulo 2 são apresentados os principais conceitos para o entendimento e elaboração deste trabalho, enquanto o Capítulo 3 apresenta uma revisão da literatura sobre a temática deste trabalho.

O Capítulo 4 descreve a implementação da transformação UML para VHDL proposta neste trabalho. Este capítulo foi dividido da seguinte maneira: a Seção 4.1 discute os principais requisitos não funcionais identificados para a plataforma FPGA, assim como as métricas para avaliação de projetos nesta plataforma; a Seção 4.3, por sua vez, apresenta as regras de mapeamento para a geração automática do código VHDL a partir dos modelos UML. Adicionalmente, a Seção 4.3 apresenta a definição dos *pointcuts* e aspectos identificados e desenvolvidos para a plataforma FPGA/VHDL.

O Capítulo 5 apresenta os estudos de caso desenvolvidos e os resultados dos experimentos realizados, assim como uma análise do impacto da abordagem proposta.

Por fim, o Capítulo 6 apresenta as conclusões deste trabalho e propostas de trabalhos futuros.

## 2 FUNDAMENTAÇÃO TEÓRICA

Esta seção apresenta os principais conceitos necessários para a execução deste projeto. Esses conceitos auxiliam no entendimento da problemática da pesquisa e servem como base para o desenvolvimento da abordagem proposta.

### 2.1 SISTEMAS EMBARCADOS

Segundo [Wolf \(2008\)](#), sistemas embarcados são dispositivos compostos por hardware e software que possuem um processador programável desenvolvidos para um propósito específico, diferentemente de computadores pessoais que são sistemas de uso geral. Os sistemas embarcados podem ser aplicados em diversas áreas desde eletrônicos de consumo até automação residencial, aplicações automobilística e aeroespaciais.

A utilização de sistemas embarcados iniciou-se por volta de 1970, com o desenvolvimento de processadores simples, em um único chip, para o uso em calculadoras. Observou-se que esses chips poderiam ser reprogramados para utilização com outros propósitos, dando origem ao termo *computer-on-a-chip* ([WOLF, 2008](#)). Mais tarde passou-se a usar o termo *System-on-a-Chip* ou SoC, ou seja, um sistema completo em um único chip ([CARRO; WAGNER, 2003](#)).

Os sistemas embarcados atuais tem como desafio implementar algoritmos complexos, fornecendo interfaces sofisticadas, além de lidar com restrições rígidas de desenvolvimento e projeto como, por exemplo, o *time-to-market* ([CARRO; WAGNER, 2003](#)). Estas restrições levaram a adotação de microprocessadores para o desenvolvimento de sistemas embarcados, ao invés de computadores de uso geral, pois os microprocessadores são mais simples e podem ser facilmente customizados para atender estas restrições de projeto, além de possuírem custo mais baixo do que processadores. Outro aspecto importante em sistemas embarcados são as características de tempo-real, ou seja, os sistemas precisam responder corretamente aos estímulos e dados de entrada e ainda fornecer estas respostas no momento certo. O projetista precisa lidar com essas restrições levando em conta as limitações de poder de processamento, memória e consumo de energia das plataformas de sistemas embarcados. Essa característica torna o desenvolvimento desse tipo de sistema muito peculiar, trazendo limitações de hardware e software para o projeto ([WOLF, 2008](#)). [Carro e Wagner \(2003\)](#) apontam essas características como cruciais na definição pela tecnologia para o desenvolvimento de sistemas embarcados, que podem ser desde FPGAs até microprocessadores e microcontroladores.

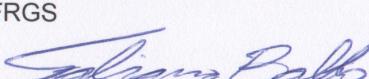

Wolf (2008) destaca como uma das dificuldades do desenvolvimento dos sistemas embarcados a adaptação do sistema no ambiente destino e a sua validação nesse ambiente, pois esse último possui características diferentes do ambiente de produção, conforme apresentado na Figura 1. Segundo Wolf (2008) é importante a utilização de ferramentas apropriadas de depuração em ambos os ambientes, assim como ferramentas de suporte na plataforma destino para a validação final e verificação de eventuais erros, tais como LEDs, *breakpoints*, portas de conexão serial ou USB.

Figura 1 – Ambiente de desenvolvimento e produção.

Fonte: Produção do próprio autor. Adaptado de (WOLF, 2008).

Carro e Wagner (2003) destacam a automação de projetos e testes como um fator chave para o sucesso no desenvolvimento de sistemas embarcados. A automação permite a reutilização de plataformas e componentes, além de agilizar o desenvolvimento dos sistemas, aumentando a viabilidade dos projetos, além de diminuir os custos e o *time-to-market*.

## 2.2 SISTEMAS DE TEMPO-REAL

Uma aplicação é dita de tempo-real quando é sensível ao cumprimento dos prazos (*deadlines*) de execução das tarefas (TSAI et al., 1996). Os sistemas embarcados podem possuir restrições de tempo, que dizem respeito ao prazo para execução das tarefas, assim como o tempo de validade dos dados após o prazo determinado (*freshness*) (FARINES; FRAGA; OLIVEIRA, 2000). Segundo Tsai et al. (1996) os sistemas de tempo-real podem ser classificados como:

- **Hard:** são aplicações altamente sensíveis aos prazos para a execução de tarefas. Se esses prazos não forem cumpridos, uma grande perda ou desastre pode acontecer. Exemplos de sistemas de tempo-real *hard* são

componentes de aeronaves, carros ou componentes utilizados na área médica, entre outros;

- **Soft:** são aplicações onde uma distribuição estatística de atrasos é aceitável, podendo até ocorrer perdas e danos devido a esse atraso, porém o impacto não é drástico. Geralmente os prazos *soft* podem degradar o desempenho do sistema, uma vez que precisam aguardar o término das tarefas. Exemplos de sistemas de tempo-real *soft* são aplicações de multimídia, como o YouTube ou TV digital.

Outra característica importante dos sistemas de tempo-real é a *previsibilidade*, pois é necessário saber exatamente quando uma tarefa começa e termina, além de vários outros fatores que afetam no processamento, como o escalonamento das tarefas, atrasos, preempção, entre outros. Dessa forma, uma das métricas mais importantes para sistemas de tempo-real é conhecer o Pior Caso do Tempo de Execução (do inglês *Worst Case Execution Time - WCET*) de uma tarefa, pois permite controlar o cumprimento de prazos de execução.

## 2.3 FIELD-PROGRAMMABLE GATE ARRAY

*Field-Programmable Gate Array* ou FPGA são Circuitos Integrados (CI) formados por vetores de portas lógicas interconectadas que podem ser configuradas pelo usuário final, daí o nome *field-programmable* ([MAXFIELD, 2004](#)).

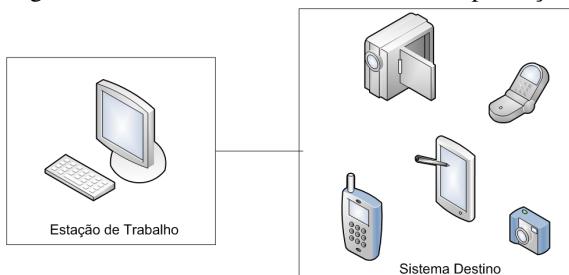

Os circuitos FPGAs são constituídos de unidades de lógica combinatorial, que são compostas por blocos de lógica e blocos de conexão programáveis. Os blocos de lógica permitem a implementação de vários tipos de portas lógicas, como “AND”, “OR” ou “XOR”. Os blocos de conexão permitem conectar os blocos de lógica, criando circuitos mais complexos. As FPGAs possuem fios conectando todos os blocos, denominados canais de comunicação, que podem ter diversos tamanhos, dependendo da distância entre os elementos conectados. Os blocos de conexão permitem selecionar quais canais serão utilizados para a lógica programada. As interconexões criadas entre os elementos da FPGA geram uma rede lógica de sinais, onde cada conexão é denominada *netlist*. As FPGAs também possuem os blocos de entrada e saída (*Input/Output Blocks - IOBs*) para comunicação externa ([WOLF, 2004](#)). Na Figura 2 é apresentada a arquitetura genérica de uma FPGA.

FPGAs são reconfiguráveis devido a tecnologia de fabricação. Algumas FPGAs são programadas uma única vez. Esse tipo de FPGA é constituída por links de fusíveis ou anti-fusíveis microscópicos. Todos os blocos de lógica vêm conectados de fábrica por esses links. A “programação” da FPGA se

Figura 2 – Arquitetura genérica de uma FPGA.

Fonte: Produção do próprio autor. Adaptado de ([MAXFIELD, 2004](#)).

baseia em remover fusíveis ou acionar os anti-fusíveis para gerar a lógica desejada. Tal processo não pode ser revertido. Já as FPGAs reprogramáveis, que são o objeto de estudo deste trabalho, são constituídas por memórias SRAM (*Static RAM*) composta de transistores e *flip-flops* (FF). Contudo as memórias SRAM perdem a informação ao desligar a fonte de energia, necessitando a sua reprogramação sempre que são religadas. Para resolver esse problema, são utilizadas memórias externas, que mantém os dados de configuração para serem carregados no momento em que a FPGA é ligada. O dados de configuração da FPGA são armazenados em um arquivo denominado *bitstream* ([MAXFIELD, 2004](#)).

O desenvolvimento de projetos implementados em FPGAs segue um processo hierárquico, em diferentes níveis de abstração. Desde o modelo esquemático, onde a definição é em nível de portas lógicas, até o nível de descrição de hardware por meio de uma linguagem HDL (ver Seção 2.4) ([WOLF, 2004](#)). Após a especificação do projeto é efetuada a síntese do código, por uma ferramenta dedicada a plataforma FPGA utilizada como, por exemplo, a *ISE Web Pack* da empresa Xilinx<sup>1</sup>. Na etapa de síntese são efetuados a localização e roteamento dos componentes do projeto no circuito FPGA, além de otimizações que permitem melhorar o desempenho e consumo de energia do projeto e, então, é gerado o arquivo *bitstream* com os bits de configuração da FPGA.

<sup>1</sup> [www.xilinx.com](http://www.xilinx.com)

## 2.4 VHDL

Devido à complexidade no desenvolvimento de projetos eletrônicos e do aumento do número de componentes em um único CI, a atividade de definição do hardware em nível de portas lógicas e FFs tornou-se difícil e sujeita a erros. Assim, linguagens de descrição de hardware ganharam espaço devido à facilidade e agilidade que trazem para esta tarefa (ROTH, 1998). A linguagem VHDL foi proposta em 1980 pelo departamento de defesa dos Estados Unidos da América com o objetivo de padronizar a descrição de circuitos integrados, facilitando seu entendimento e desenvolvimento. Atualmente a linguagem VHDL é padronizada pela *Institute of Electrical and Electronics Engineers* (IEEE) nas normas internacionais 1076 e 1164, cuja última atualização é de 2009 (IEEE, 2009). Esta linguagem permite descrever tanto a estrutura de circuitos eletrônicos, como também o seu comportamento (PEDRONI, 2004).

Outra linguagem muito popular para descrição de hardware é o Verilog. Verilog segue uma metodologia “*bottom-up*”. O Verilog é utilizado em geral para a simulação do comportamento de circuitos. Uma de suas limitações é não permitir a definição de diferentes comportamentos em um único módulo (ROTH, 1998). Já a linguagem VHDL segue uma metodologia “*top-down*” e permite utilizar múltiplos níveis de modelos com diferentes arquiteturas, além de também permitir a simulação de circuitos (ROTH, 1998).

VHDL permite descrever as portas lógicas e as conexões que serão configuradas no hardware por meio de expressões booleanas. Outra característica importante é que os comandos VHDL executam em paralelo, i.e., cada linha ou elemento do código corresponde a um circuito que processará sinais paralelamente com outros circuitos ou componentes. Entretanto VHDL também possui estruturas que permitem implementar máquinas de estado para processamentos sequenciais. A seguir são apresentados alguns conceitos básicos da linguagem VHDL com base em (PEDRONI, 2004; IEEE, 2009).

1. **Entity:** Define a estrutura física do circuito. Uma *entity* pode definir as seguintes estruturas:

- **Port:** esse comando define as entradas e saídas do circuito com tipo e direção.

- **Generics:** esse comando é utilizado para definir parâmetros para o circuito.

- **Constants:** permite definir constantes para o circuito.

Na Listagem 2.1 é apresentado um exemplo de definição de uma *entity*.

Listagem 2.1 – Exemplo de Entity

1 -- *Exemplo completo de uma Entity*:

```

2 entity exemplo is

3

4   Port ( sw : in STD_LOGIC_VECTOR (2 downto 0);

5       led : out STD_LOGIC_VECTOR (7 downto 0) );

6

7   generic ( gain : integer := 4;

8             timeDelay: time := 10 ns );

9

10  constant : rpu : real := 100.0;

11

12 end exemplo;

```

2. **Variables e Signals:** São duas formas de armazenar e transmitir valores no circuito na linguagem VHDL. *Variables* armazenam valores como em um software, porém esses valores são acessíveis somente no escopo em que a variável foi definida. Variáveis podem ser declaradas somente dentro de códigos sequenciais. *Signals* permitem a troca de valores por meio de sinais e estão acessíveis fora do escopo de onde foram definidos. Os sinais podem ser definidos em *entity*, *architecture* ou dentro de blocos de código sequencial. A principal diferença entre *signals* e *variables* é que, ao atualizar um valor em um *signal*, a atualização estará disponível somente no próximo ciclo de clock, enquanto que a atualização em *variables* é automática.

3. **Architecture:** Define o comportamento do circuito que pode ser do tipo *Behavioral*, *Data Flow* ou *Structural*. Nesta seção do código será definido efetivamente a estrutura lógica do circuito, i.e., como o circuito se comportará com base nas entradas e conexões. Variáveis locais e sinais podem ser declarados dentro do escopo da *architecture*, antes do comando *begin*, conforme o exemplo da Listagem 2.2. Esse local é chamado de “seção de declarações da arquitetura”. Essas variáveis poderão ser utilizadas somente dentro do escopo da arquitetura que as definiu.

#### Listagem 2.2 – Exemplo de Architecture

```

1 architecture behaviour exemplo is

2   -- declaracao de variaveis locais

3   signal sig1, sig2 : bit;

4 begin

5   -- '<=' e um comando de atribuicao para sinais

6   saida <= sig1 and sig2;

7 end exemplo;

```

4. **Process, Function e Procedure:** São comandos que permitem definir máquinas de estados para execução sequencial. É importante observar

que esses blocos de código executam em paralelo com outros comandos do código. *Process* são utilizados dentro de um *architecture* para criar um bloco de lógica sequencial. Esses blocos são locais do módulo implementado e não podem ser acessados por outras rotinas. Na Listagem 2.3 é apresentado um exemplo de utilização do comando *Process*.

### Listagem 2.3 – Exemplo de Architecture

```

1 architecture behaviour exemplo is

2     -- declaracao de variaveis de toda a aquitetura

3     signal port1, port2 : bit;

4 begin

5

6     nome:Process (port2) -- lista de variaveis sensitivas

7         -- declaracao de variaveis locais do processo

8     signal sig1, sig2 : bit;

9 begin

10     -- aqui vai o codigo sequencial

11     port2 <= sig1 or sig2;

12 end nome;

13

14 -- esse comando executa em paralelo com o processo

15 port <= port2;

16

17 end exemplo;

```

*Procedures* e *functions* são utilizados em sub-programas para implementar um bloco de lógica sequencial que pode ser chamado por outras rotinas, permitindo o seu reaproveitamento em várias rotinas. *Procedures* não retornam nenhum valor após o processamento, já *functions* retornam algum valor. Não é permitido a declaração de componentes em *procedures* e *functions*. Sinais somente podem ser declarados em *procedures* e *function* quando esses forem declarados dentro de um *process* (PEDRONI, 2004). As ferramentas de síntese podem sintetizar as estruturas de *procedures* e *function* de forma *inline* onde as chamadas dos *procedures* e *function* são substituídas pelo corpo destas estruturas, replicando o hardware gerado, ou com a criação de uma componente independente para execução das *procedures* e *function* para o qual será necessário a definição de um protocolo de comunicação e regras de escalonamento (RAMACHANDRAN et al., 1993).

## 2.5 REQUISITOS NÃO-FUNCIONAIS

Segundo Sommerville (2007) os requisitos de sistemas podem ser divididos em requisitos funcionais, não funcionais e de domínio. Requisitos funcionais são aqueles que definem as funcionalidades do sistema de forma completa e concisa. Já os requisitos não funcionais se referem as restrições do

projeto que afetam uma ou mais de suas funcionalidades, tais como restrições de tempo, utilização de recursos ou padrões de desenvolvimento. São também requisitos não funcionais restrições como confiabilidade e integridade, não relacionados diretamente a uma funcionalidade. Enquanto que os requisitos de domínio estão relacionados ao domínio de aplicação, como tipos e tamanho de dados (**SOMMERVILLE, 2007**).

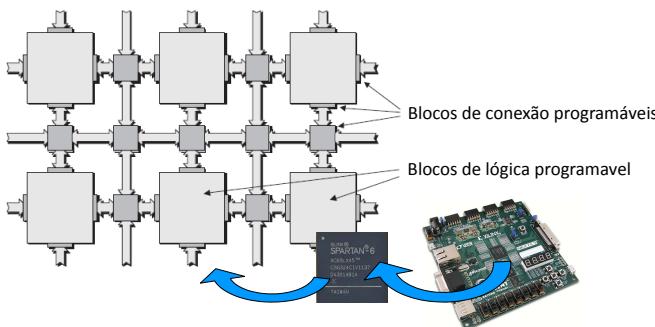

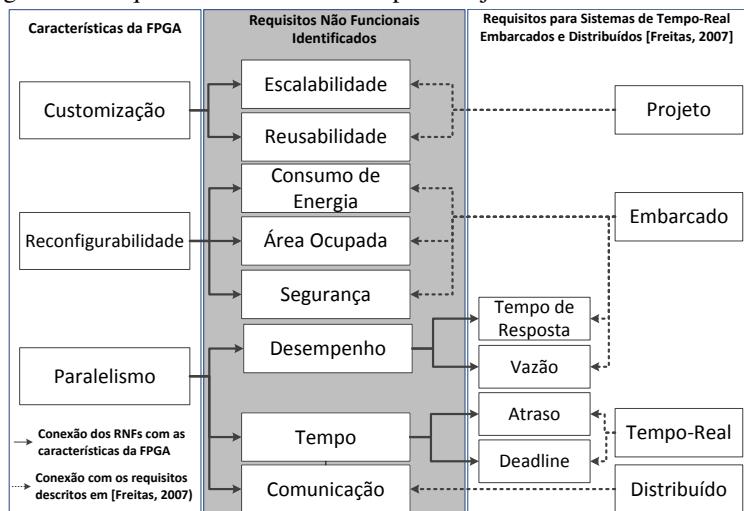

**Sommerville (2007)** divide os requisitos não funcionais em três tipos: (i) requisitos de produto, que definem o comportamento e qualidade do produto; (ii) requisitos organizacionais, relacionados à qualidade do projeto; e (iii) requisitos externos, que abrangem os comportamentos emergentes com a integração com outros sistemas. **Bertagnolli (2004)** propõem outra classificação dos requisitos não funcionais visando facilitar seu entendimento e a sua identificação no projeto, na qual os requisitos são descritos de forma genérica e então são subdivididos em requisitos específicos, permitindo um nível maior de abstração. Utilizando tal classificação, **Bertagnolli (2004)** propõem o *framework FRIDA (From Requirements to Design using Aspects)* para gerenciar os requisitos do projeto e auxiliar na identificação e tratamento de requisitos não funcionais aplicando o paradigma orientado a aspectos. Baseado na proposta de **Bertagnolli (2004)**, **Freitas (2007)** adaptou o FRIDA para uma classificação dos requisitos não funcionais para sistemas de tempo-real embarcados e distribuídos, criando a extensão RT-FRIDA. A classificação proposta por **Freitas (2007)** é apresentada na Figura 3. A classificação dos requisitos não funcionais proposta por **Freitas (2007)** foi utilizada por **Wehrmeister (2009)** para a construção do *framework DERAf* que serve como base para a ferramenta GenERTiCA.

Existem vários trabalhos que abordam o tratamento de requisitos não funcionais em sistemas embarcados. Entretanto, poucos trabalhos abordam o tratamento dos requisitos não funcionais no contexto de sistemas implementados em FPGA. As características especiais das FPGAs, tais como reconfigurabilidade e paralelismo, não são propriamente abordadas no projeto como um todo. **Salewski e Taylor (2008)** destacaram o impacto dos requisitos não funcionais em aplicações industriais baseadas em FPGA.

Com o objetivo de tratar os requisitos não funcionais em projetos implementados em FPGA, propôs-se um relacionamento entre os requisitos descritos em **Freitas (2007)** e as características das FPGAs, visando identificar os requisitos que tem maior impacto sobre essa plataforma. Essa relação e os requisitos não funcionais identificados a partir da análise da literatura são apresentados na Seção 4.1.

Figura 3 – Classificação dos requisitos não funcionais.

Fonte: (FREITAS, 2007).

## 2.6 ORIENTAÇÃO A ASPECTOS

A Programação Orientada a Aspectos (*Aspect-Oriented Programming, AOP*) foi proposta como uma solução para uma lacuna do paradigma orientado a objetos. Segundo Kiczales et al. (1997) observou-se que alguns requisitos podem influenciar diversas funcionalidades do projeto e eles não podem ser implementados como o comportamento de um único objeto. Esses requisitos, que estão presentes em todo o projeto, são denominados requisitos transversais como, por exemplo, o *log* do sistema. Em outras palavras esses requisitos atravessam (do inglês *cross-cutting*) as funcionalidades básicas do sistema (KICZALES et al., 1997). Como consequência, o código para tratamento desses requisitos acaba sendo espalhado por todo o projeto, o que leva a um código disperso e confuso (KICZALES et al., 1997).

A partir dessa ideia surgiu o paradigma de Desenvolvimento de Software Orientado a Aspectos (AOSD). Esse paradigma se baseia no conceito de *separação de preocupações*, que se referem a alguma característica ou área de interesse do projeto (ELRAD; FILMAN; BADER, 2001). Segundo Sommerville (2007), o AOSD se baseia na introdução da abstração *aspecto* ao paradigma orientado a objetos, que representam as *preocupações transversais* do projeto, ou seja, os requisitos que são implementados em várias funcionalidades ao mesmo tempo. As preocupações transversais estão geralmente

associadas ao tratamento de requisitos não-funcionais.

Kiczales et al. (1997) diferenciam aspectos de componentes, onde componentes são as funcionalidades que podem ser implementadas de forma geral em um único procedimento; já aspectos não podem ser encapsulados em um único procedimento. A implementação dos requisitos transversais utilizando abordagens tradicionais (e.g. orientação a objetos ou o paradigma estruturado) acaba levando ao espalhamento do código de tratamento por várias funcionalidades (do inglês, *Scattering*) e na ocorrência de diversos requisitos sendo tratados e implementados em uma mesma funcionalidade (do inglês *Tangling*). Esse espalhamento e o emaranhamento produzem um código com baixa coesão e alto acoplamento, reduzindo a possibilidade do seu reuso.

O objetivo da abordagem AOSD é separar o tratamento das preocupações transversais das outras funcionalidades do projeto, sendo que o programa final será a composição dos objetos, métodos e aspectos (SOM-MERVILLE, 2007). Além disso, os aspectos indicam onde o tratamento das preocupações transversais será introduzido nas funcionalidades. O processo de unir os aspectos com as demais funcionalidades do projeto é denominada *entrelaçamento*. Essa separação permite melhorar a manutenção do código e diminuir erros de programação (ELRAD; FILMAN; BADER, 2001).

Na Listagem 2.4 são apresentados dois exemplos de requisitos entrelaçados em um código VHDL, nas linhas 1-5 e 21-25. Esse trecho de código implementa a funcionalidade do controle de velocidade e direção em um controlador para um motor elétrico. A linha 2 verifica o sinal de clock, para que o processamento execute somente quando o sinal estiver alto. Essa linha trata de um requisito transversal presente em todas as funcionalidades do sistema que operam em sincronia com o sinal de clock (alto ou baixo). Já a linha 4 verifica se o motor está ativo para efetuar o processamento. Esta validação é feita em todas as funcionalidades que executam somente quando o motor está ligado.

Listagem 2.4 – Exemplo de Código com requisitos transversais.

```

1  -- Requisito A

2  if ((Clk'event) and (Clk = '1')) then

3    -- Requisito B

4    if (Enable = '1') then

5      --

6        sensor_diff := conv_integer(ADdifRead);

7        if(sensor_diff > dif_threshold) then

8          if(ADdifSignal = '0') then

9            Left_Right <= left;

10         else

11           Left_Right <= right;

12         end if;

13         Walk_Turn <= turn;

```

```

14      Speed <= speed_turn;

15      MotorEn <= '1';

16  else

17      Walk_Turn <= walk;

18      Speed <= speed_walk;

19      MotorEn <= '1';

20  end if;

21  —

22  else

23      MotorEn <= '0';

24  end if;

25  —

26  end if;

```

Os requisitos implementados nas linhas 2 e 4 da Listagem 2.4 podem ser tratados em módulos independentes das funcionalidades do sistema, o que facilitaria sua manutenção e reutilização em outros projetos semelhantes. Devido ao espalhamento de código desses requisitos transversais pelas funcionalidades do sistema, se torna difícil a separação desses tratamentos. É nestas situações que a AOSD se aplica, permitindo a separação desses requisitos, sem perder a confiabilidade e características do sistema.

Segundo Rashid et al. (2010) a indústria vem adotando a utilização de AOSD em projetos de média e grande escala. Porém, a maioria dos projetos se concentra na utilização das características básicas de AOSD e na aplicação em requisitos transversais bem conhecidos como monitoramento do código, validação da arquitetura do sistema e *log* de erros (RASHID et al., 2010). Rashid et al. (2010) destacam que o maior desafio na adoção de AOSD é na sua aplicação em processos de desenvolvimento atuais, o que inclui no preparo e treinamento da equipe de desenvolvimento e gestores para a nova metodologia. Aqueles autores citam como principais benefícios na utilização de AOSD a simplificação e diminuição do modelo de dados e a estabilidade sobre as manutenções e mudanças do projeto. Entretanto, também destacam fragilidades na abordagem em consequência de problemas emergentes, relacionados aos *pointcuts* que são definidos de acordo com os nomes de classes, métodos, campos, entre outros, que podem sofrer alterações invalidando a definição dos *pointcuts* (RASHID et al., 2010). Além disso, Rashid et al. (2010) observaram uma falha na aplicação de *pointcuts* em projetos baseados em camadas, onde definições de uma camada afetaram outras que não deveriam ser afetadas.

A seguir são apresentados os principais conceitos da abordagem AOSD que serviram como base para construção da solução proposta. Esses conceitos são baseados nas definições apresentadas em (KICZALES et al., 1997; SOMMERVILLE, 2007; WEHRMEISTER, 2009).

- **Aspecto:** É abstração do requisito transversal que será implementado

por *adaptações* e *pointcuts*; A Listagem 2.5 apresenta a definição de um aspecto na linguagem AspectJ (KICZALES et al., 1997).

Listagem 2.5 – Exemplo de Aspecto definido na linguagem AspectJ (KICZALES et al., 1997).

```

1 public aspect AspectoExemplo{

2     // define o pointcut

3     pointcut point1(): execution(**());

4     //define a adaptação

5     before() : point1(){

6         system.out.println("Adaptacao_point1");

7     }

8 }

```

- **Adaptação:** Especifica as modificações que devem ser realizadas em um ou mais elementos do sistema para tratar um requisito transversal, encapsulando tal tratamento em um único componente. A adaptação pode ser de duas formas: (i) estrutural, se refere a adaptações na estrutura de um elemento; (ii) comportamental, que se refere a alteração no comportamento de um elemento; As linhas 5-7 (Listagem 2.5) apresentam um exemplo de definição de uma adaptação comportamental que adiciona uma mensagem aos elementos afetados. O termo “before” indica que a adaptação será introduzida antes do elemento selecionado.

- **Join Points:** Definem onde as adaptações devem ser aplicadas. Os *join points* são expressões de seleção de funcionalidades, métodos, classes, etc., sobre os quais serão aplicadas as adaptações, funcionando como filtros sobre os elementos da especificação do sistema. Alguns termos e curingas são utilizados para a definição de *join points*. Na Listagem 2.5 a linha 3 apresenta um exemplo de definição de um *join point*: “execution(\*\*())”. Esse *join point* seleciona a execução de todos os métodos do projeto. O caractere “\*\*” funciona como um curinga indicando que qualquer outro caractere passará pelo filtro na posição em que foi utilizado.

- **Pointcuts:** Ligam as *adaptações* aos *join points*, i.e. definem qual adaptação ocorrerá para um determinado *join point*. Na Listagem 2.5 a linha 3 representa a definição de um *pointcut* que vincula a adaptação *point1* ao *join point* que seleciona a execução de todos os métodos.

- **Entrelaçamento do Aspecto:** (do inglês *Aspect Weaver*) é o processo de entrelaçamento dos aspectos com as funcionalidades do sistema, i.e., a aplicação das adaptações dos aspectos sobre as funcionalidades afetadas nos *join points* definidos.

## 2.7 A METODOLOGIA AMODE-RT

A metodologia AMoDE-RT (*Aspect-oriented Model-Driven Engineering for Real-Time systems*) proposta por Wehrmeister (2009), e as ferramentas de suporte a essa metodologia, foram estendidas neste trabalho para dar suporte a geração de código para a linguagem VHDL. Esta nova versão da metodologia foi utilizada para o desenvolvimento dos estudos de caso. Na metodologia AMoDE-RT, a modelagem do sistema alvo é realizada em um alto-nível de especificação utilizando a UML em conjunto com o perfil MARTE. O tratamento dos requisitos não funcionais é realizado usando conceitos de AOSD por meio dos diagramas ACOD (*Aspects Crosscutting Overview Diagram*) e JPDD (*Join Point Designation Diagrams*) e do framework DERAf (*Distributed Embedded Real-Time Aspects Framework*). MARTE possui estereótipos para a definição da estrutura e comportamento temporal dos sistemas de tempo-real embarcados e distribuídos. Esses mesmos conceitos podem ser utilizados na plataforma FPGA.

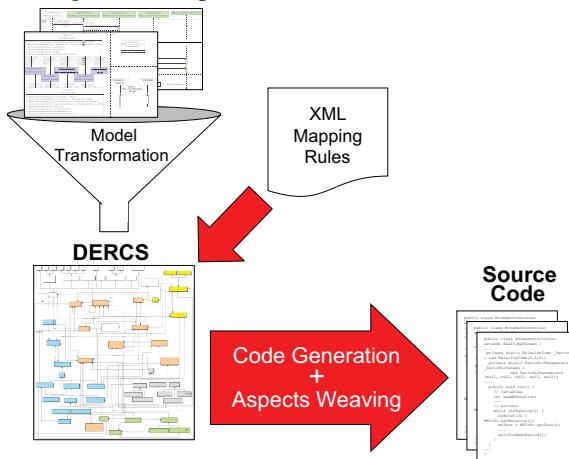

Os modelos especificados em alto-nível são transformados em um modelo intermediário denominado *Distributed Embedded Real-time Compact Specification (DERCS)* que é um PIM. O modelo DERCS é livre de ambiguidades e detalhado o suficiente para a geração de código a partir de seus elementos. Os elementos do modelo DERCS são transformados em código na linguagem alvo a partir de regras que mapeiam os elementos DERCS para elementos da linguagem alvo.

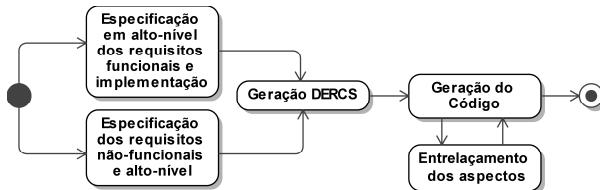

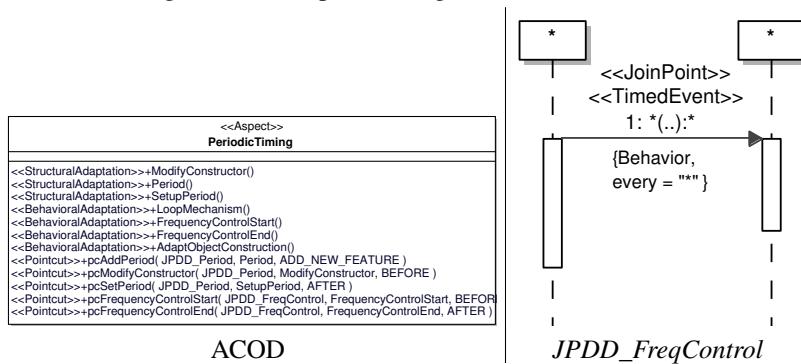

Na Figura 4 é apresentado o fluxo do processo de geração de código seguindo a metodologia AMoDE-RT. A atividade de “Geração do Código” é realizada com o uso de regras de mapeamento definidas e estruturadas em um arquivo de *scripts* no formato *eXtensible Markup Language (XML)*. O resultado desse processo é o código fonte na linguagem selecionada para a plataforma alvo. A ferramenta GenERTiCA (*Generation of Embedded Real-Time Code based on Aspects*) utiliza a metodologia AMoDE-RT para a geração do código. Na Figura 5 é apresentado um resumo das principais etapas no processo da ferramenta GenERTiCA.

A ferramenta GenERTiCA foi construída como um *plugin* para a ferramenta de modelagem Magic Draw<sup>2</sup>. O sistema é especificado na ferramenta Magic Draw, e, após, o *plugin* é acessado para a geração do código. A ferramenta GenERTiCA percorre todos os meta-elementos presentes no projeto selecionado, gerando o modelo DERCS. A partir desse ponto, a ferramenta GenERTiCA executa a leitura do arquivo XML que contém as regras de mapeamento para a linguagem alvo e executa o processo de geração de código baseado nestas regras.

---

<sup>2</sup> <http://www.nomagic.com/>

Figura 4 – Fluxo do processo de geração de código.

Fonte: Produção do próprio autor.

Figura 5 – Etapas da ferramenta GenERTiCA.

Fonte: (WEHRMEISTER, 2009).

As regras para conversão dos elementos da UML para os elementos da linguagem alvo são especificadas em um arquivo de *scripts* no formato XML utilizando a linguagem *Template Velocity*<sup>3</sup>. Os *scripts* definem trechos de código VHDL que devem substituir os meta-elementos do modelo DERCS, gerados pela ferramenta GenERTiCA. As Listagens 2.6 e 2.7 apresentam um exemplo de regras de mapeamento e de código gerado. O *script* da Listagem 2.6 define as regras para o tratamento das definições dos métodos da classe. Esse bloco é utilizado na linguagem VHDL para a geração

<sup>3</sup> <http://velocity.apache.org>

das portas da entidade, selecionando todos os atributos que possuem métodos *get/set*. A Listagem 2.7 apresenta o resultado do processamento para uma classe chamada *Display*.

Listagem 2.6 – Exemplo de regra de mapeamento.

```

1 ...

2 #if ($Message.Name != $Class.Name )

3 #if($Message.isGetSetMethod())

4   #foreach ($msgGer in $Class.getMethods())

5     #if (!$msgGer.isGetSetMethod() and $msgGer.Name != $Class.Name)

6       #set($add = $lreadMes.add($DERCSHelper.

7           getListOfAttributesUsed($Class, $msgGer.Name, 0)))