# UNIVERSIDADE DO ESTADO DE SANTA CATARINA – UDESC CENTRO DE CIÊNCIAS TECNOLÓGICAS – CCT PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA – PPGEEL

**AUGUSTO MANFROI MEDEIROS**

ASSESSMENT OF A CONVENTIONAL 4L DC-DC FLYING CAPACITOR TOPOLOGY TO OPERATE IN RESONANT MODE AND SOFT-SWITCHING CAPABILITY

# **AUGUSTO MANFROI MEDEIROS**

# ASSESSMENT OF A CONVENTIONAL 4L DC-DC FLYING CAPACITOR TOPOLOGY TO OPERATE IN RESONANT MODE AND SOFT-SWITCHING CAPABILITY

Master's thesis presented to the Graduate Program in Electrical Engineering of the Santa Catarina State University, as requirement for obtention of the title of Master in Electrical Engineering, concentration area of Electronic Systems.

Supervisor: Yales Rômulo de Novaes, Dr.

# Ficha catalográfica elaborada pelo programa de geração automática da Biblioteca Universitária Udesc, com os dados fornecidos pelo(a) autor(a)

Manfroi Medeiros, Augusto

Assessment of a conventional 4L DC-DC Flying Capacitor Topology to operate in resonant mode and soft-switching capability / Augusto Manfroi Medeiros. -- 2024.

194 p.

Orientador: Yales Rômulo de Novaes Dissertação (mestrado) -- Universidade do Estado de Santa Catarina, Centro de Ciências Tecnológicas, Programa de Pós-Graduação em Engenharia Elétrica, Joinville, 2024.

1. DC/DC Conversion. 2. Flying-Capacitor. 3. Multi-Resonant. 4. State-plane Trajectory. 5. WBG Devices. I. Rômulo de Novaes, Yales. II. Universidade do Estado de Santa Catarina, Centro de Ciências Tecnológicas, Programa de Pós-Graduação em Engenharia Elétrica. III. Título.

# **AUGUSTO MANFROI MEDEIROS**

# ASSESSMENT OF A CONVENTIONAL 4L DC-DC FLYING CAPACITOR TOPOLOGY TO OPERATE IN RESONANT MODE AND SOFT-SWITCHING CAPABILITY

Master's thesis presented to the Graduate Program in Electrical Engineering of the Santa Catarina State University, as requirement for obtention of the title of Master in Electrical Engineering, concentration area of Electronic Systems.

Supervisor: Yales Rômulo de Novaes, Dr.

# **EXAMINATION BOARD:**

Prof. Yales Rômulo de Novaes, Doctor Santa Catarina State University (UDESC) (Board's president / Supervisor)

Membros:

Prof. Joselito Heerdt, Doctor Santa Catarina State University (UDESC)

Prof. Thiago Batista Soeiro, Doctor University of Twente (UT)

Prof. Sérgio Vidal Garcia Oliveira, Doctor Santa Catarina State University (UDESC)

I dedicate this work to my parents, Flavio Medeiros and Ana Lucia Manfroi, to my brother Gustavo Manfroi Medeiros, and to my great wife, Mariane Hans Alexandre, who has devoted tremendous patience during this process.

# **ACKNOWLEDGEMENTS**

First of all, I would like to thank the State University of Santa Catarina (UDESC), the Electrical Engineering Graduation Program (PPGEEL) and the Núcleo de Processamento de Energia Elétrica (NPEE), for letting me be part of this program. Further, I would like to express my immense gratitude to my supervisor Yales for showing me the patience, resilience and the thoughtful discussions and advises not only professionally but also personally.

To my former employer, Volvo Car Corporation, and the staff, Riccardo Negri and Lars Johansson, who have encouraged me and let me pursue this path while reducing my working hours to dedicate to this project. Additionally, for the unconditional support and willingness to provide the lab infrastructure which was crucial for the validation and finalization of the project. Further, to my current Employer, OAK Amplifiers AB, and the staff, Mats and Sandra Otterdahl, who have been extremely supportive to my continuous education.

My parents, Flavio Augusto Jorge Medeiros and Ana Lucia Manfroi, who have guided me and provided for my wellness, without whom none if this would be possible. I extend this acknowledgment to my brother, Gustavo Manfroi Medeiros.

Lastly, I would like to express my gratitude, and appreciation, to my beloved wife, Mariane Hans Alexandre, who has accompanied me since before this journey has started and who has been showing me the strength and courage to continue pursuing this path. Furthermore, to the many days, holidays and vacations that, most importantly, were devoted and sacrificed, to let me focus on this project.

"The future belongs to those who believe in the beauty of their dreams." (ELEANOR ROOSEVELT, [19–])

# **ABSTRACT**

Multi-level Resonant Converter topologies have been addressed to increase the power density and efficiency of step-down intermediate conversion stages, for Low-voltage (LV) systems, due to the higher current demand, in addition to its inherent benefit of soft-switching capability and fixed static-gain ratio, while operating above, or at, Resonance. This work proposes an extension for the Multi-level Resonant Flying Capacitor Converter (ML-RFLCC), by demonstrating the potential soft-switching and voltage regulation capabilities of a 1:3 RFLCC while operating under, and at, the Resonance. Due to the increased number of state variables, it presents a comprehensive state diagram to demonstrate the operating principle, and dependencies, of the different set of LC resonant tanks. In order to achieve such operation, this work proposes a operating condition coefficient  $\Lambda$  to derive a design methodology. To validate the proposed operation condition, a 400V 500W GaN-based 1:3 RFLCC is presented, illustrating the theoretical correlation and non-idealities while operating under-resonance.

**Keywords**: DC-DC Conversion, Multi-level Converter. Flying-Capacitor. Multi-Resonant. State-plane Trajectory. WBG Devices.

# **RESUMO**

Conversores ressonantes multiníveis têm sido utilizados para alcançar altos níveis de densidade de potência e eficiência em conversores abaixadores de baixa tensão (LV), devido à demanda por altas correntes de saída e aos benefícios das propriedades de comutação suave. Esses conversores normalmente operam sincronizados ou acima da frequência de ressonância devido às suas características. Este trabalho propõe uma extensão ao conversor ressonante multinível do tipo capacitor flutuante (ML-RFLCC), demonstrando a capacidade de um conversor 1:3 de atingir comutação suave e regulação da tensão de saída enquanto opera em sincronização, ou abaixo, da frequência de ressonância. Por conta do número de variáveis de estado, é proposto um diagrama de estados para demonstrar o funcionamento do conversor proposto, e suas dependências, dos diferentes tanques ressonantes. Para atingir esses objetivos, este trabalho propõe um coeficiente de operação Λ. Um protótipo, empregando chaves do tipo GaN, é desenvolvido para validar os resultados teóricos e as não idealidades enquanto operando abaixo da frequência de ressonância.

**Palavras-chave**: Conversão CC-CC. Conversores Multiníveis. Capacitor Flutuante. Ressonância Multipla. Trajetória do plano de estado. semicondutores WBG.

# LIST OF FIGURES

| Figure 1 –  | Representation of Base form of different DC-DC Switched-Capacitor Topolo-        |    |

|-------------|----------------------------------------------------------------------------------|----|

|             | gies                                                                             | 27 |

| Figure 2 -  | Representation of different approaches for the realization of resonant switched- |    |

|             | capacitor converter (ReSCC)                                                      | 29 |

| Figure 3 –  | Basic Structure for a 3L flying capacitor boost DC-DC converter                  | 30 |

| Figure 4 –  | 3L resonant flying capacitor equivalent circuit for every topological stage      | 34 |

| Figure 5 –  | Generic Structure for a n-level resonant flying capacitor boost DC-DC converter. | 35 |

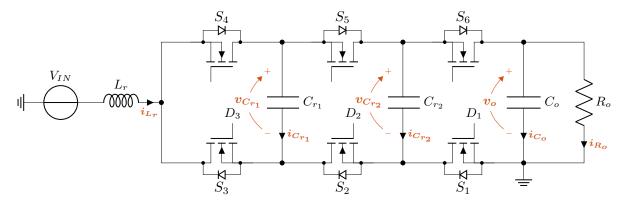

| Figure 6 –  | Proposed Converter Circuit Topology.                                             | 35 |

| Figure 7 –  | Generic Series Resonance LC Equivalent Circuit with a Differential-mode          |    |

|             | Voltage Excitation Signal                                                        | 37 |

| Figure 8 -  | Normalized State-Plane Trajectory for a Generic LC series resonant circuit.      | 40 |

| Figure 9 –  | Generic Series Resonance LCCp Equivalent Circuit with a Differential-mode        |    |

|             | Voltage Excitation Signal                                                        | 41 |

| Figure 10 – | Normalized State-Plane Trajectory for a Generic LCCp series resonant circuit.    | 43 |

| Figure 11 – | Generic Series Resonance LCCs Equivalent Circuit with a Differential-mode        |    |

|             | Voltage Excitation Signal                                                        | 44 |

| Figure 12 – | Normalized State-Plane Trajectory for a Generic LCCs series resonant circuit.    | 46 |

| Figure 13 – | Equivalent Circuit and Normalized State-Plane Trajectory for Operating           |    |

|             | Region I within Interval I                                                       | 51 |

| Figure 14 – | Equivalent Circuit for Operating Region I within Interval II                     | 51 |

| Figure 15 – | Equivalent Circuit and Normalized State-Plane Trajectory for Operating           |    |

|             | Region I within Interval IV.                                                     | 53 |

| Figure 16 – | Equivalent Circuit for Operating Region I within Interval V                      | 53 |

| Figure 17 – | Equivalent Circuit and Normalized State-Plane Trajectory for Operating           |    |

|             | Region I within Interval VII                                                     | 55 |

| Figure 18 – | Equivalent Circuit for Operating Region I within Interval VIII                   | 55 |

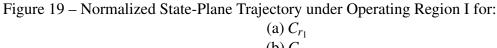

| Figure 19 – | Normalized State-Plane Trajectory for Operating Region I                         | 57 |

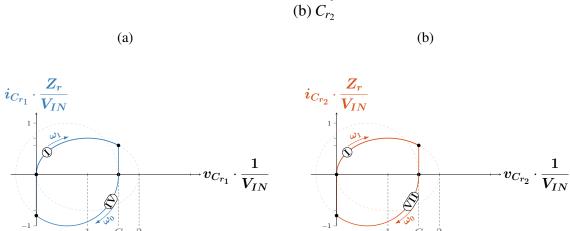

| Figure 20 – | Normalized Time-Domain State Variables for Operating Region I                    | 57 |

| Figure 21 – | Equivalent Circuit and Normalized State-Plane Trajectory for Operating           |    |

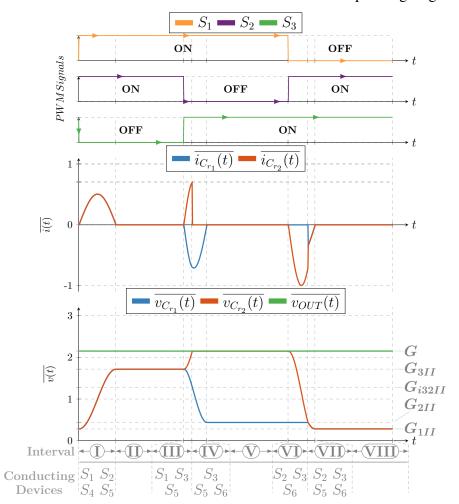

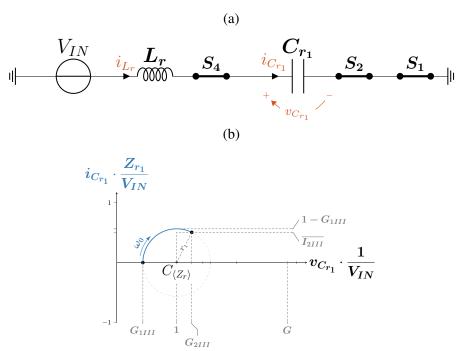

|             | Region II within Interval I                                                      | 59 |

| Figure 22 – | Equivalent Circuit and Normalized State-Plane Trajectory for Operating           |    |

|             | Region II within Interval III                                                    | 61 |

| Figure 23 – | Equivalent Circuit and Normalized State-Plane Trajectory for Operating           |    |

|             | Region II within Interval IV                                                     | 63 |

| Figure 24 – | Equivalent Circuit and Normalized State-Plane Trajectory for Operating           |    |

|             | Region II within Interval VI                                                     | 65 |

| Figure 25 - Equivalent Circuit and Normalized State-Plane Trajectory for Operating         |      |

|--------------------------------------------------------------------------------------------|------|

| Region II within Interval VII                                                              |      |

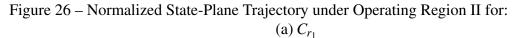

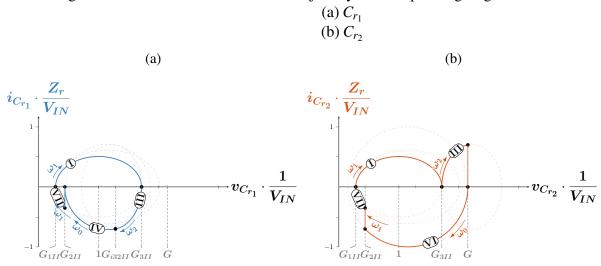

| Figure 26 – Normalized State-Plane Trajectory for Operating Region II                      | 68   |

| Figure 27 – Normalized Time-Domain State Variables for Operating Region II                 | 68   |

| Figure 28 - Equivalent Circuit and Normalized State-Plane Trajectory for Operating         |      |

| Region III within Interval I                                                               | 70   |

| Figure 29 - Equivalent Circuit and Normalized State-Plane Trajectory for Operating         |      |

| Region III within Interval II                                                              | 72   |

| Figure 30 - Equivalent Circuit and Normalized State-Plane Trajectory for Operating         |      |

| Region III within Interval IV                                                              | 74   |

| Figure 31 - Equivalent Circuit and Normalized State-Plane Trajectory for Operating         |      |

| Region III within Interval VI                                                              | 76   |

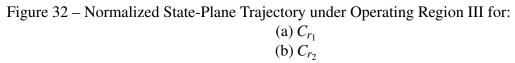

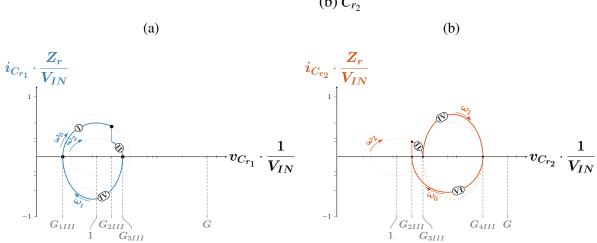

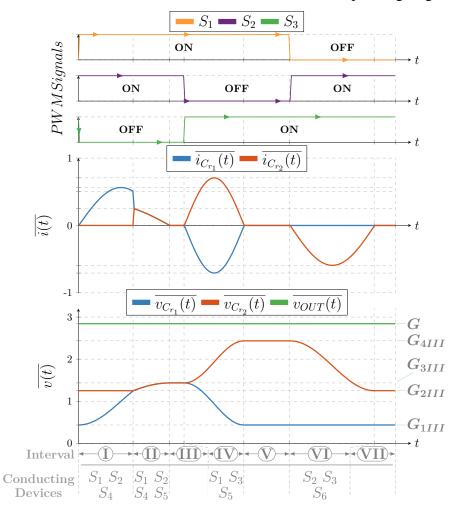

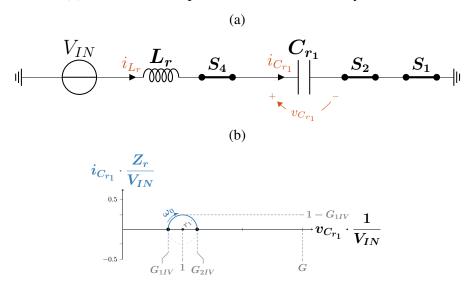

| Figure 32 – Normalized State-Plane Trajectory for Operating Region III                     | . 77 |

| Figure 33 – Normalized Time-Domain State Variables for Operating Region III                | 77   |

| Figure 34 – Equivalent Circuit and Normalized State-Plane Trajectory for Operating         |      |

| Region IV within Interval I                                                                | 79   |

| Figure 35 – Equivalent Circuit and Normalized State-Plane Trajectory for Operating         |      |

| Region IV within Interval III                                                              | 81   |

| Figure 36 – Equivalent Circuit and Normalized State-Plane Trajectory for Operating         |      |

| Region IV within Interval VI                                                               | 83   |

| Figure 37 – Normalized State-Plane Trajectory for Operating Region IV                      |      |

| Figure 38 – Normalized Time-Domain State Variables for Operating Region IV                 |      |

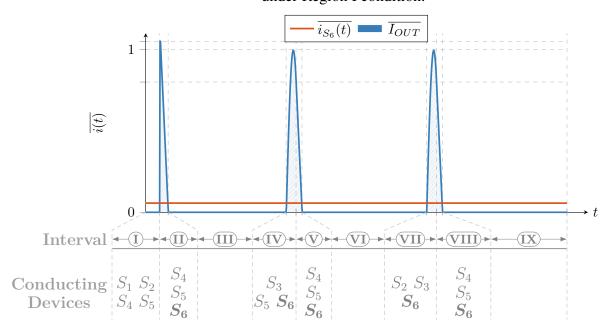

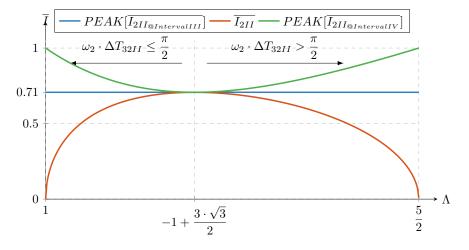

| Figure 39 – Area representation of Switch $S_6$ Current waveform within the topological    |      |

| stages under Region I condition                                                            | 88   |

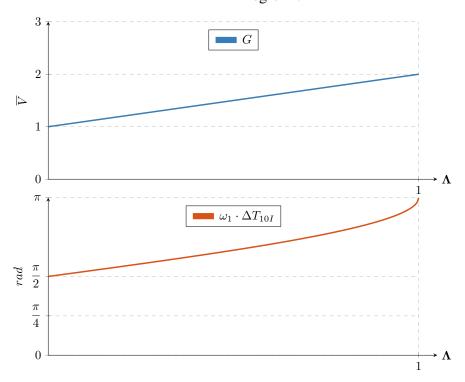

| Figure 40 – Output Static Gain and Phase-Timing Characteristics as a function of $\Lambda$ |      |

| within Region I                                                                            | 89   |

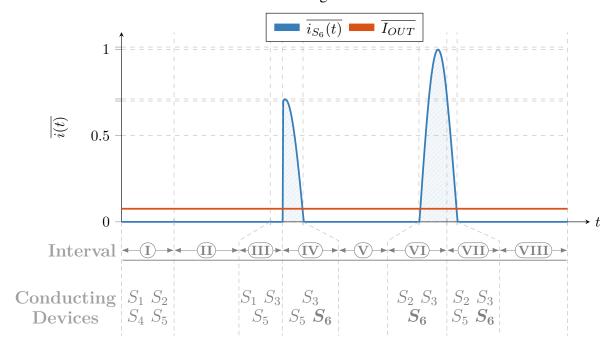

| Figure 41 – Area representation of Switch $S_6$ Current waveform within the topological    |      |

| stages under Region II condition.                                                          | 91   |

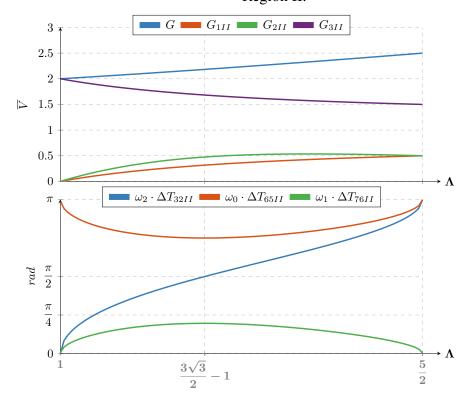

| Figure 42 – Output Static Gain and Phase-Timing Characteristics as a function of $\Lambda$ | , ,  |

| within Region II                                                                           | 93   |

| Figure 43 – Interval III and Interval IV Peak current stresses progression based on State- | 75   |

| plane Trajectory                                                                           | 93   |

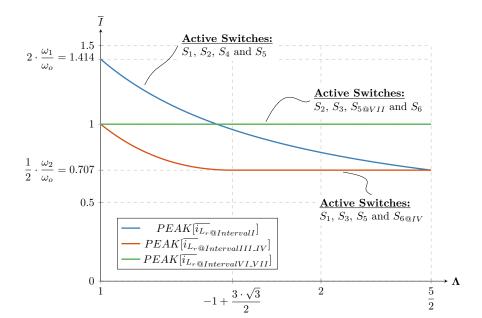

| Figure 44 – Peak current stresses progression based on resonant semi-cycles under Region   | 75   |

| II condition                                                                               | 94   |

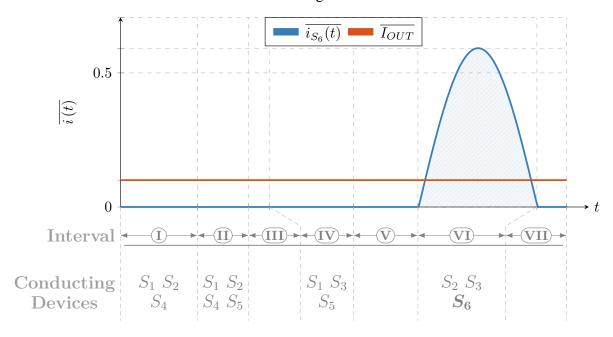

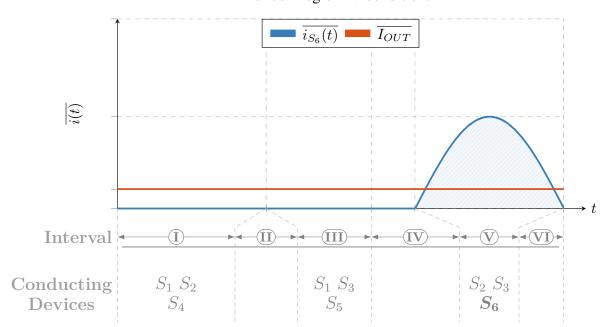

| Figure 45 – Area representation of Switch $S_6$ Current waveform within the topological    | 74   |

| stages under Region III condition                                                          | 95   |

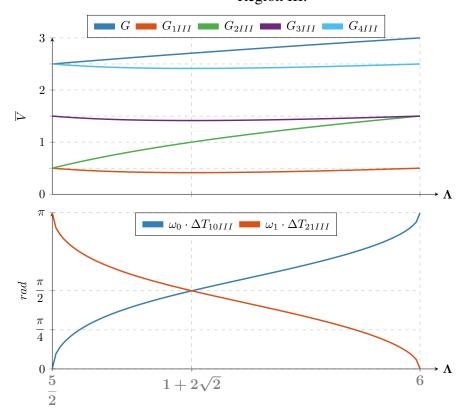

| Figure 46 – Output Static Gain and Phase-Timing Characteristics as a function of $\Lambda$ | 93   |

| within Region III                                                                          | 97   |

| within Region III                                                                          | 91   |

| Figure 47 – | Interval I and II Peak Current Stress Impact as a function of Λ within Region III     | 97  |

|-------------|---------------------------------------------------------------------------------------|-----|

| Figure 48 – | Area representation of Switch $S_6$ Current waveform within the topological           |     |

|             | stages under Region IV condition                                                      | 99  |

|             |                                                                                       | 100 |

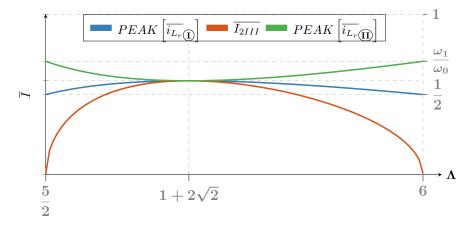

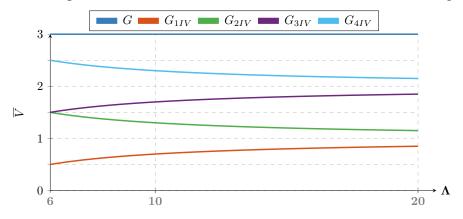

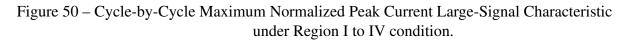

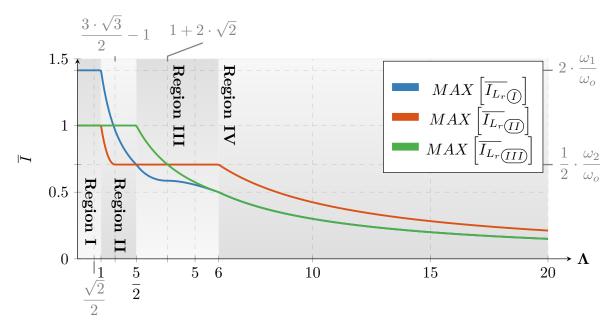

| Figure 50 – | Cycle-by-Cycle Maximum Normalized Peak Current Large-Signal Charac-                   |     |

|             |                                                                                       | 102 |

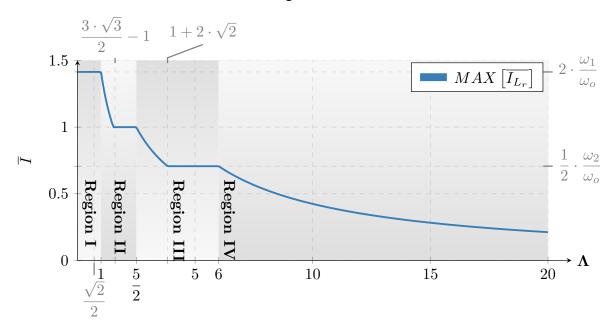

| Figure 51 – | Global Maximum Normalized Peak Current Large-Signal Characteristic                    |     |

|             |                                                                                       | 102 |

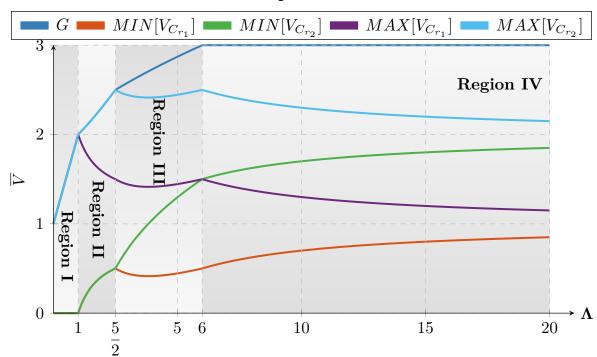

| Figure 52 – | 4L-RFLCC Static Output and Flying capacitors' Voltage Characteristic under            |     |

|             | Region I to IV condition                                                              | 103 |

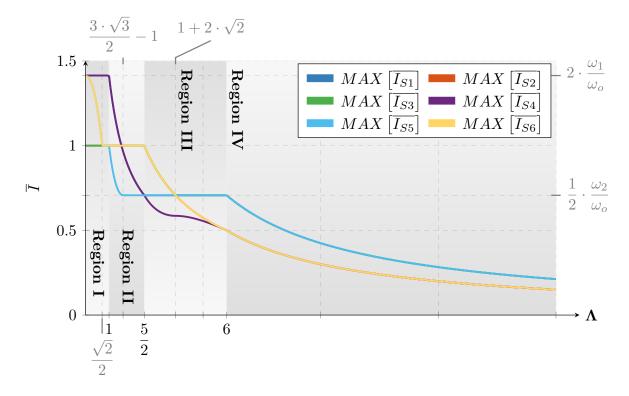

| Figure 53 – | 4L-RFLCC Switches $S_1 - S_6$ Maximum Current Stress Characteristic under             |     |

|             |                                                                                       | 103 |

| Figure 54 – | 4L-RFLCC Switches $S_1 - S_6$ Maximum Voltage Stress Characteristic under             |     |

|             |                                                                                       | 104 |

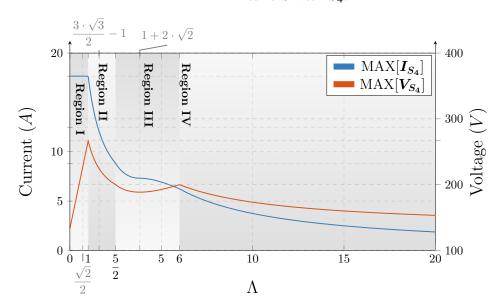

| Figure 55 – | Absolute Peak Current and Voltage Stresses for Active Switch $S_1$ under Target       |     |

|             | Specification Range                                                                   | 106 |

| Figure 56 – | Absolute Peak Current and Voltage Stresses for Active Switch $S_2$ under Target       |     |

|             |                                                                                       | 107 |

| Figure 57 – | Absolute Peak Current and Voltage Stresses for Active Switch $S_3$ under Target       |     |

|             |                                                                                       | 107 |

| Figure 58 – | Absolute Peak Current and Voltage Stresses for Active Switch $S_4$ under Target       |     |

|             | Specification Range                                                                   | 108 |

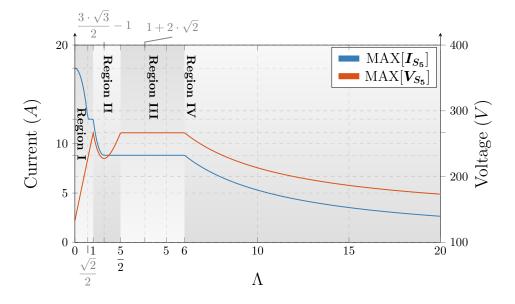

| Figure 59 – | Absolute Peak Current and Voltage Stresses for Active Switch $S_5$ under Target       |     |

|             | Specification Range                                                                   | 108 |

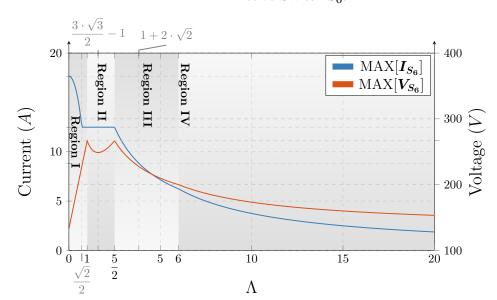

| Figure 60 – | Absolute Peak Current and Voltage Stresses for Active Switch $S_6$ under Target       |     |

|             | Specification Range                                                                   | 109 |

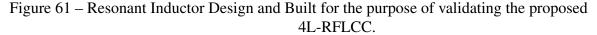

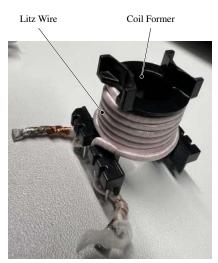

| Figure 61 – | Resonant Inductor Design and Built for the purpose of validating the proposed         |     |

|             | 4L-RFLCC                                                                              |     |

| _           | DC-link Capacitor Architecture for the Proposed 4L-RFLCC Prototype                    | 114 |

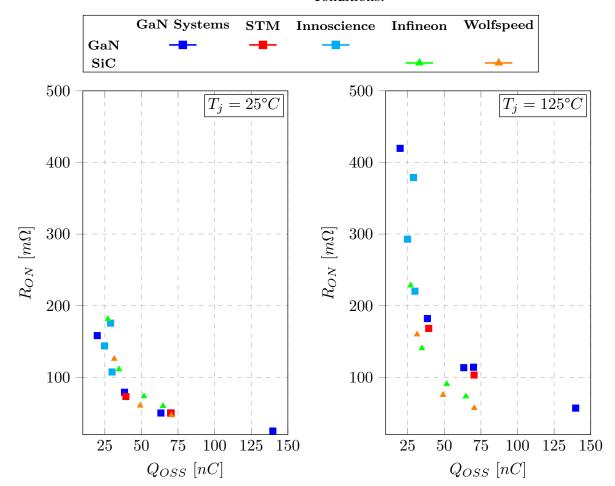

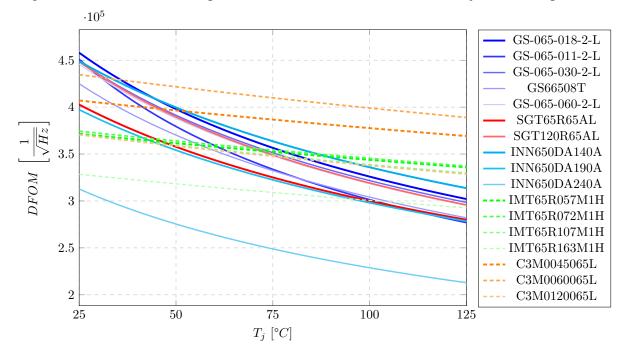

| Figure 63 – | SiC/GaN $R_{ON}$ and $Q_{OSS}$ distribution per device for different junction temper- |     |

|             | ature conditions                                                                      | 119 |

| Figure 64 – | SiC/GaN DFOM performance assessment as a function of junction temperature.            | 120 |

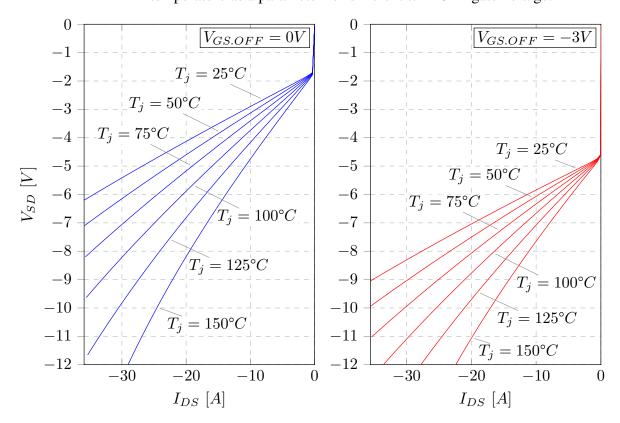

| Figure 65 – | Gan Systems's GS-0650-180-2-L's Reverse conduction Performance with                   |     |

|             | junction temperature as a parameter for different turn-OFF gate voltage               | 121 |

| Figure 66 – | Gan Systems's GS-0650-180-2-L's Reverse conduction Performance compar-                |     |

|             | ison towards 650V SiC Diodes from different suppliers with forward current            |     |

|             | $I_{DS}$ as a parameter for different Junction Temperatures $T_j$                     | 122 |

|             |                                                                                       |     |

| Figure 67 – 650V SiC Diodes $V_F$ and $Q_C$ distribution per device for different junction    |     |

|-----------------------------------------------------------------------------------------------|-----|

| temperature conditions under 10A forward current condition                                    | 123 |

| Figure 68 – System-level description of the FCML converter employing Cascaded Boot-           |     |

| strap Gate Drive                                                                              | 124 |

| Figure 69 – System-level description of the FCML converter employing Cascaded Boot-           |     |

| strap Gate Drive and Charge-Pump                                                              | 125 |

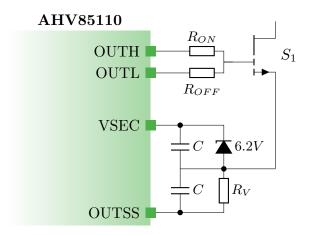

| Figure 70 – System-level Implementation of AHV85110 Bipolar Drive Supply for GaN              |     |

| Systems' GS-065-018-2-L                                                                       | 127 |

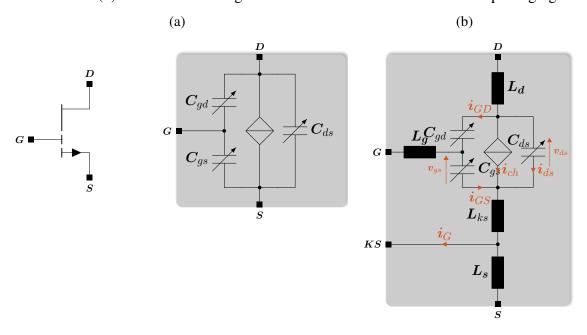

| Figure 71 – Different Representations of a GaN device                                         | 128 |

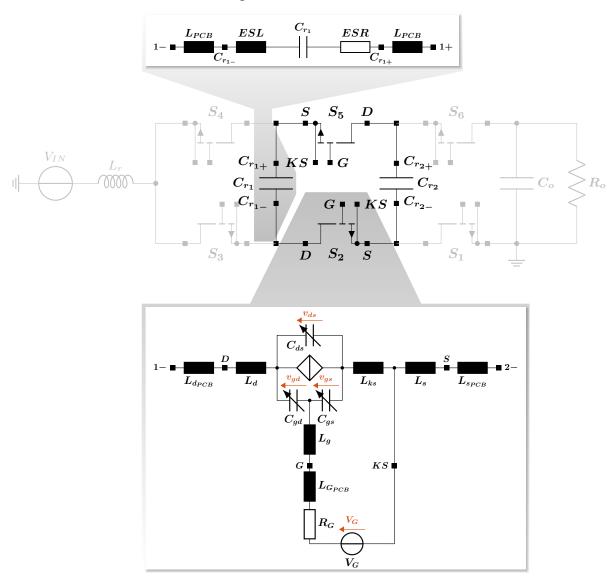

| Figure 72 – System-Level Description Model including Parasitic Elements in a single           |     |

| Flying Capacitor Commutation Cell (FLCCC)                                                     | 129 |

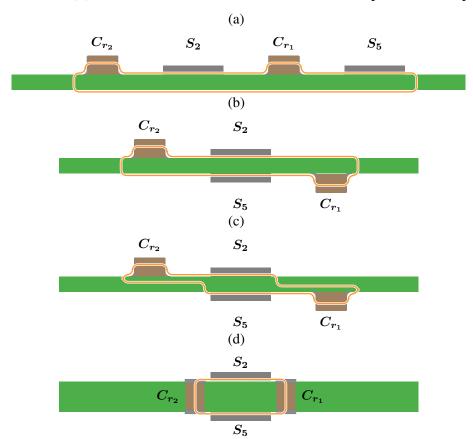

| Figure 73 – Different Vertical Commutation Loop layout approaches                             | 130 |

| Figure 74 – Final PCB Design Top and Bottom Layer View of a Flying Capacitor Com-             |     |

| mutation Cell                                                                                 | 131 |

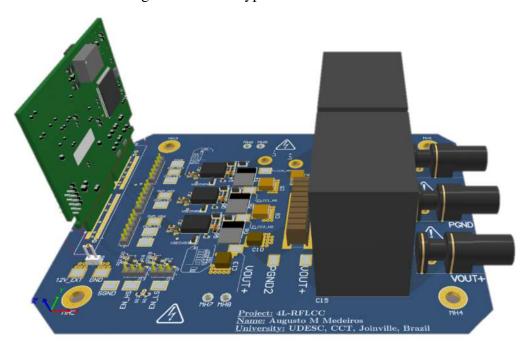

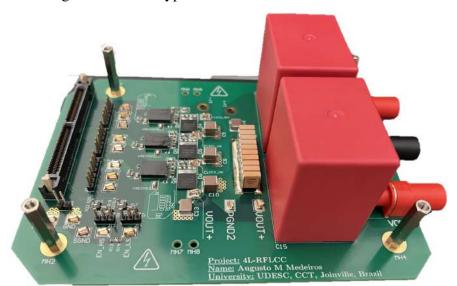

| Figure 75 – Prototype Board Altium 3D view                                                    | 131 |

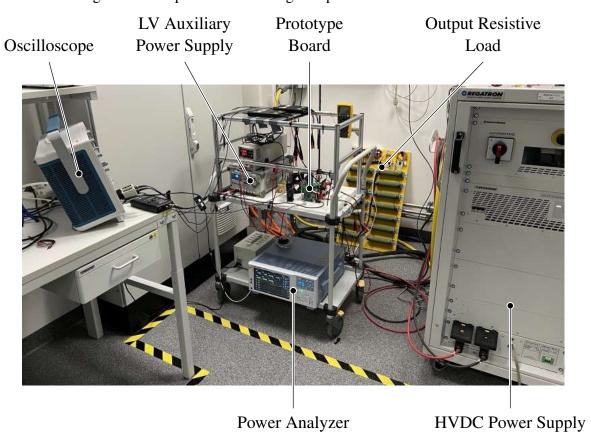

| Figure 76 – Experimental Testing Setup for 4L-RFLCC validation                                | 132 |

| Figure 77 – Prototype Board for 4L-RFLCC validation                                           | 133 |

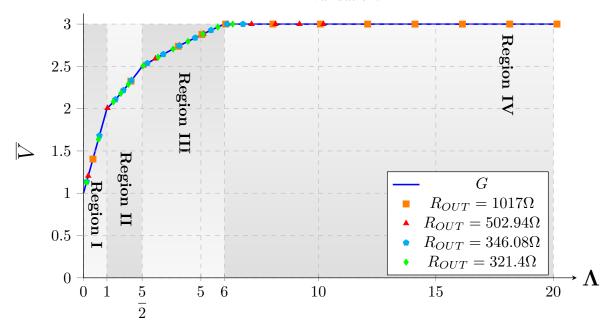

| Figure 78 – Experimental Test Condition Points utilized during the 4L-RFLCC prototype         |     |

| validation                                                                                    | 134 |

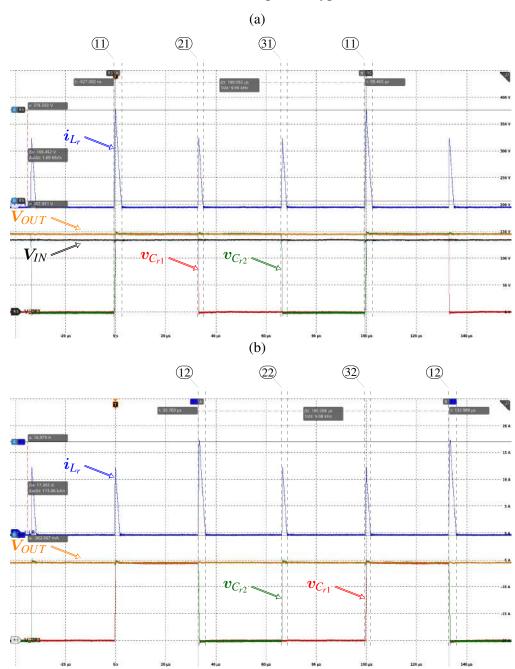

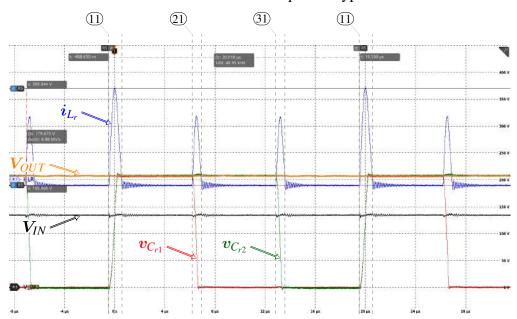

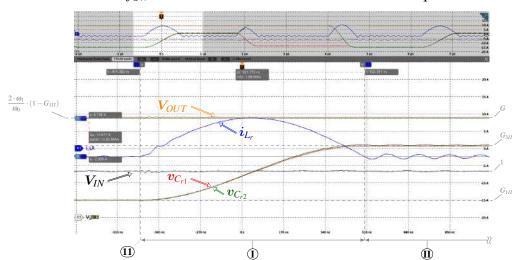

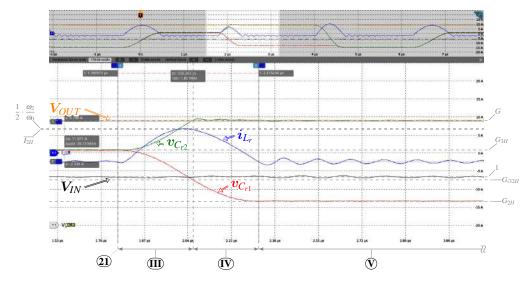

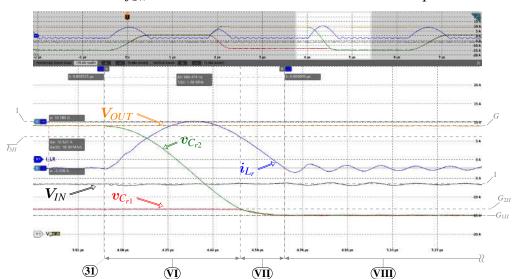

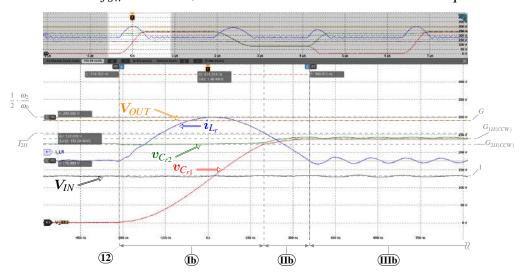

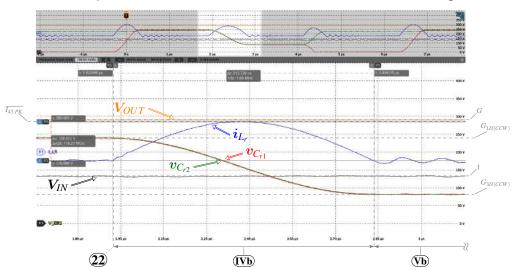

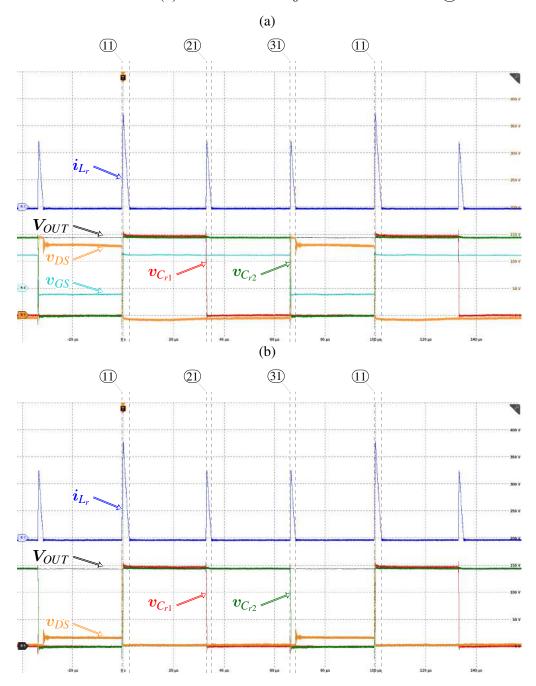

| Figure 79 – Experimental Results under Test Condition Set 1 and 2                             | 135 |

| Figure 80 – 1st to 3rd Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

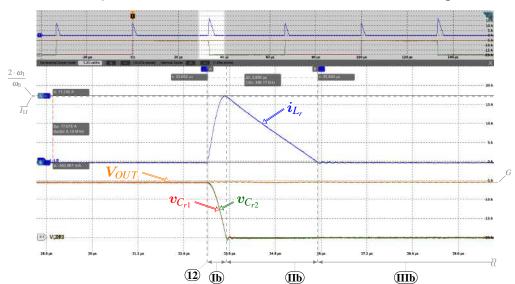

| $f_{SW} = 10kHz$ based on Clock-wise PWM Sequence                                             | 136 |

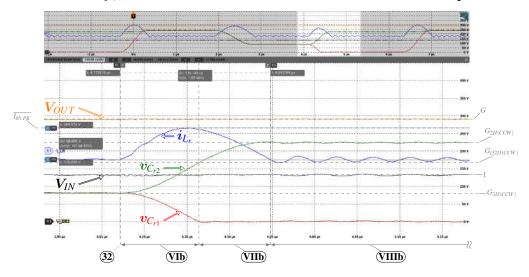

| Figure 81 – 4th to 6th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 10kHz$ based on Clock-wise PWM Sequence                                             | 137 |

| Figure 82 – 7th to 9th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 10kHz$ based on Clock-wise PWM Sequence                                             | 137 |

| Figure 83 – 1st to 3rd Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 10kHz$ based on Counter Clock-wise PWM Sequence                                     | 138 |

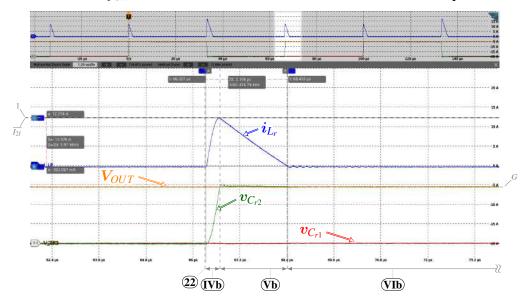

| Figure 84 – 4th to 6th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 10kHz$ based on Counter Clock-wise PWM Sequence                                     | 138 |

| Figure 85 – 7th to 9th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 10kHz$ based on Counter Clock-wise PWM Sequence                                     | 139 |

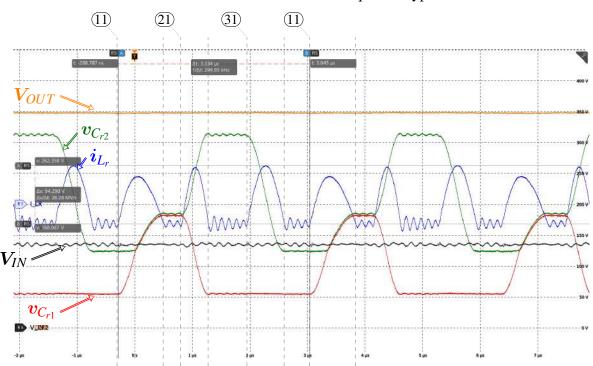

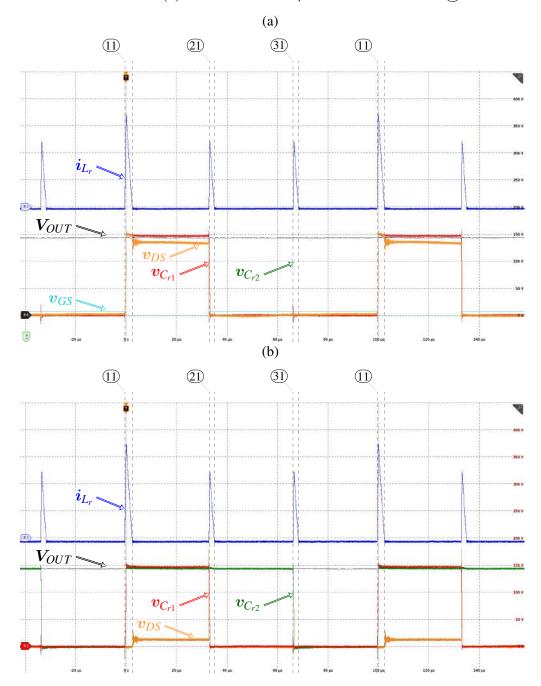

| Figure 86 – Experimental results under $R_{OUT}=321.4\Omega$ and $f_{SW}=50kHz$ based on      |     |

| Clock-wise PWM Sequence Type                                                                  | 139 |

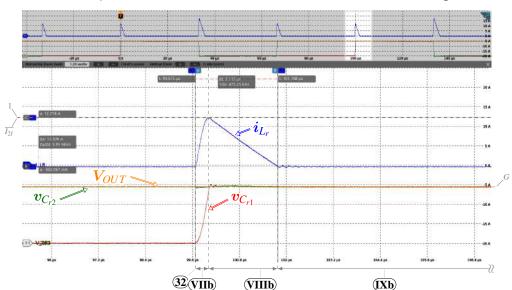

| Figure 87 – 4th to 6th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 50kHz$ based on Clock-wise PWM Sequence                                             | 140 |

| Figure 88 – 7th to 9th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 50kHz$ based on Clock-wise PWM Sequence                                             | 140 |

|                                                                                               |     |

| Figure 89 – Experimental results under $R_{OUT} = 321.4\Omega$ and $f_{SW} = 150kHz$ based on |     |

|-----------------------------------------------------------------------------------------------|-----|

| Clock-wise PWM Sequence Type                                                                  | 141 |

| Figure 90 – Experimental results under $R_{OUT} = 321.4\Omega$ and $f_{SW} = 150kHz$ based on |     |

| Counter Clock-wise PWM Sequence Type                                                          | 141 |

| Figure 91 – 1st to 2nd Topological Stage validation results under $R_{OUT}=321.4\Omega$ and   |     |

| $f_{SW} = 150kHz$ based on Clock-wise PWM Sequence                                            | 142 |

| Figure 92 – 3rd to 5th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 150kHz$ based on Clock-wise PWM Sequence                                            | 142 |

| Figure 93 – 6th to 8th Topological Stage validation results under $R_{OUT}=321.4\Omega$ and   |     |

| $f_{SW} = 150kHz$ based on Clock-wise PWM Sequence                                            | 143 |

| Figure 94 – 1st to 3rd Topological Stage validation results under $R_{OUT}=321.4\Omega$ and   |     |

| $f_{SW} = 150kHz$ based on Counter Clock-wise PWM Sequence                                    | 143 |

| Figure 95 – 4th to 5th Topological Stage validation results under $R_{OUT}=321.4\Omega$ and   |     |

| $f_{SW} = 150kHz$ based on Counter Clock-wise PWM Sequence                                    | 144 |

| Figure 96 – 6th to 8th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and |     |

| $f_{SW} = 150kHz$ based on Counter Clock-wise PWM Sequence                                    | 144 |

| Figure 97 – Experimental results under $R_{OUT} = 321.4\Omega$ and $f_{SW} = 300kHz$ based on |     |

| Clock-wise PWM Sequence Type                                                                  | 145 |

| Figure 98 – 1st to 3rd Topological Stage validation results under $R_{OUT}=321.4\Omega$ and   |     |

| $f_{SW} = 300kHz$ based on Counter Clock-wise PWM Sequence                                    | 145 |

| Figure 99 – 4th to 5th Topological Stage validation results under $R_{OUT}=321.4\Omega$ and   |     |

| $f_{SW} = 300kHz$ based on Counter Clock-wise PWM Sequence                                    | 146 |

| Figure 100–6th to 7th Topological Stage validation results under $R_{OUT} = 321.4\Omega$ and  |     |

| $f_{SW} = 300kHz$ based on Counter Clock-wise PWM Sequence                                    | 146 |

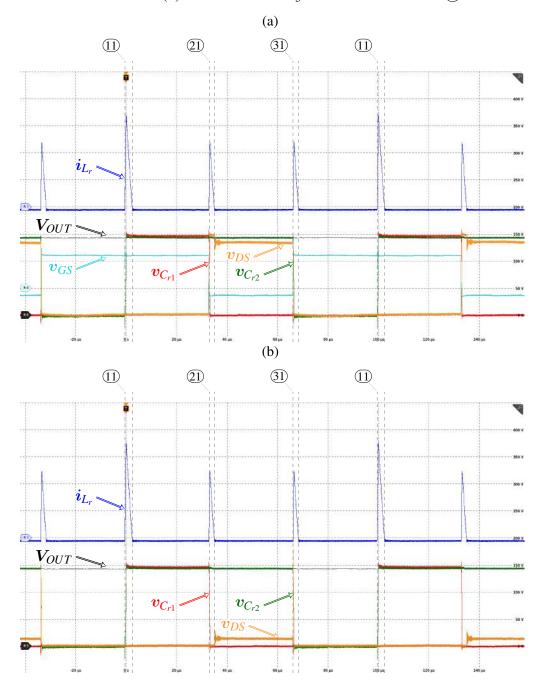

| Figure 101 – Experimental Results Comparison for two different test conditions under the      |     |

| same $\Lambda$ condition                                                                      | 147 |

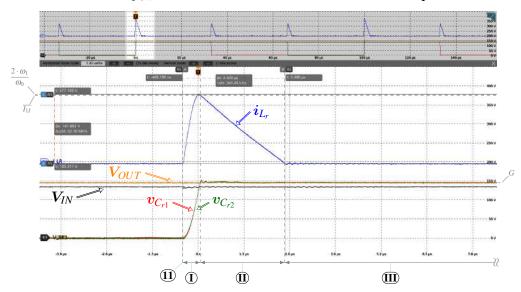

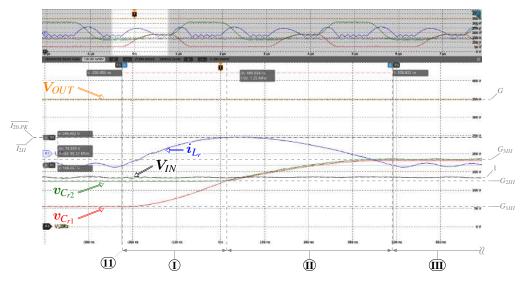

| Figure 102 – Experimental results under Test Condition (9) highlighting the Resonant State    |     |

| Variables                                                                                     | 148 |

| Figure 103-1st to 2nd Topological Stage Resonant Variables Experimental results under         |     |

| $R_{OUT} = 321.4\Omega$ and $f_{SW} = 500kHz$ based on Counter Clock-wise PWM                 |     |

| Sequence                                                                                      | 148 |

| Figure 104-4LRFLCC Equivalent Circuit upon Transition State 11 including Reverse-             |     |

| biased Diode $D_5$ 's intrisic output capacitance $C_o$                                       | 149 |

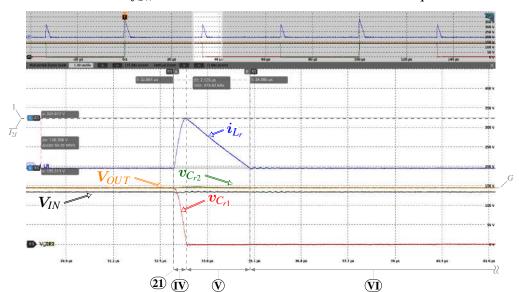

| Figure 105-3rd to 4th Topological Stage Resonant Variables Experimental results under         |     |

| $R_{OUT} = 321.4\Omega$ and $f_{SW} = 500kHz$ based on Counter Clock-wise PWM                 |     |

| Sequence                                                                                      | 149 |

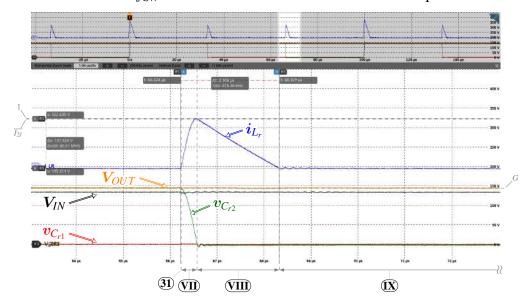

| Figure 106-5th to 6th Topological Stage Resonant Variables Experimental results under         |     |

| $R_{OUT} = 321.4\Omega$ and $f_{SW} = 500kHz$ based on Counter Clock-wise PWM                 |     |

| Sequence                                                                                      | 150 |

|                                                                                               |     |

| Figure 107 – Experimental and Theoretical results comparison for the proposed converter                                                    | 151 |

|--------------------------------------------------------------------------------------------------------------------------------------------|-----|

| within Operating Regions I to IV.                                                                                                          | 131 |

| Figure 108–Experimental results under Test Condition (10) highlighting the Resonant State Variables                                        | 151 |

| Figure 109–Experimental results under Test Condition (11) highlighting the Resonant State Variables                                        | 152 |

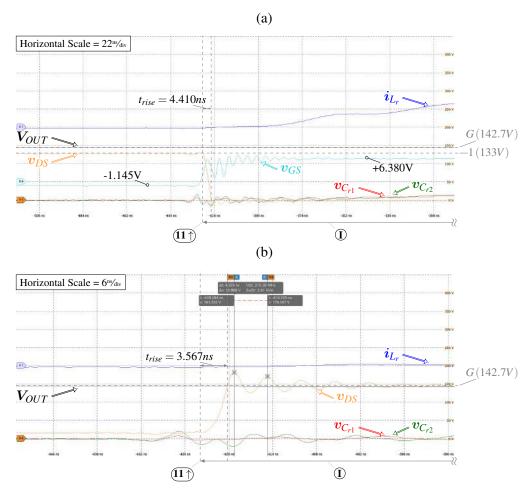

| Figure 110–Active Devices $S_1 - S_3$ High-frequency and Floating Voltage Measurement setup                                                |     |

| Figure 111 – Passive Devices $D_4 - D_6$ High-frequency and Floating Voltage Measurement setup                                             | 154 |

| Figure 112–Switch $S_1$ and $D_6$ Voltage Stresses Experimental Results within Operating Region I and Test Condition $(1)$                 |     |

| Figure 113–Switch $S_3$ and $D_4$ Voltage Stresses Experimental Results within Operating Region I and Test Condition $(1)$                 |     |

| Figure 114–Switch $S_2$ and $D_5$ Voltage Stresses Experimental Results within Operating                                                   |     |

| Region I and Test Condition $\widehat{\mathbb{1}}$                                                                                         | 157 |

| under Test Condition ①                                                                                                                     | 158 |

| under Test Condition $(1)$                                                                                                                 | 159 |

| Condition $\textcircled{1}$                                                                                                                | 159 |

| under Test Condition ①                                                                                                                     | 160 |

| under Test Condition 1                                                                                                                     | 161 |

| Condition ①                                                                                                                                | 161 |

| Figure 121 – Switch $S_2$ and $D_5$ Dynamic Voltage Behaviour upon the Transition Event $\mathfrak{A}$ under Test Condition $\mathfrak{A}$ | 162 |

| Figure 122–Switch $S_1$ and $D_6$ Dynamic Voltage Behaviour upon the Transition Event $31$ under Test Condition $1$                        | 163 |

| Figure 123 – Switch $D_5$ Dynamic voltage behaviour upon Transient Event $31$ under Test Condition $1$                                     | 164 |

| Figure 124–Switch $S_1$ and $D_6$ Voltage Stresses Experimental Results within Operating Region II and Test Condition $\textcircled{4}$    | 165 |

| Figure 125 – Switch $S_3$ and $D_4$ Voltage Stresses Experimental Results within Operating Region II and Test Condition $\textcircled{4}$  |     |

| -14-6-20 -1 min 1200 00 manual (b)                                                                                                         | 100 |

| Figure 126–Switch $S_2$ and $D_5$ Voltage Stresses Experimental Results within Operating       |     |

|------------------------------------------------------------------------------------------------|-----|

| Region II and Test Condition 4                                                                 | 167 |

| Figure 127 – Switch $S_3$ and $D_4$ Dynamic Voltage Stresses Experimental Results within       |     |

| Operating Region II and Test Condition 4 upon a Transition Event 11 1.                         | 168 |

| Figure 128-Switch $S_3$ and $D_4$ Dynamic Voltage Stresses Experimental Results within         |     |

| Operating Region II and Test Condition 4 upon the First Idle State                             | 169 |

| Figure 129-Switch $S_2$ and $D_5$ Dynamic Voltage Stresses Experimental Results within         |     |

| Operating Region II and Test Condition 4 upon the Second Idle State                            | 170 |

| Figure 130-Switch $S_1$ and $D_6$ Dynamic Voltage Stresses Experimental Results within         |     |

| Operating Region II and Test Condition 4 upon the Third Idle State                             | 171 |

| Figure 131 – Switch $S_1$ and $D_6$ Voltage Stresses Experimental Results within Operating     |     |

| Region III and Test Condition 6                                                                | 172 |

| Figure 132–Switch $S_3$ and $D_4$ Voltage Stresses Experimental Results within Operating       |     |

| Region III and Test Condition <b>6</b>                                                         | 173 |

| Figure 133 – Switch $S_2$ and $D_5$ Voltage Stresses Experimental Results within Operating     |     |

| Region I and Test Condition <b>6</b>                                                           | 174 |

| Figure 134 – Switch $S_1$ and $S_3$ Idle State's Dynamic Voltage Stresses Experimental Results |     |

| within Operating Region III and Test Condition 6                                               | 175 |

| Figure 135 – Active Switches Idle State's Dynamic Voltage Sharing Experimental Results         |     |

| within Operating Region III and Test Condition (6) during Dead-Time                            | 176 |

| Figure 136-Passive Switches Idle State's Dynamic Voltage Sharing Experimental Results          |     |

| within Operating Region III and Test Condition (6) during Dead-Time                            | 177 |

| Figure 137 – Switch Pair $S_1$ and $D_6$ Voltage Stresses Experimental Results within Operat-  |     |

| ing Region IV and Test Condition 12                                                            | 178 |

| Figure 138 – Switch Pair $S_3$ and $D_4$ Voltage Stresses Experimental Results within Operat-  |     |

| ing Region IV and Test Condition 12                                                            | 179 |

| Figure 139–Switch Pair $S_2$ and $D_5$ Voltage Stresses Experimental Results within Operat-    |     |

| ing Region I and Test Condition 12                                                             | 180 |

| Figure 140 – Switches Pair $S_3 - D_4$ Dead-time interval's Dynamic Voltage Sharing Exper-     |     |

| imental Results within Operating Region IV and Test Condition 12                               | 181 |

| Figure 141 – Switches Pair $S_1 - D_6$ Quasi-ZVS behavior Experimental Results within          |     |

| Operating Region IV and Test Condition 12                                                      | 182 |

| Figure 142–4LRFLCC Non-ideal Equivalent Circuit upon Transition State (11 †)                   | 182 |

| Figure 143–4LRFLCC Non-ideal Equivalent Circuit upon Transition State (31 †)                   | 183 |

| Figure 144–Switches Pair $S_2 - D_5$ Quasi-ZVS behavior Experimental Results within            |     |

| Operating Region IV and Test Condition 12                                                      | 183 |

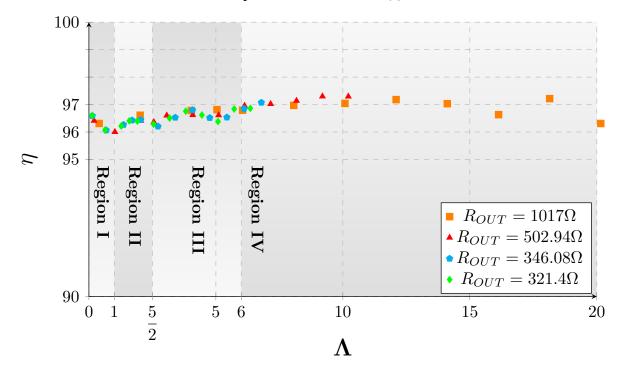

| Figure 145–500W GaN-based 4L-RFLCC Efficiency Map as a function of Λ                           | 184 |

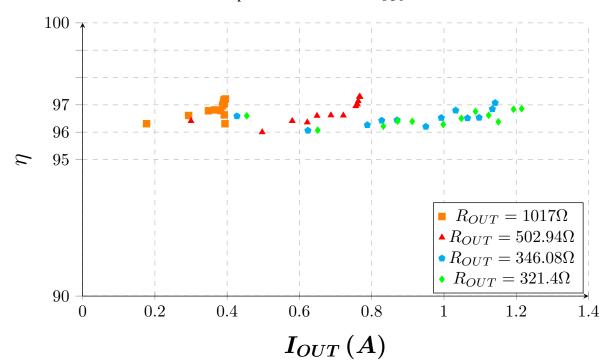

| Figure 146–500W GaN-based 4L-RFLCC Efficiency Map as a function of $I_{OUT}$                   | 185 |

|                                                                                                |     |

# LIST OF TABLES

| Table 1 –  | Summary of the different topological stages and their evolution                 | 34  |

|------------|---------------------------------------------------------------------------------|-----|

| Table 2 -  | List of Active Switches Transition Events                                       | 49  |

| Table 3 –  | Summary of the different topological stages and their characteristics for the   |     |

|            | 4LRFLC topology under Region I condition                                        | 56  |

| Table 4 –  | Summary of the different topological stages and their characteristics for the   |     |

|            | 4LRFLC topology under Region II condition                                       | 67  |

| Table 5 –  | Summary of the different topological stages and their characteristics for the   |     |

|            | 4LRFLC topology under Region III condition                                      | 76  |

| Table 6 –  | Summary of the different topological stages and their characteristics for the   |     |

|            | 4LRFLC topology under Region IV condition                                       | 84  |

| Table 7 –  | Table of Initial and Final Conditions for State Variables within Region I for   |     |

|            | Phase-Timing Definition                                                         | 87  |

| Table 8 –  | Comparison between 3L-RFLCC and 4L-RFLCC under Region I of Operating            |     |

|            | condition                                                                       | 90  |

| Table 9 –  | Summary of the distribution of maximum peak voltage and current stresses in     |     |

|            | the Switches $S_1$ - $S_6$ under Region I condition                             | 90  |

| Table 10 – | Table of Initial and Final Conditions for State Variables within Region II for  |     |

|            | Phase-Timing Definition                                                         | 91  |

| Table 11 – | Summary of the distribution of maximum peak voltage and current stresses in     |     |

|            | the Switches $S_1$ - $S_6$ under Region II condition                            | 94  |

| Table 12 – | Table of Initial and Final Conditions for State Variables within Region III for |     |

|            | Phase-Timing Definition                                                         | 95  |

| Table 13 – | Summary of the distribution of maximum peak voltage and current stresses in     |     |

|            | the Switches $S_1$ - $S_6$ under Region III condition                           | 98  |

| Table 14 – | Table of Initial and Final Conditions for State Variables within Region IV for  |     |

|            | Phase-Timing Definition                                                         | 98  |

| Table 15 – | Summary of the distribution of maximum peak voltage and current stresses in     |     |

|            | the Switches $S_1$ - $S_6$ under Region IV condition                            | 101 |

| Table 16 – | Summary of the Output Voltage Characteristic associated with Region I to        |     |

|            |                                                                                 | 101 |

| Table 17 – | Target 4LRFLCC Prototype Design Specifications                                  | 105 |

| Table 18 – | Summary of the distribution of maximum peak voltage and current stresses in     |     |

|            |                                                                                 | 109 |

| Table 19 – | 46 AWG Wire Properties utilized for the resonant inductor construction          |     |

|            | List of Inductor Magnetic core-based iteration based on the prototype target    |     |

|            | specification.                                                                  | 111 |

| Table 21 – | Resonant Capacitor's main properties for the 4L-RFLCC prototype build           |     |

| Table 22 – DC-link Capacitor's main properties for the 4L-RFLCC prototyp     | e build          | 114 |

|------------------------------------------------------------------------------|------------------|-----|

| Table 23 – Bootstrap Architecture and Component Selection for FCML com-      | verter found     |     |

| in the literature                                                            |                  | 126 |

| Table 24 – Digital Isolator and Gate Driver Architecture and Component S     | Selection for    |     |

| FCML converter found in the literature                                       |                  | 126 |

| Table 25 – Gate Driver Performance Attribute Comparison List Amongst diffe   | erent solutions. | 127 |

| Table 26 – List of Instruments for prototype testing                         |                  | 133 |

| Table 27 – List of Test Condition Sets utilized for the Operating Region     | and Output       |     |

| Voltage Regulation Validation assessment                                     |                  | 136 |

| Table 28 – Operating Region II relative voltage comparison in between Con    | unter Clock-     |     |

| wise and Clock-wise PWM Sequence type                                        |                  | 142 |

| Table 29 – Test Condition set 6 Static Resonant Variables Comparison in be   | tween Theo-      |     |

| retical and Experimental Results                                             |                  | 143 |

| Table 30 – Test Condition set 7 and 8 Static Resonant Variables Comparison   | n in between     |     |

| Theoretical and Experimental Results under the same $\Lambda$ condition      | n                | 146 |

| Table 31 – Test Condition set (9) Static Resonant Variables Comparison in be | tween Theo-      |     |

| retical and Experimental Results                                             |                  | 150 |

| Table 32 – Test Condition set 10 and 11 Static Resonant Variables Con        | mparison in      |     |

| between Theoretical and Experimental Results within Operating                | Region IV        | 152 |

|                                                                              |                  |     |

# LIST OF ABBREVIATIONS AND ACRONYMS

AWG American Wire Gauge

CCM Continuous Conduction Mode

CMRR Common-mode Rejection Ratio

DC Direct-Current

DCM Discontinuous Conduction Mode

ESL Equivalent Series Inductance

ESR Equivalent Series Resistance

FCML Flying-Capacitor Multi-level

FLCCC Flying-Capacitor Commutation Cell

FOM Figure of Merit

FSL Fast-Switching Limit

GaN Gallium Nitride

GD Gate Driver

HSW Hard-Switching

IC Integrated-Chip

IGBT Insulated-gate Bipolar Transistor

KVL Kirchhoff's Voltage Law

LV Low Voltage

MLCC Multilayer Ceramic Capacitor

MOSFET Metal Oxide Semiconductor Field Effect Transistor

MV Mega Voltage

PWM Pulse-width Modulation

ReSC Resonant Switched-Capacitor

RFLCC Resonant Flying-Capacitor Converter

SC Switched-Capacitor

Si Silicon

SiC Silicon Carbide

SSL Slow-Switching Limit

SSW Soft-Switching

WBG Wide-band Gap

ZCS Zero-Current Switching

ZVS Zero-Voltage Switching

2L Two-level

3L Three-level

3L-RFLCC Three-level Resonant Flying-Capacitor Converter

4L Four-level

4L-RFLCC Four-level Resonant Flying-Capacitor Converter

# LIST OF SYMBOLS

N Number of levels associated with a multi-level converter topology

$A_e$  Effective Core Area

$a_x$  Ellipse Major-axis total length

$B_s$  Magnetic B field

$b_x$  Ellipse Minor-axis total length

$C_{ds}$  Drain-to-Source Capacitor/Capacitance

$C_{fly}$  Flying Capacitor/Capacitance

$C_{gd}$  Gate-to-Drain Capacitor/Capacitance

$C_{gs}$  Gate-to-Source Capacitor/Capacitance

C<sub>IO</sub> Input-Output Equivalent Capacitance

Ciss FET's Equivalent intrisic input capacitance

$C_{oss}$  FET's Equivalent intrisic output capacitance

$C_{oss,O}$  Charge-related Equivalent output capacitance

*C<sub>OUT</sub>* Output Capacitor/Capacitance

*Cout* Switches' intrisic Output Equivalent Capacitance

*C<sub>o.Diode</sub>* Diode's Equivalent Output Capacitance

$C_{o,FET}$  FET's Equivalent Output Capacitance

*C<sub>r</sub>* Resonant Flying Capacitor/Capacitance

$C_{r,eq}$  Equivalent Resonant Flying Capacitor/Capacitance

$C_x$  Circle Center coordinate value

D Duty Cycle

$\delta$  Skin-depth

$E_{oss}$ 's stored energy as a function of v

$L_d$  Drain Inductor/Inductance

$L_{d_{DCR}}$  Drain PCB Parasitic Inductor/Inductance

$L_g$  Gate Inductor/Inductance

$L_{G_{PCR}}$  Gate-Loop PCB Parasitic Inductor/Inductance

$L_{ks}$  Kelvin-Source Inductor/Inductance

*L<sub>PCB</sub>* PCB Parasitic Inductor/Inductance

$L_{prototype}$  Measured Resonant inductor/inductance value

| $L_r$                                            | Resonant Inductor/Inductance                                                                                  |

|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------|

| $L_s$                                            | Power-Source Inductor/Inductance                                                                              |

| $L_{^{SPCB}}$                                    | Power-Source PCB Parasitic Inductor/Inductance                                                                |

| $f_{SW}$                                         | Switching Frequency in Hz                                                                                     |

| $f_0$                                            | $Z_r$ -related Resonant Frequency in Hz                                                                       |

| $I_{C0}$                                         | Capacitor's Initial Current Condition in Amps                                                                 |

| $i_{C_{fly}}(t)$                                 | Instantaneous Flying-capacitor's current value                                                                |

| $i_{C_r}(t)$                                     | Instantaneous Resonant Flying-capacitor's current value                                                       |

| $\overline{i_{C_r}(t)}$                          | Normalized Instantaneous Resonant Flying-capacitor's voltage value in reference to $\frac{Z_r}{V_{IN}}$ .     |

| $\overline{i_{C_r}(t)}$                          | Normalized Instantaneous Resonant Flying-capacitor's voltage value in reference to $\frac{Z_{r_2}}{V_{IN}}$ . |

| $\overline{\overline{i_{C_r}(t)}}$               | Normalized Instantaneous Resonant Flying-capacitor's voltage value in reference to $\frac{Z_{r_1}}{V_{IN}}$ . |

| $MAX\left(\overline{I_{C_{r_n}}}\right)$         | Maximum Resonant Capacitor n's peak current value                                                             |

| $i_{L_{r}}\left( t ight)$                        | Instantaneous Resonant Inductor's current value                                                               |

| $\overline{i_{L_{r}}\left( t ight) }$            | Normalized Instantaneous Resonant Inductor's voltage value in reference to $\frac{Z_r}{V_{IN}}$ .             |

| $\overline{i_{L_{r}}\left( t ight) }$            | Normalized Instantaneous Resonant Inductor's voltage value in reference to $\frac{Z_{r_2}}{V_{IN}}$ .         |

| $\overline{\overline{i_{L_{r}}\left( t ight) }}$ | Normalized Instantaneous Resonant Inductor's voltage value in reference to $\frac{Z_{r_1}}{V_{IN}}$ .         |

| $I_{IN}$                                         | Average Input current value                                                                                   |

| $i_{OUT}\left(t ight)$                           | Instantaneous Output load current value                                                                       |

| $I_{OUT}$                                        | Average Output load current value                                                                             |

| $I_p$                                            | Peak Current thru the Magnetic component                                                                      |

| $I_1$                                            | Hard-switched Switching Current value                                                                         |

| $\mu_r$                                          | Material relative magnetic permeability                                                                       |

| $\omega_0$                                       | $Z_r$ -related Resonant Velocity in $\frac{rad}{s}$                                                           |

| $\omega_1$                                       | $Z_{r_1}$ -related Resonant Velocity in $\frac{rad}{s}$                                                       |

$\omega_2$   $Z_{r_2}$ -related Resonant Velocity in  $\frac{rad}{s}$

*P*<sub>DRV</sub> Total Gate-related Power consumption

$P_{dt}$  Dead-time-related conduction loss

$P_G$  Gate  $C_{iss}$  loss

$P_{oss}$  Output-capacitance  $C_{oss}$  loss

$P_{rr}$  Reverse-recovery loss

$P_{vi}$  Voltage-Current Overlap-related loss

$Q_C$  Diode's Capacitive Charge

$Q_{GD.tot}$  Total Gate Charge

$Q_{oss}$   $C_{oss}$ 's stored charge as a function of v

$R_{OUT}$  Output Load Impedance/Resistance in  $\Omega$

$R_{ON}$  Device's ON-resistance

$r_x$  Circle radius value

ρ Material conductivity coefficient

$S_x$  Switch

$T_i$  Junction Temperature

$\Delta T_{XYZ}$  Interval's Time duration from **Y** to **X** within Operating Condition **Z**

$au_{rr}$  Reverse-recovery-related coefficient

$V_{C0}$  Capacitor's Initial Voltage Condition in Volts

$v_{C_{flv}}(t)$  Instantaneous Flying-capacitor's voltage value

$v_{C_r}(t)$  Instantaneous Resonant Flying-capacitor's voltage value

$\overline{v_{C_r}(t)}$  Normalized Instantaneous Resonant Flying-capacitor's voltage value in

reference to  $V_{IN}$ .

$MAX(\overline{V_{C_{r_n}}})$  Maximum Resonant Capacitor **n**'s peak voltage value

$V_{DRV}$  Gate Driver Voltage

$V_{DM}$  DC Differential Voltage in reference to  $V_1$  and  $V_2$  in Volts

$V_{DS}$  Drain-to-Source Voltage

$V_F$  Diode's Forward Voltage Drop

$V_{GS,OFF}$  Turn-OFF Gate-to-Source Voltage

$v_{L_r}(t)$  Instantaneous Resonant Inductor's voltage value

*v<sub>IN</sub>* Input Voltage in Volts

*v<sub>OUT</sub>* Output Voltage in Volts

$V_{SD}$  Reverse conduction Source-to-Drain Voltage Drop

$V_1$  DC Plus-Differential Voltage in Volts

V<sub>2</sub> DC Minus-Differential Voltage in Volts

$Z_r$  Characteristic Impedance

# **CONTENTS**

| 1      | INTRODUCTION 2                          | 6  |

|--------|-----------------------------------------|----|

| 1.1    | CONTEXTUALIZATION AND LITERATURE REVIEW | 6  |

| 1.2    | MOTIVATION                              | 3  |

| 1.2.1  | Operation Principle                     | 3  |

| 1.2.2  | Thesis Outline                          | 5  |

| 2      | LC-NETWORK GENERAL DESCRIPTION          | 7  |

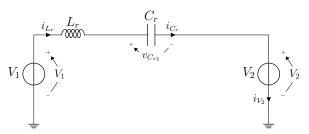

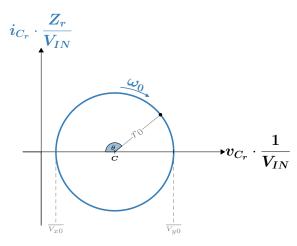

| 2.1    | CASE 1 - LC SERIES RESONANCE            | 7  |

| 2.2    | CASE 2 - LCCP SERIES RESONANCE          | 0  |

| 2.3    | CASE 3 - LCCS SERIES RESONANCE          | 4  |

| 3      | 4L-RFLC BOOST CONVERTER DESCRIPTION 4   | 8  |

| 3.1    | MODULATION STRATEGY                     | 8  |

| 3.2    | REGION I                                | 9  |

| 3.2.1  | <b>Interval I</b> $(t_0 < t < t_1)$     | 9  |

| 3.2.2  | <b>Interval II</b> $(t_1 < t < t_2)$    | 1  |

| 3.2.3  | <b>Interval III</b> $(t_2 < t < t_3)$   | 2  |

| 3.2.4  | <b>Interval IV</b> $(t_3 < t < t_4)$    | 2  |

| 3.2.5  | <b>Interval V</b> $(t_4 < t < t_5)$     | 3  |

| 3.2.6  | <b>Interval VI</b> $(t_5 < t < t_6)$    | 4  |

| 3.2.7  | <b>Interval VII</b> $(t_6 < t < t_7)$   | 4  |

| 3.2.8  | <b>Interval VIII</b> $(t_7 < t < t_8)$  | 5  |

| 3.2.9  | <b>Interval IX</b> $(t_8 < t < t_9)$    | 6  |

| 3.2.10 | Summary of Operation                    | 6  |

| 3.3    | REGION II                               | 8  |

| 3.3.1  | <b>Interval I</b> $(t_0 < t < t_1)$     | 8  |

| 3.3.2  | <b>Interval II</b> $(t_1 < t < t_2)$    | 0  |

| 3.3.3  | <b>Interval III</b> $(t_2 < t < t_3)$   | 0  |

| 3.3.4  | <b>Interval IV</b> $(t_3 < t < t_4)$    | 2  |

| 3.3.5  | <b>Interval V</b> $(t_4 < t < t_5)$     | 3  |

| 3.3.6  | <b>Interval VI</b> $(t_5 < t < t_6)$    | 4  |

| 3.3.7  | <b>Interval VII</b> $(t_6 < t < t_7)$   | 5  |

| 3.3.8  | <b>Interval VIII</b> $(t_7 < t < t_8)$  | 7  |

| 3.3.9  | Summary of Operation                    | 7  |

| 3.4    | REGION III                              | 9  |

| 3.4.1  | <b>Interval I</b> $(t_0 < t < t_1)$     | 9  |

| 3.4.2  | Interval II $(t_1 < t < t_2)$           | 'n |

| 3.4.3 | Interval III $(t_2 < t < t_3)$                                            |

|-------|---------------------------------------------------------------------------|

| 3.4.4 | <b>Interval IV</b> $(t_3 < t < t_4)$                                      |

| 3.4.5 | Interval V $(t_4 < t < t_5)$                                              |

| 3.4.6 | Interval VI $(t_5 < t < t_6)$                                             |

| 3.4.7 | Interval VII $(t_6 < t < t_7)$                                            |

| 3.4.8 | <b>Summary of Operation</b>                                               |

| 3.5   | REGION IV                                                                 |

| 3.5.1 | Interval I $(t_0 < t < t_1)$                                              |

| 3.5.2 | Interval II $(t_1 < t < t_2)$                                             |

| 3.5.3 | <b>Interval III</b> $(t_2 < t < t_3)$                                     |

| 3.5.4 | <b>Interval IV</b> $(t_3 < t < t_4)$                                      |

| 3.5.5 | Interval V $(t_4 < t < t_5)$                                              |

| 3.5.6 | <b>Interval VI</b> $(t_5 < t < t_6)$                                      |

| 3.5.7 | Summary of Operation                                                      |

| 4     | STATIC GAIN & LARGE-SIGNAL ANALYSIS 86                                    |

| 4.0.1 | Region I                                                                  |

| 4.0.2 | Region II                                                                 |

| 4.0.3 | Region III                                                                |

| 4.0.4 | Region IV                                                                 |

| 4.0.5 | Large-Signal Analysis Summary                                             |

| 5     | PROTOTYPE DESIGN & COMPONENT SELECTION 105                                |

| 5.0.1 | Project Specification & Design Methodology                                |

| 5.0.2 | Component Stresses                                                        |

| 5.0.3 | Resonant inductor $L_r$                                                   |

| 5.0.4 | Resonant flying capacitors $C_{r1}$ and $C_{r2}$ & DC-link Capacitors 111 |

| 5.0.5 | <b>Active Switches</b> $S_1 - S_6$                                        |

| 5.0.6 | Gate Driver & Auxiliary Circuitries                                       |

| 5.0.7 | PCB Design                                                                |

| 6     | EXPERIMENTAL RESULTS AND VALIDATION                                       |

| 6.0.1 | Operating Region & Output Voltage Regulation                              |

| 6.0.2 | Switches $S_1 - S_6$ 's Voltage Stresses                                  |

| 6.0.3 | Efficiency Map                                                            |

| 7     | CONCLUSIONS                                                               |

|       | BIBLIOGRAPHY                                                              |

# 1 INTRODUCTION

# 1.1 CONTEXTUALIZATION AND LITERATURE REVIEW

DC-DC Step-up and Step-down power conversion have been extensively utilized over the years in a broad range of applications from DC distribution networks [Zhang et al. 2016], where voltages are required to step-down from MV to LV (400V or 380V) levels, to renewable energy system, to lower voltage applications such as datacenters and telecommunication [Ye, Lei e Pilawa-Podgurski 2018] and low-voltage digital circuitry [Pilawa-Podgurski, Giuliano e Perreault 2008] [Pilawa-Podgurski e Perreault 2012], where the conversion ratio and output current requirements are usually high. As a consequence, high efficiency and high power density converters become important in order to achieve a high level of sustainability.

In order to fulfill such requirements, either multi-stage conversion have been widely employed, in order to overcome the poor performance of conventional buck-like or boost-like converters operating with a large conversion ratio, or isolated DC-DC converters, due to their ability of increasing the conversion ratio based on a magnetically coupling component to support the large conversion ratio [Zhang et al. 2016] [Vasic et al. 2019]. Even though multi-stage conversion architectures can potentially achieve good levels of power density and compactness [Vasic et al. 2019], the additional stages generally require bulky energy storage elements either to provide the intermediate voltage stabilization or to support the conversion such as a conventional 2L buck-like or boost-like converter's Volt-Second balance in an inductor.

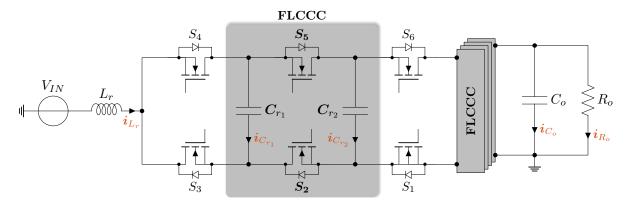

Due to these distinct conditions, multilevel converters have been addressed in order to optimize the system's performance due to its ability to deliver a higher conversion ratio, lower Volt-Second balance in inductors, in case of magnetic-type converter, as well as the feasibility to utilize lower voltage switches [Brooks et al. 2022] which leads to better figure-of-merits (FoM) compared to high voltage switches. Amongst the different structures that are defined as multilevel converters, Switched-capacitor converters, as shown in Figure 1, have been widely utilized due to their key benefits such as the magnetic-less characteristic and possibility to fulfill a particular fixed voltage gain requirement in comparison to their natural counter-parts such as conventional buck or boost converters. Such characteristics generally lead to higher power density and small component count. On the other hand, due to the magnetic-less characteristic, large current spikes are experienced due to the charging/discharging process of the intermediate capacitors [Shoyama, Naka e Ninomiya 2004] and, consequently, lower efficiency is achievable. Therefore, such topology becomes limited to lower output current and/or lower input voltage applications. The Switched-capacitor converter types, shown in Figure 1, can be expanded to N levels, which leads to a higher output voltage gain. However, their applicability has practical limits in order to introduce a N voltage gain due to the input current flowing through N switching devices. As a consequence, introducing further losses and reducing the efficiency.

Different switched-capacitor topologies have been introduced such as the Ladder-type, Dickson, Fibonacci, Series-Parallel and Doubler. Each of these topologies have its benefits and

Figure 1 – Representation of the Base form of different DC-DC Switched-Capacitor, such as: (a) Ladder SC Converter. (b) Dickson SC Converter. (c) Fibonacci SC Converter.

drawbacks. The ladder-type, as shown in Figure 1a, is based on a set of capacitors establishing the DC potentials referred to the ground reference and a set of capacitors establishing the equalization amongst the DC-referenced capacitors [Seeman 2009]. The basic pulse-width modulation strategy is by driving the odd-numbered switches complementary to the even-numbered switches. The ladder-type is also suitable for non-integer voltage gains based on the position of the input voltage connection with reference to the ground. As a consequence, depending on the number of levels, the low-side components are the most stressed whereas the high-side devices are locally stressed based on the charging and discharging process. This behaviour leads to an unbalance in the current stresses making it not well suitable for high conversion ratio and high current applications.

In order to improve the unbalance in the current stresses, shown in the Ladder-type SC converter, the Dickson SC converter has been introduced, as shown in Figure 1b, by introducing phase-shifted ladder commutation cells. Therefore, by driving the two low-side bridge-legs

complementary as well as the high-side switches in a similar fashion as in the Ladder-type, the current stresses in the low-side switches are distributed accordingly whereas the current stresses in the high-side switches remain the same as shown in the Ladder-type SC converter. As a consequence, the Dickson SC converter becomes more suitable for slightly higher conversion ratio and higher current and applications. On the other hand, by introducing the phase-shifted ladder, the voltage stresses in the flying capacitors are no longer equal due to the phase-shifted ladder connection point; thus, leading to an unbalance in the voltage stresses in the switches during the OFF-state.

Alternatively, the Fibonacci SC converter has been introduced, as shown in Figure 1c, by applying cascaded three switches and 1 flying capacitor commutation cell. Differently from the other SC converters, the conversion ratio is given by the Fibonacci sequence. Therefore, a higher conversion ratio is achieved on a smaller component count compared to the Ladder and Dickson SC converters. As a consequence, higher efficiencies are achieved. On the other hand, similarly to the Ladder SC converter and the Dickson SC converter, there exist a progressive unbalance in the current stresses for the switches, based on the commutation cell position, and a unbalance in the voltage stresses in the active switches and passive components, respectively.

Driven by the main characteristics for each SC converter, [Seeman 2009] [Seeman e Sanders 2008] derives the Slow-Switching Limit (SSL) and Fast-Switching Limit (FSL) impedance analysis in order to compare the different topologies based upon the capacitive energy losses and the resistive elements energy losses, respectively.

Due to the excessive forced charging and discharging process, there exist an inherent drawback on the losses introduced by the switched capacitors as well as increase the device stresses [Lei e Pilawa-Podgurski 2015]. Thus, the efficiency becomes limited regardless of the internal resistance minimization [Shoyama, Naka e Ninomiya 2004] [Shoyama, Deriha e Ninomiya 2005]. Additionally, due to its hard-switched pulse-width modulation operation, it introduces further limitations in terms of high-frequency applications by increasing the switching losses [Li et al. 2017] and causing undesirable electromagnetic interference problems, which are solved by either increasing the switching frequency or employing larger switched capacitors [Lei e Pilawa-Podgurski 2015].

In order to reduce the current stresses and the forced charging/discharging process energy losses, an additional inductive element is introduced with the capacity of limiting the charging and discharging current of the intermediate capacitors, Such structure is named Hybrid Switched-capacitor converter. Thus, potentially increasing the converter's efficiency. Additionally, it also introduces the possibility of regulating the voltage gain, releasing the pressure of the input voltage requirement in order to fulfill a particular output voltage. However, the introduction of the inductive element naturally decreases the power density, becoming less suitable for high power density applications. Resonant switched-capacitor converters, as shown in Figure 2, have been a research interest due to its benefits such as high power-density and soft-switching capability while delivering a constant voltage gain and limiting the main drawback of conventional switched-

capacitor converter.

Figure 2 – Representation of different approaches for the realization of resonant switched-capacitor converter (ReSCC).

The resonant type employs small inductors and capacitors, in opposition to the bulky intermediate capacitors employed in conventional switched-capacitor converters, due to the voltage mismatching in between the intermediate capacitors being present across the inductors instead of the internal resistance of the active switches [Ye, Lei e Pilawa-Podgurski 2020]. Thus, enabling the utilization of smaller capacitors and bigger voltage ripples without sacrificing the system's efficiency. The small inductor and capacitor create a resonant behaviour based on the Active switches' status. As a consequence, the charging/discharging process is based on the resonance frequency and soft-switching can be achieved by exploring the switching frequency control as well as the phase-shift [Setiadi e Fujita 2016] [Sano e Fujita 2011] mechanism based on the modulation strategy employed by the converter.

Due to the limited voltage gain characteristic, additional conversion stages [Ye, Lei e Pilawa-Podgurski 2020] [Ye, Lei e Pilawa-Podgurski 2018] can be introduced in order to increase the voltage gain. The cascaded stages employ basic 2:1 switched-capacitor converter in series in order to achieve the desired output voltage gain. The main benefit is the simple resonant activity, due to the individual stages operation. On the other hand, this strategy leads to incremental voltage stresses in the upstream cascade converters and the utilization of intermediate bus capacitors in order to decouple the resonance in between the adjacent cascaded converters.

Different cascaded topologies [Lei e Pilawa-Podgurski 2015] explore the characteristics of switched-capacitor converter followed by conventional buck converters [Pilawa-Podgurski, Giuliano e Perreault 2008] with high switching frequency and high bandwidth due to its output current characteristic which then eliminates the need of bulky bus capacitors. Therefore, these architectures can be considered as merged-cascaded stages and improves the power density of the power conversion stage. Many different authors have explored the basic switched-capacitor architectures in order to reduce the components' stresses as well as the component count.

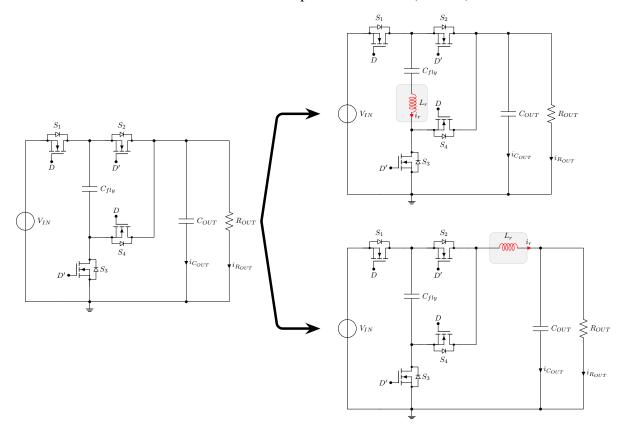

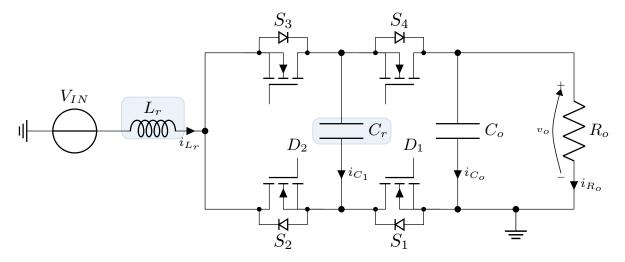

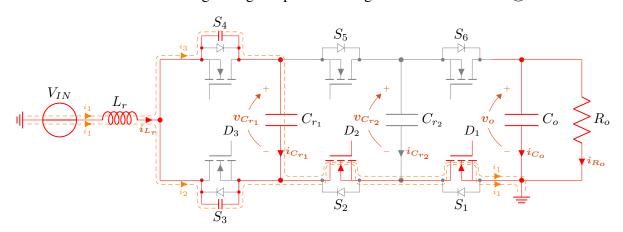

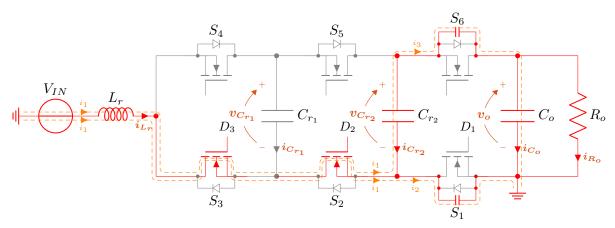

Alternatively, the flying capacitor multilevel converter, as shown in Figure 3, has also become attractive for similar applications, due to its component stresses' characteristics as well as its ability to regulate the output voltage. Likewise the switched-capacitor topologies, the flying capacitor topology can also be operated in resonant mode. Thus, bringing the similar benefits as discussed previously.

Figure 3 – Basic Structure for a 3L flying capacitor boost DC-DC converter.

Cascaded topologies have also been addressed in resonant mode [Ye, Lei e Pilawa-Podgurski 2018], and also where the essence is to minimize the resonant tank design complexity, as demonstrated by [Liu, Ge e Pilawa-Podgurski 2022], in which the resultant energy transfer is based on an interaction in between the two adjacent stages. Due to that, the filter, in between the stages, can be simplified, in comparison to [Ye, Lei e Pilawa-Podgurski 2018] where the intermediate filter is required to sustain an intermediate voltage level for the adjacent conversion stage. Alternatively, cascaded topologies have been explored with virtual intermediate voltage buses [Chen et al. 2022] [Zhu et al. 2024], where the first stage is essentially a switched capacitor, employing the conventional hard-charging mechanism as observed in non-resonant switched-capacitor converters, whereas [Ge, Ye e Pilawa-Podgurski 2023] addresses a similar mechanism except that the virtual intermediate bus is converted into a switching virtual bus, in which the advantages become the small-sized bus, the ability to increase the step-down conversion ratio, and the opportunity of exploring the virtual bus as part of the resonant energy-transfer mechanism in the adjacent conversion stage. As a consequence, the cascaded total resonant tank is greatly

reduced. On the other hand, due to the primary-stage's charge-pump behavior, there exist a high-current stresses in order to enable the switching bus mechanism.

The ability of the above-mentioned converters to greatly increase the power density is also driven by the passive components volume given the objective of defining the characteristic impedance to balance, and optimize, the energy utilization of the resonant tank components, such as the resonant inductor and resonant capacitor [Ye, Sanders e Pilawa-Podgurski 2019] [Ellis et al. 2024]. [Ye, Sanders e Pilawa-Podgurski 2019] addresses this issue by defining the energy utilization and comparing the characteristic impedance of different switched capacitors, operating in resonant mode, amongst which the FCML is further analyzed. By utilizing the energy processed by the capacitor and the inductor, the energy utilization refers to the amount of energy transfer per peak energy. In other words, it addresses the total voltage ripple, and current ripple, within the resonant capacitor and resonant inductor, respectively. From a different perspective, [Zhu, Ye e Pilawa-Podgurski 2024] addresses the switched-capacitor performance based on finite input and output capacitances. It expands the SSL and FSL by considering the impact of the charge/discharge of the output and input capacitors as a forced charging/discharging process in which it has been found that the capacitance ratio with respect to the flying capacitor impacts the performance, leading to a higher bus capacitance total volume requirements. The same analysis has not been performed for resonant-type converters. However, it could be expected the interference of the input and output capacitor into the conversion ratio, as well as in the ability of soft-switching, due to the higher sensibility of the operating mechanism as a result of a shift in the resonant frequency.

On the contrary, [Abramson et al. 2022] [Brooks et al. 2022] define a conduction mode factor, which describes the converter's operating condition with respect to the fundamental switching frequency and the resultant resonance frequency given the number of FLCCC stages, in order to derive an optimization function based on the conduction mode. The analysis focus on operations at and above resonance, where the converter operates either synchronously with the switching frequency; thus, achieving ZCS at every Switches State Transition; or intentionally increasing the conduction mode factor in order to reduce the current stresses, while retaining the resonant behavior within each FLCCC. The later leads to non-ZCS, introducing switching losses at the turn-OFF and turn-ON transition of the complementary switches. Based on the conduction mode factor, the charge associated with each flying capacitor is derived, exhibiting an optimum operating condition, where the conduction losses and switching losses are balanced. Although ZVS cannot be achieved for every Switch, a ZVS cross-conduction time is introduced [Ge et al. 2021] [Ge, Ye e Pilawa-Podgurski 2023] in order to achieve ZVS, where every Low-side Switches are simultaneously ON, imposing a high negative voltage across the inductor. As a result, the inductor's current falls linearly during this phase and introduces a ZCS for the complementary High-side Switches, greatly improving the converter's performance. Similarly, the Low-side Switches can also achieve by sufficiently increasing the inductor's current above zero. Yet, the non-ZVS Switches achieve ZCS, which is beneficial for high-current applications [Ge, Ye e

Pilawa-Podgurski 2023], despite of the  $C_{out}$ -associated losses.

Operating under resonance leads to ZCS for every Switch. However, it inhibits the ZVS transition and the associated  $C_{out}$  losses, possibly imposing limitation to the system's operating frequency. Yet, depending on the number of FLCCC, the switching voltage becomes small, leading to an acceptable  $C_{out}$  loss figures. Low-voltage applications, as demonstrated in the various papers above-mentioned, the  $C_{out}$  losses may not be very critical, instead, the high-current requirements becomes important, where Si MOSFETs remain competitive. For high-voltage applications,  $C_{out}$  losses are non-negligible and WBG devices introduces a degree of freedom in order to keep pushing the boundaries of power density by increasing the operating frequency and minimizing the resonant tank volume.

The majority of the past, and recent, work have explored the flying capacitor resonant converter as a non-regulated step-up or step-down converter with a given characteristic of constant voltage gain under the right operating conditions, such as the high characteristic impedance. Such characteristic leads to a constant voltage gain under a very wide load range, with the cost of having a larger resonant tank, becoming suitable for many different applications. Similarly, the same topology has been explored as a voltage gain multiplier/divider as a result of specific PWM strategies.

Due to the sinusoidal shape, the frequency-dependent state variables' description, which enables the optimization objects described previously, becomes more complex. Recent works have explored different methods of analytically solving for the unknown variables. [Ellis et al. 2024] [Ye, Sanders e Pilawa-Podgurski 2019] exploits the energy processed, in which [Ellis et al. 2024] [Brooks et al. 2022] emphasizes the conduction timings per phase as a consequence of the multi-resonance characteristic. The description aids the phase timings in order to accurately change the Switches State in order to fulfill the output requirements. The only drawback is the RFLCC operating condition, which is focused on either at resonance or above resonance, leading to a simplified frequency-dependent unknown variables, where the sinusoidal shape exhibits a symmetrical behavior in terms of initial and final condition within each phase. Similarly, [Ellis e Amirtharajah 2022] addresses the phase timings, for a Dickson-type switched-capacitor converter, in order to maintain a zero voltage-seconds across the inductor, based on the Kirchhoff's Voltage Law (KVL) for each topological stage where an average and ripple voltage level are considered as unknown variables. Based on the charge transfer, the unknown variables can be analytically solved.

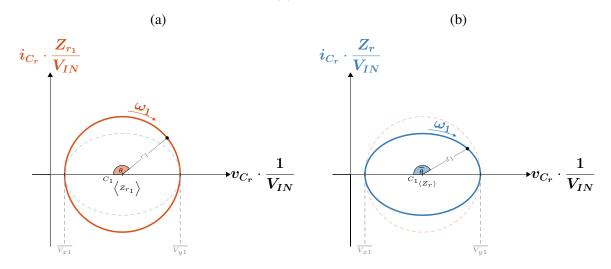

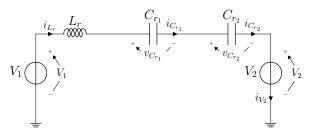

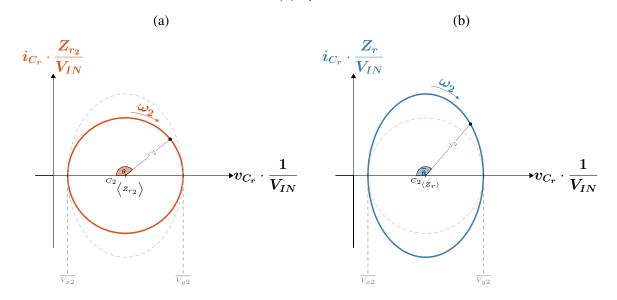

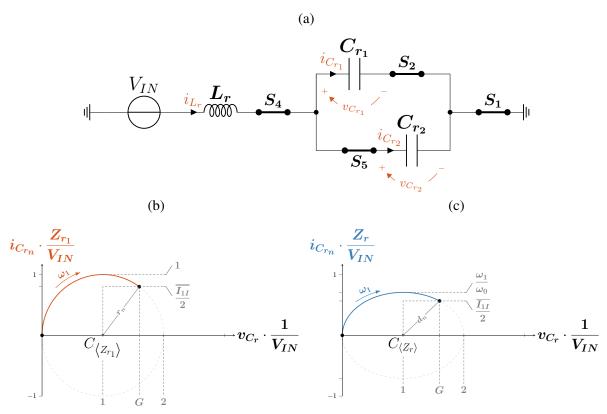

Alternatively, due to the sinusoidal shape, a geometrical representation exhibits an advantage over purely analytical solutions due to the possibility of representing the sinusoidal shape by geometrical forms, such as circles and ellipses, and exploring the geometry rules. [Oruganti e Lee 1985] pioneered the State Plane Analysis, which became very popular specially for LLC converter application [Feng, Lee e Mattavelli 2013] [Vuchev e Grigorova 2021] [Rezayati et al. 2022] due to the possibility of increasing the output voltage regulation's bandwidth despite of the increased mathematical computational power demand. The same approach is taken in

non-isolated resonant converters [Shuai et al. 2010] [Setiadi e Fujita 2016] for a single LC resonant network. The resultant representation exhibits a circular trajectory, leading to a very comprehensive analysis with explicit radius and center to aid with the problem solving. [Setiadi e Fujita 2016] demonstrates the phase timing determination, which results in a similar result as described in [Ellis et al. 2024]. However, the approach, shown in [Setiadi e Fujita 2016], is limited due to the single LC resonant network and simple description, lacking the coverage to multi-resonant converters.

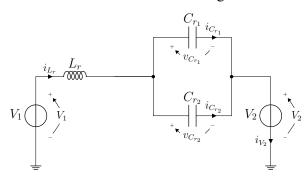

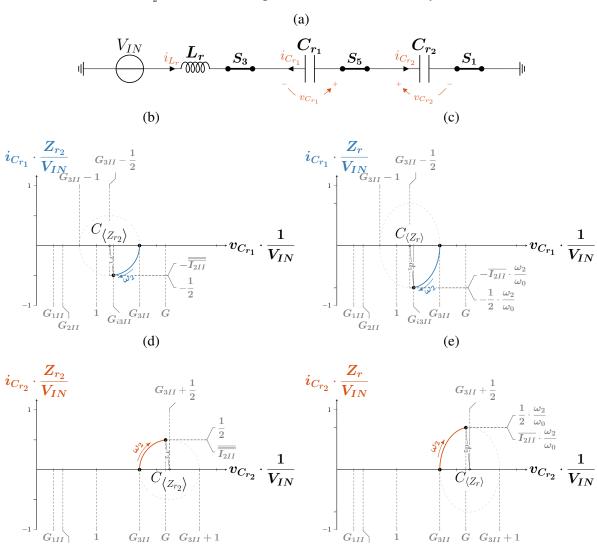

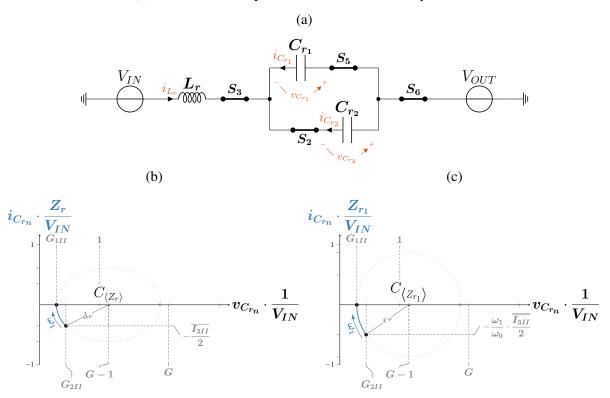

The multi-resonant characteristic introduces further complexity in the geometrical representation. As demonstrated in [Ge, Ye e Pilawa-Podgurski 2023], multiple interconnection amongst different passive elements possesses challenges by introducing different geometrical forms. As a consequence, [Ge, Ye e Pilawa-Podgurski 2023] suggests the individual representation, under each equivalent resonant tank framework, and the topological stages link as per the equilibrium states. As a consequence, it avoids the utilization of elliptical geometries as part of the problem solving.

#### 1.2 MOTIVATION

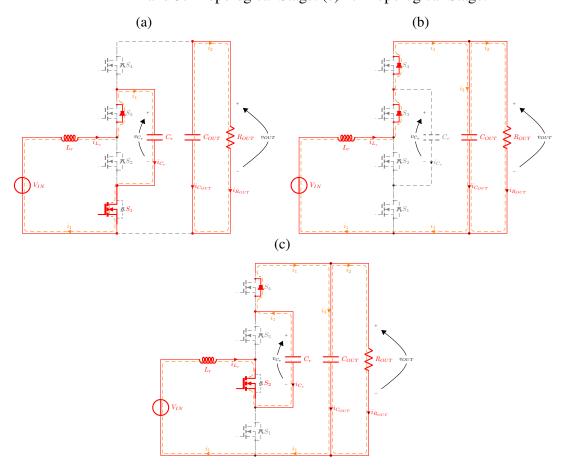

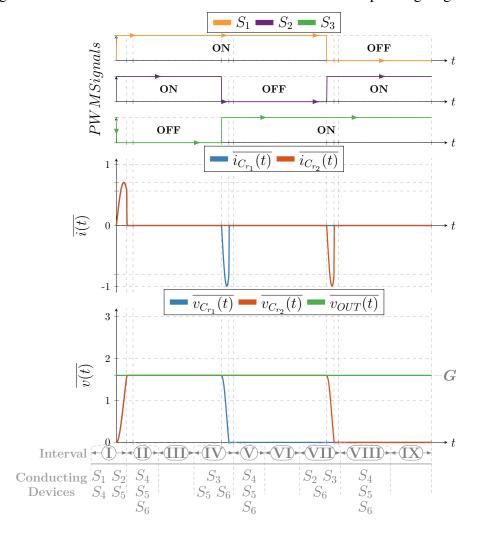

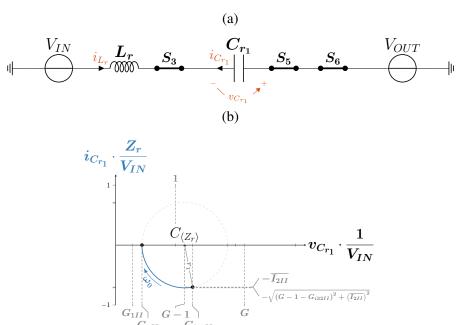

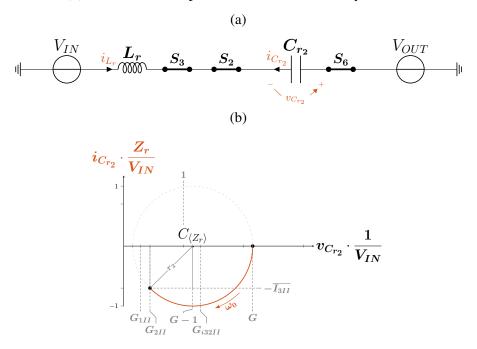

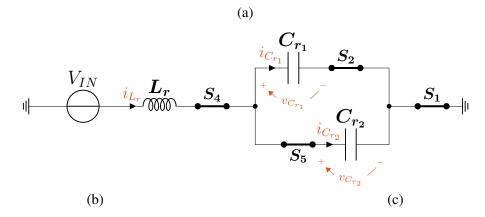

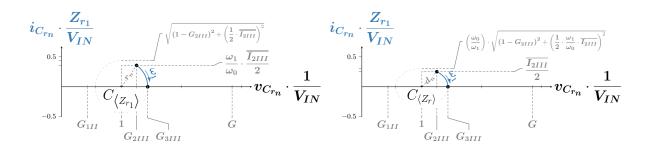

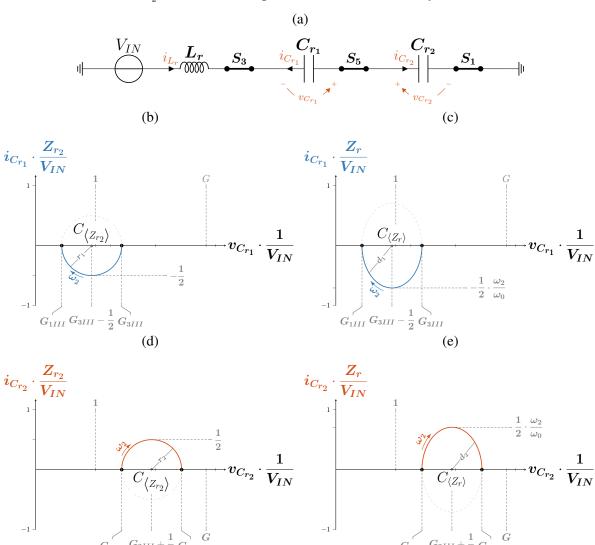

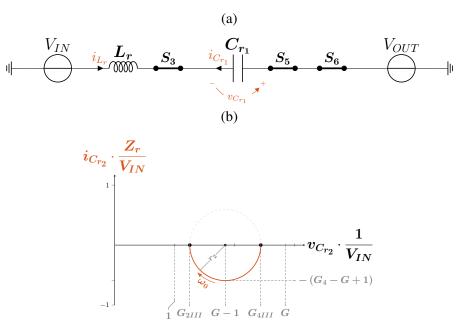

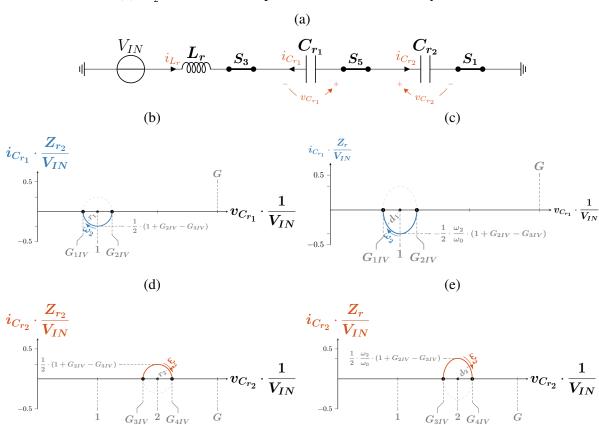

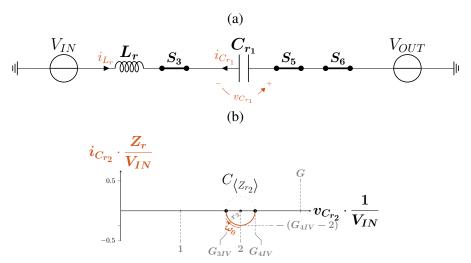

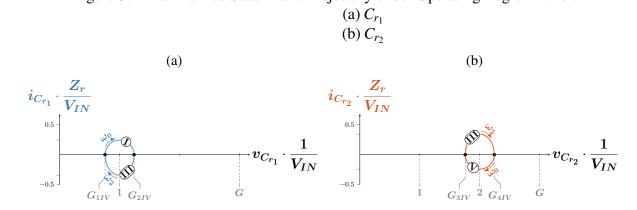

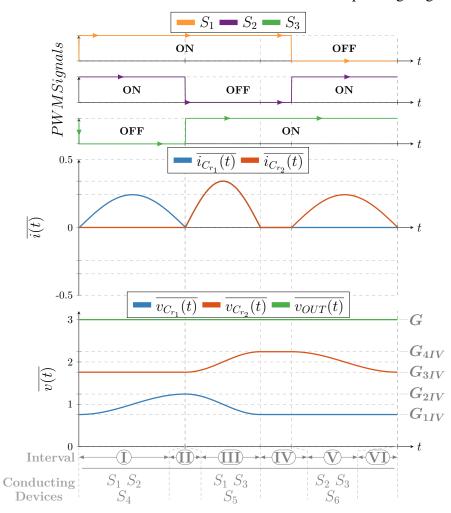

In a similar fashion, [Shuai et al. 2010] proposed a unidirectional 3L resonant flying capacitor boost converter, where the same commutation cell can be used, as shown in Figure 3, in which a bidirectional version is exhibited. Thus, introducing no further components but perceiving the inductor  $L_r$  and capacitor  $C_r$  in a different manner. In the resonant-mode,  $L_r$  and  $C_r$  affect the static gain, depending on the operating switching frequency  $f_{sw}$  and output load conditions, simplified as a resistive element  $R_{OUT}$ . Thus, the 3L-RFLCC topology can also be explored to regulate the output voltage as a function of the switching frequency  $f_{sw}$ .

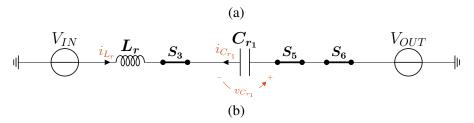

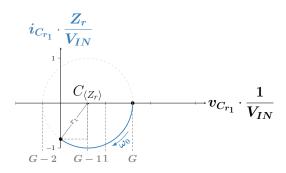

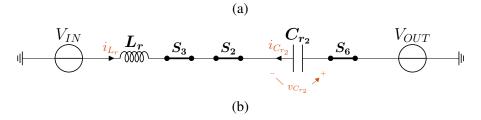

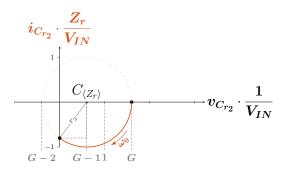

# 1.2.1 Operation Principle

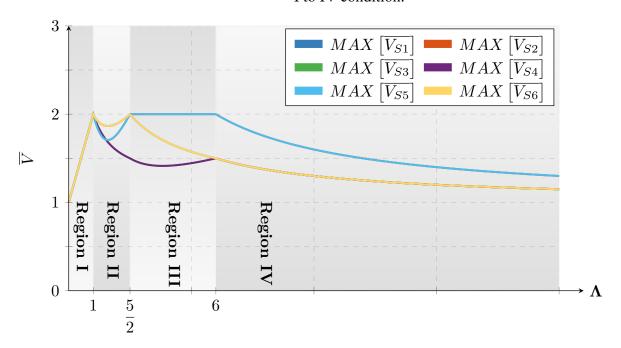

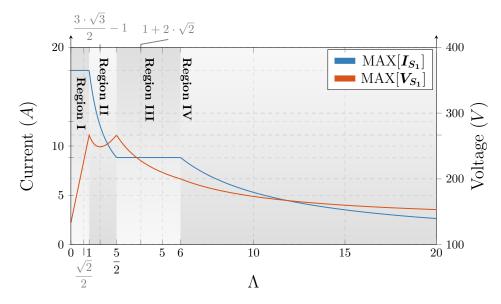

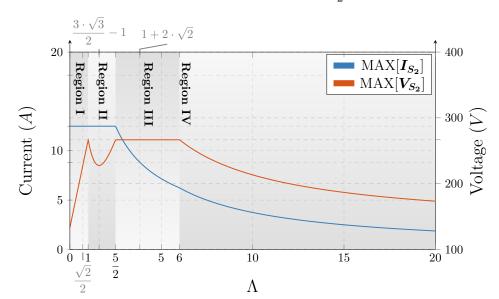

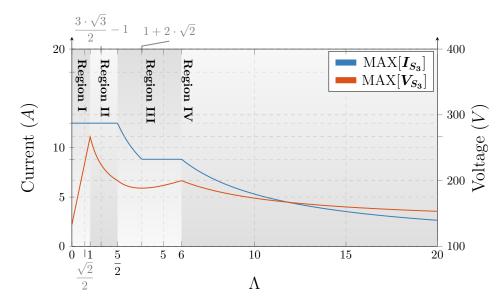

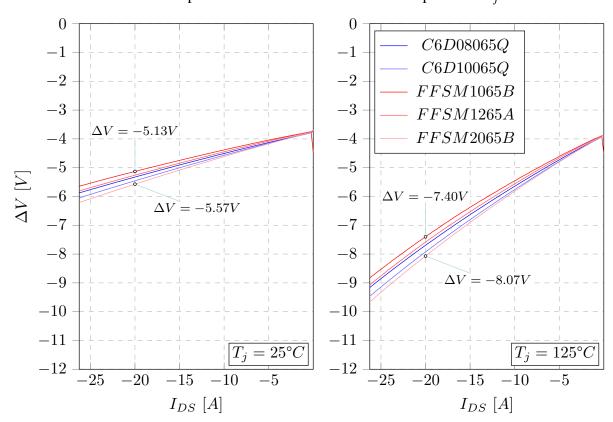

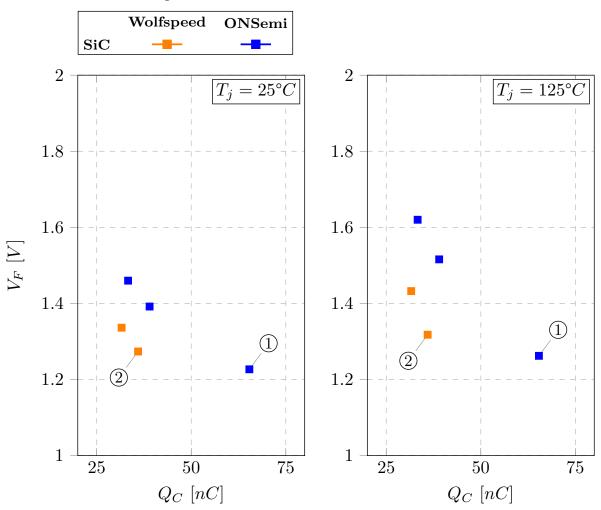

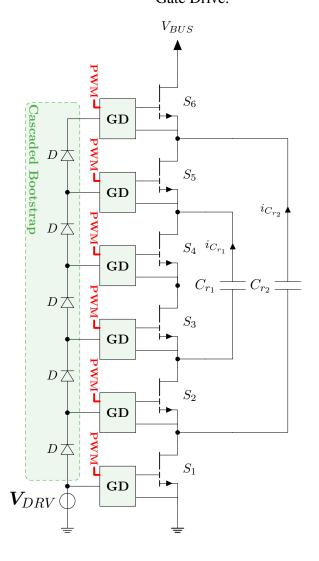

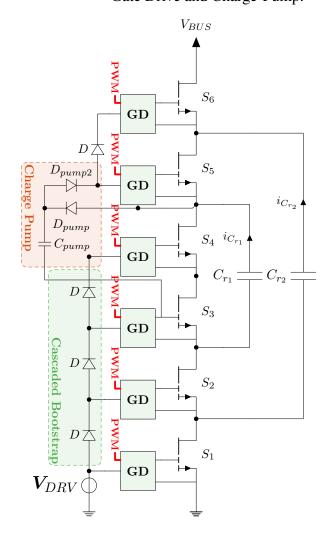

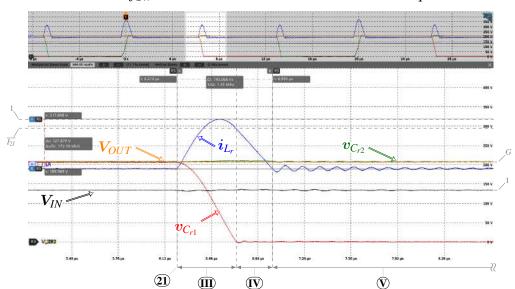

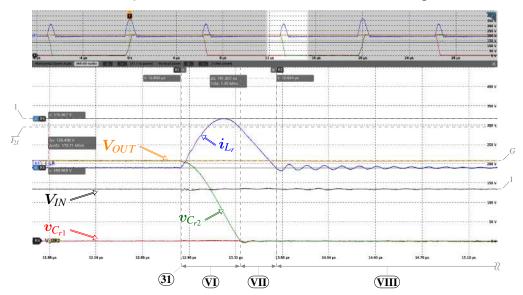

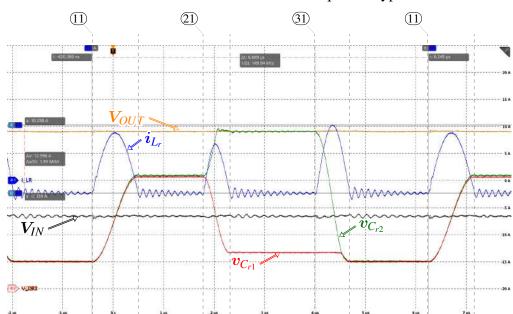

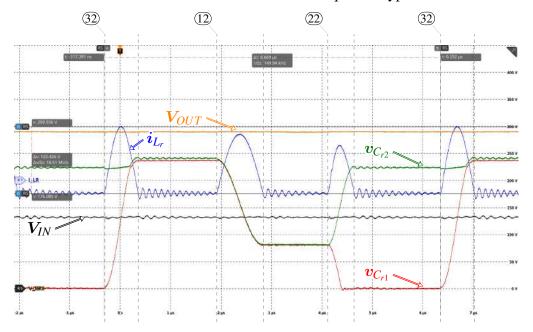

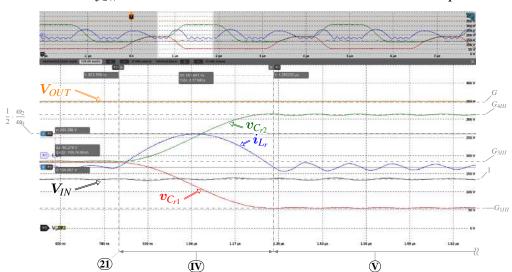

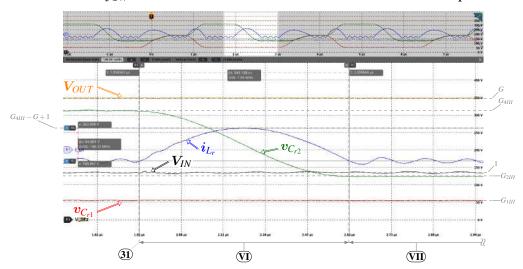

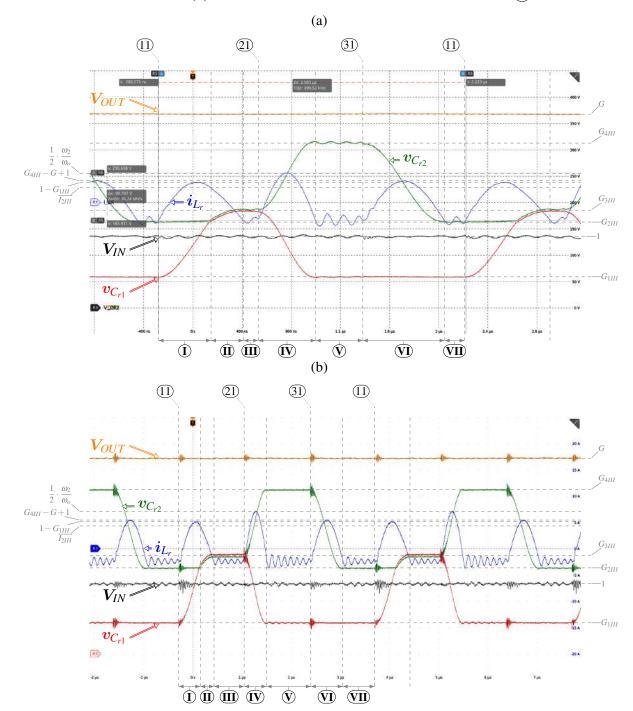

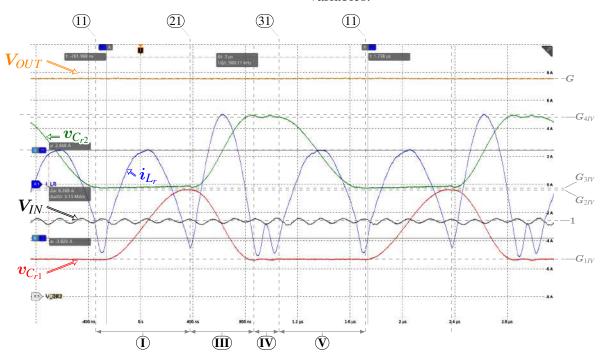

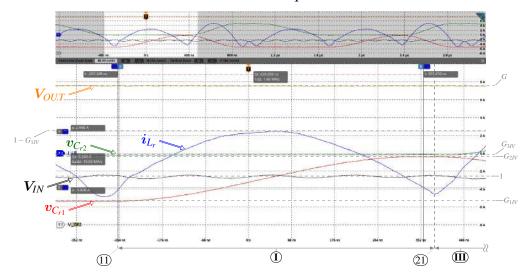

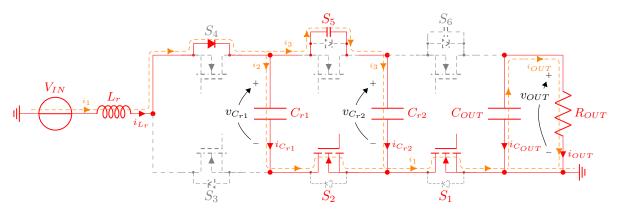

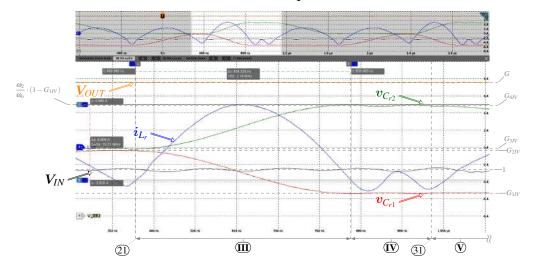

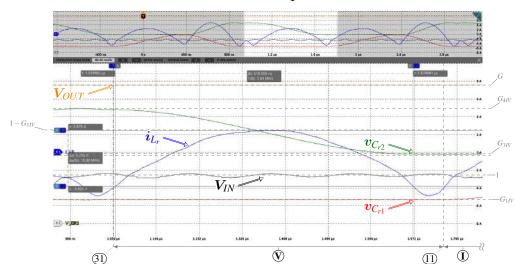

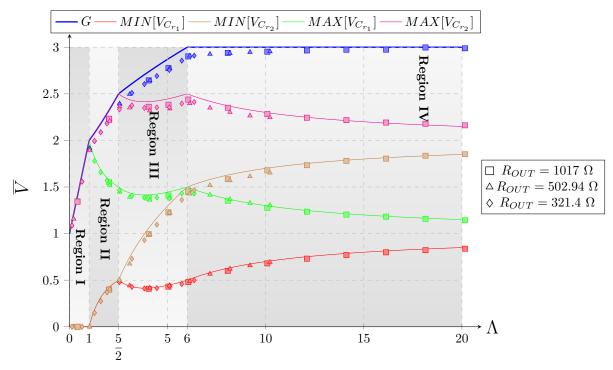

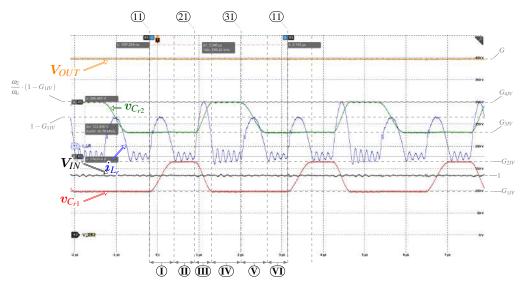

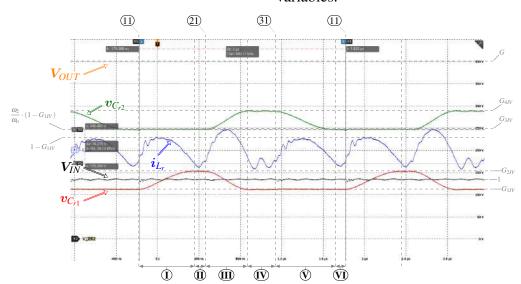

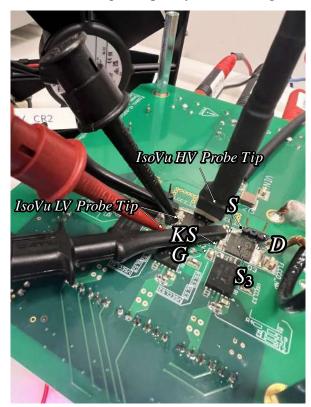

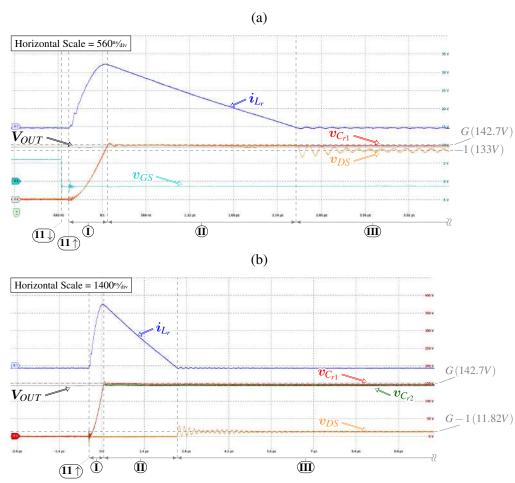

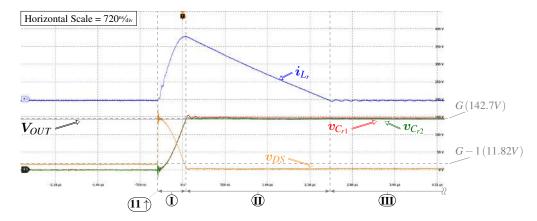

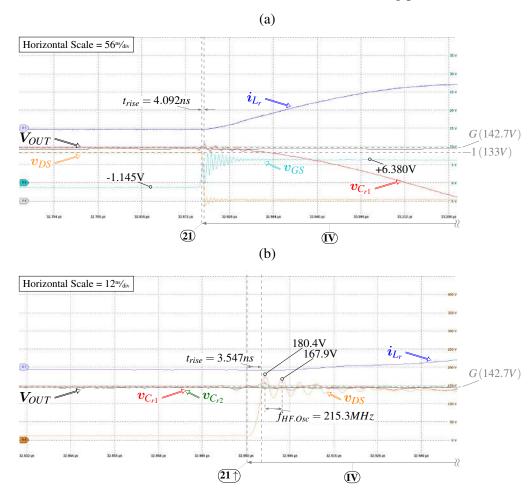

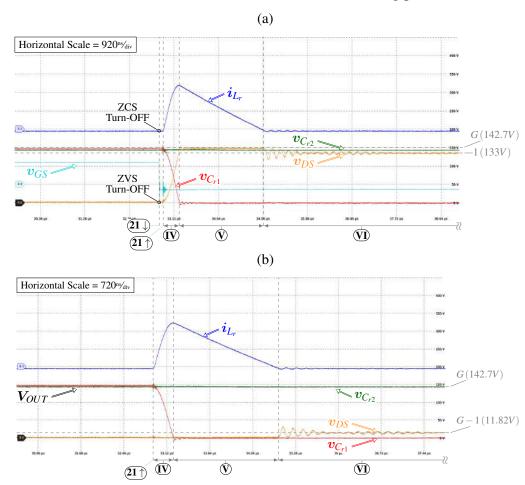

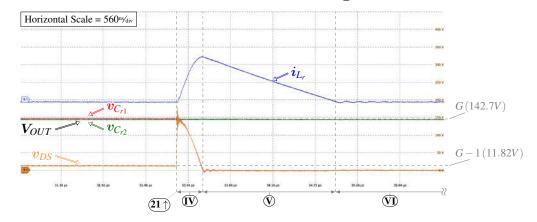

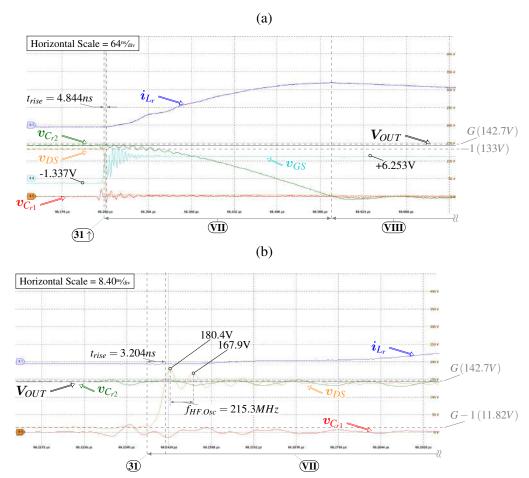

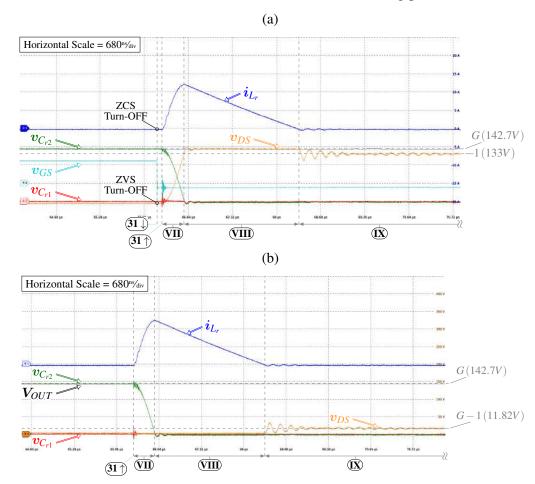

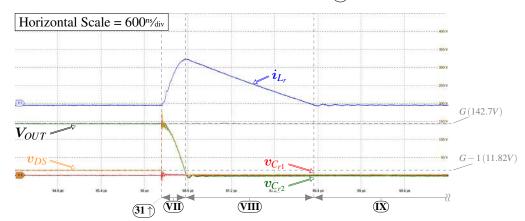

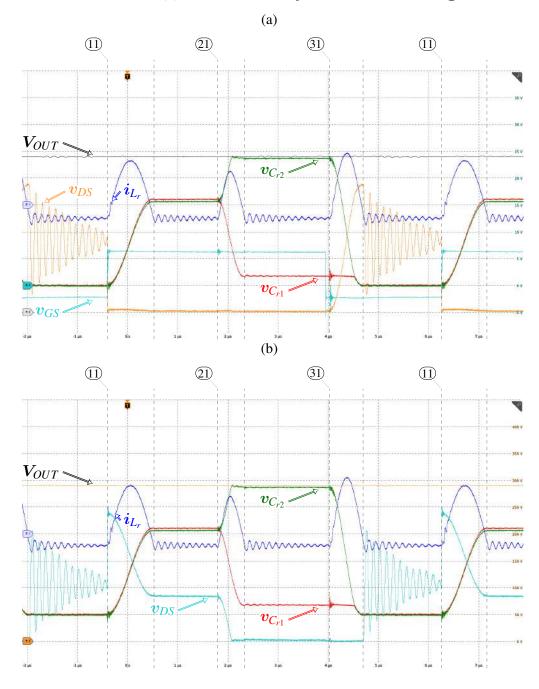

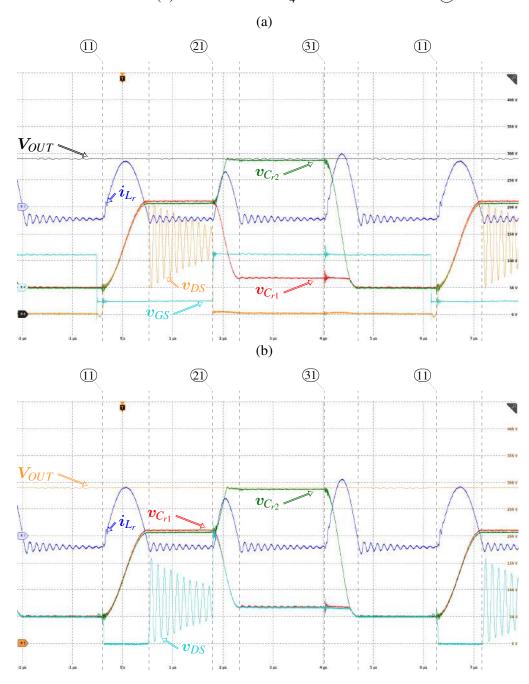

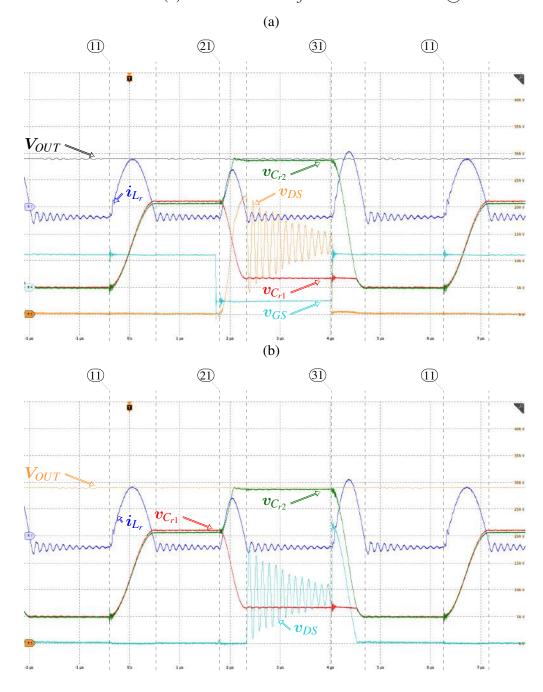

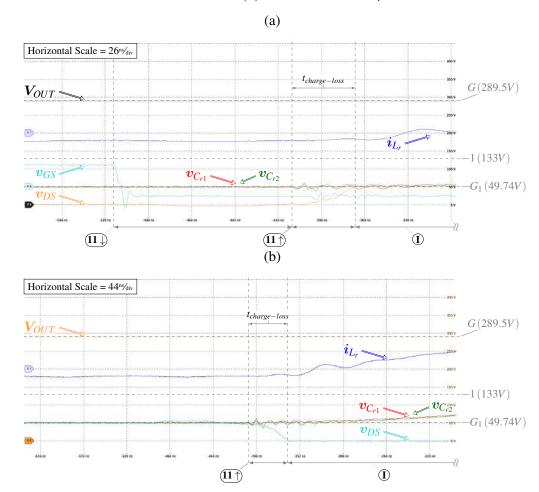

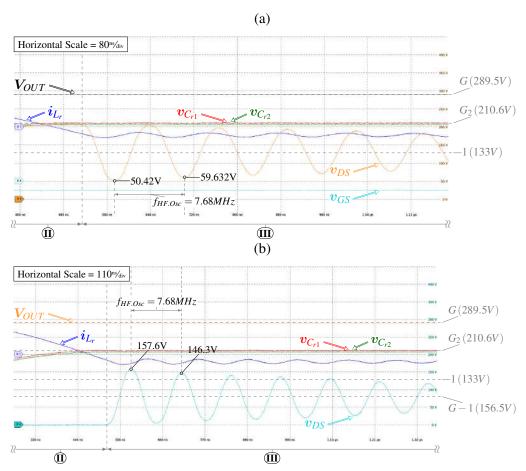

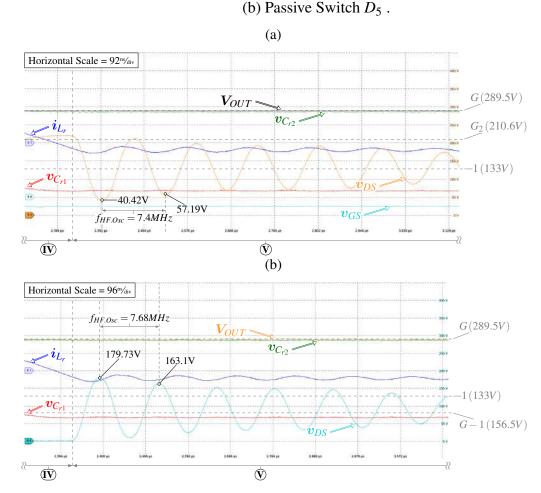

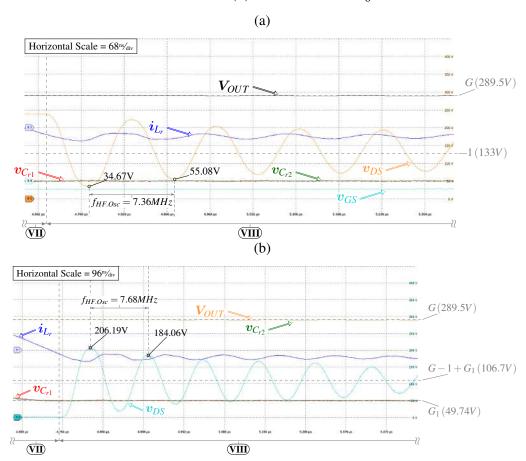

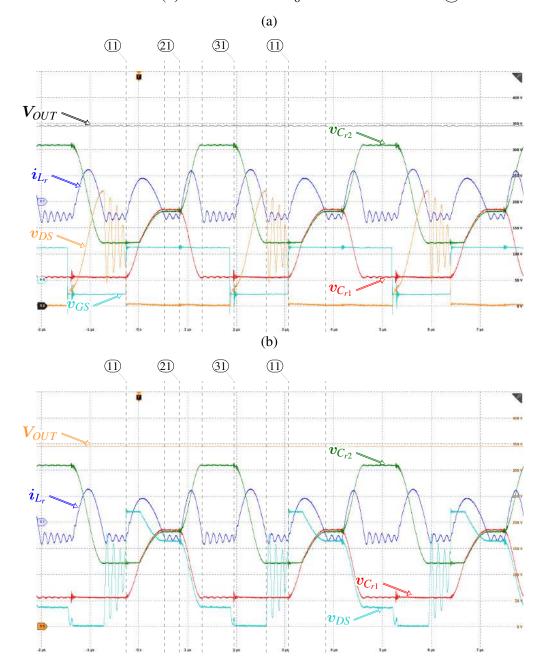

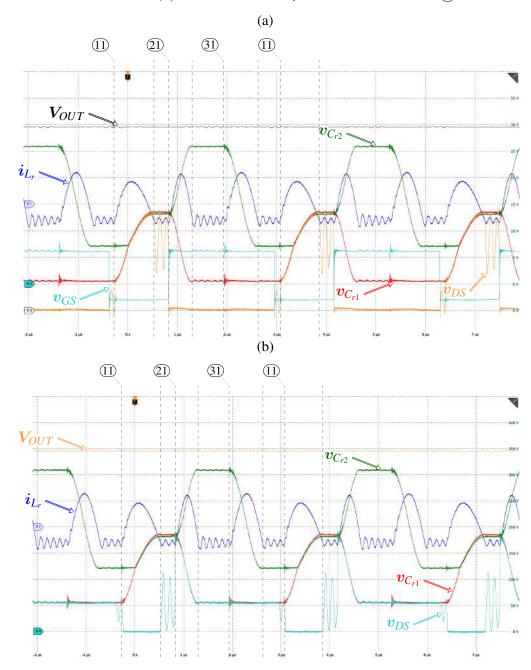

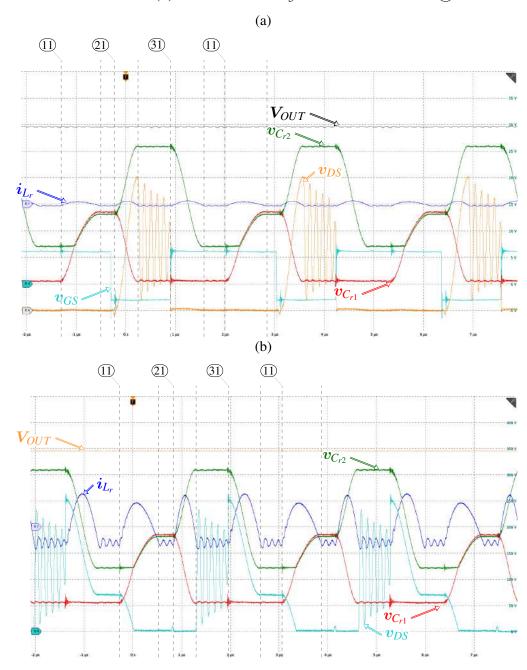

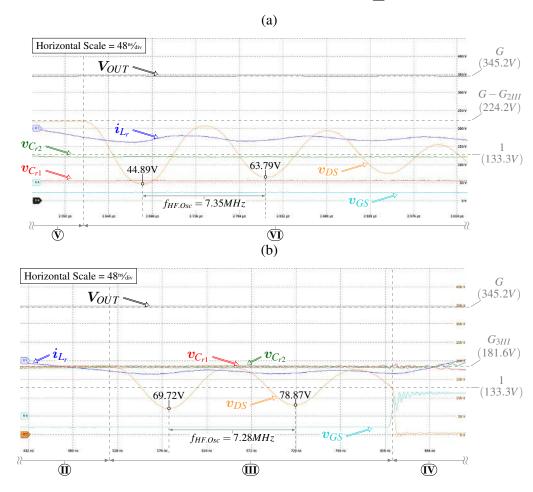

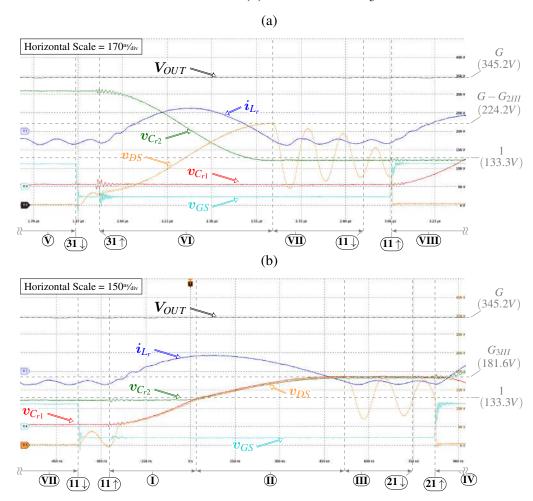

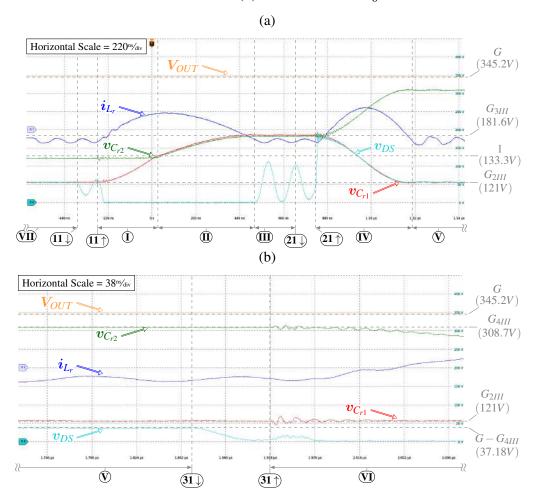

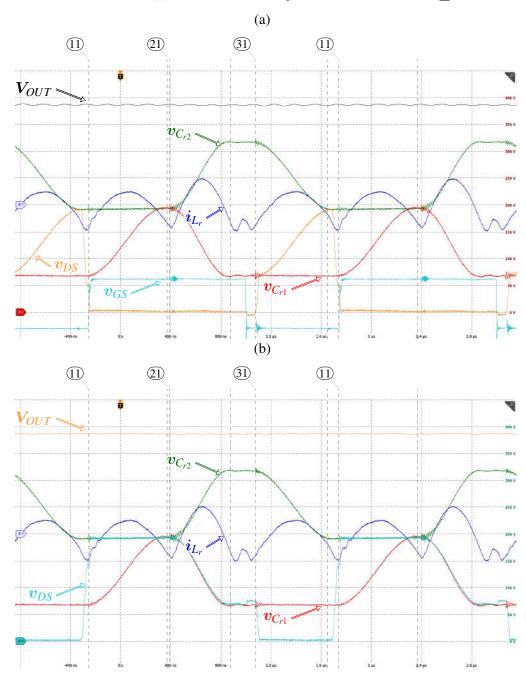

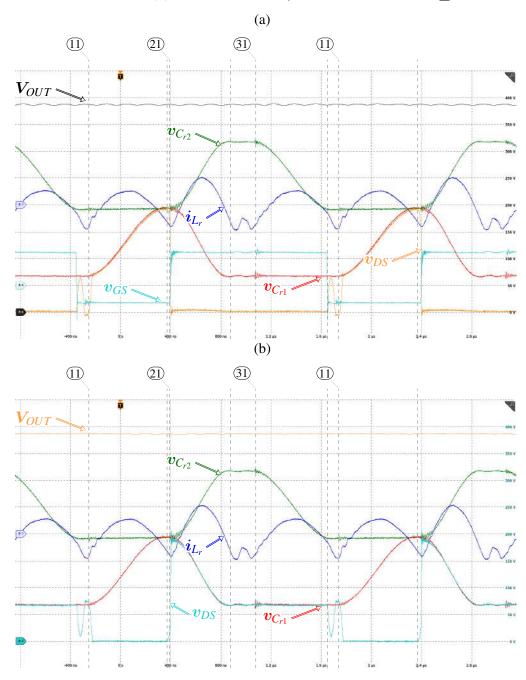

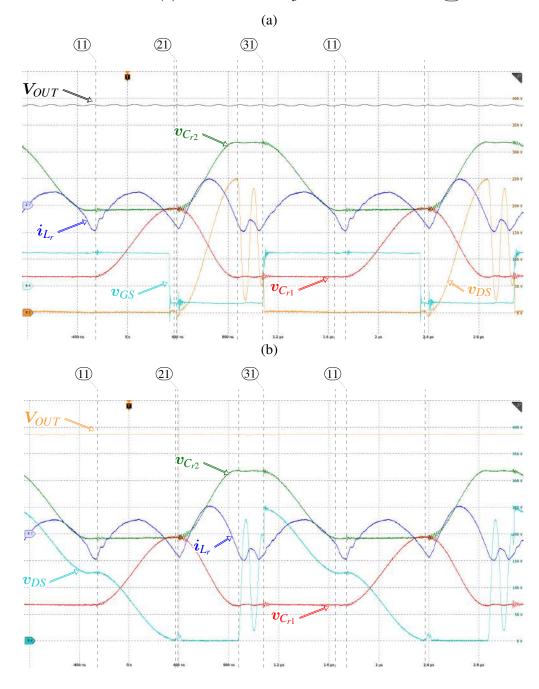

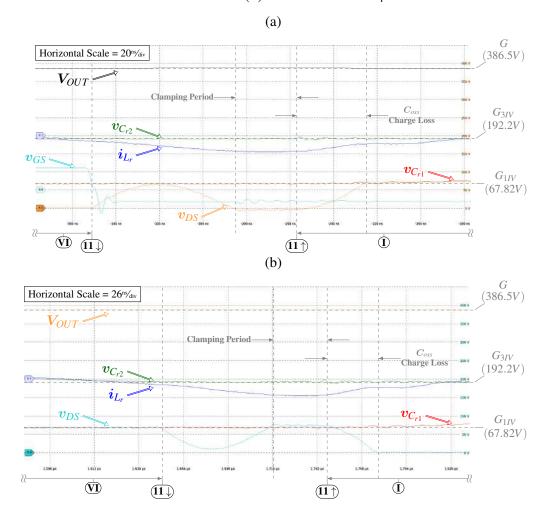

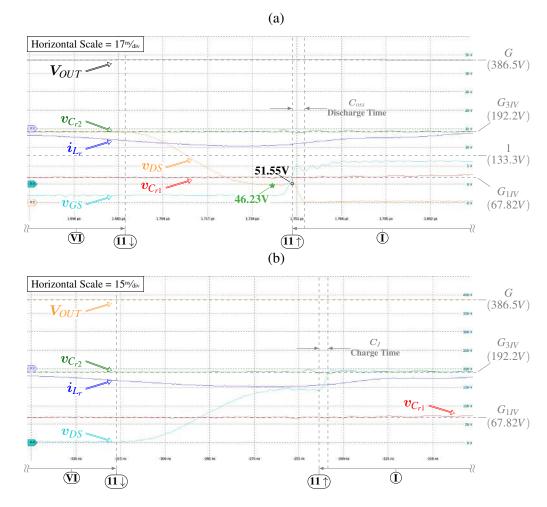

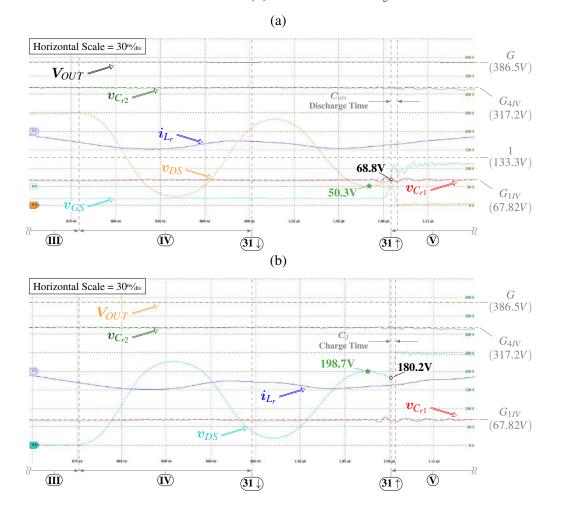

For the sake of describing the operation of the 3L resonant flying capacitor boost converter, the Output Capacitor  $C_{OUT}$  is assumed to be big enough. Thus, the Output Voltage  $V_{OUT}$  is considered constant within the different topological stages. The switches  $S_1$  and  $S_2$  are actively switching complementary to each other, and constant 50% duty cycle, whereas the switches  $S_3$  and  $S_4$  are passively switching.