**UNIVERSIDADE DO ESTADO DE SANTA CATARINA – UDESC

CENTRO DE CIÊNCIAS TECNOLÓGICAS – CCT

PROGRAMA DE PÓS-GRADUAÇÃO EM ENGENHARIA ELÉTRICA**

**HENRIQUE FERNANDES DE SOUZA**

**METODOLOGIA DE IDENTIFICAÇÃO DE FALHAS DE CIRCUITO ABERTO EM

CONVERSORES MULTINÍVEIS CHB**

**JOINVILLE**

**2023**

**HENRIQUE FERNANDES DE SOUZA**

**METODOLOGIA DE IDENTIFICAÇÃO DE FALHAS DE CIRCUITO ABERTO EM

CONVERSORES MULTINÍVEIS CHB**

Dissertação apresentada ao Programa de Pós–Graduação em Engenharia Elétrica do Centro de Ciências Tecnológicas da Universidade do Estado de Santa Catarina, como requisito parcial para a obtenção do grau de Mestre em Engenharia Elétrica.

Orientador: Alessandro Luiz Batschauer

Coorientador: Felipe Joel Zimann

**JOINVILLE

2023**

Para gerar a ficha catalográfica de teses e

dissertações acessar o link:

<https://www.udesc.br/bu/manuais/ficha>

De Souza, Henrique Fernandes

Metodologia de Identificação de Falhas de Circuito

Aberto em Conversores Multiníveis CHB / Henrique

Fernandes De Souza. - Joinville, 2023.

117 p. : il. ; 30 cm.

Orientador: Alessandro Luiz Batschauer.

Coorientador: Felipe Joel Zimann.

Dissertação (Mestrado) - Universidade do Estado

de Santa Catarina, Centro de Ciências Tecnológicas,

Programa de Pós-Graduação em Engenharia Elétrica,

Joinville, 2023.

1. Palavra-chave. 2. Palavra-chave. 3. Palavra-chave.

4. Palavra-chave. 5. Palavra-chave. I. Batschauer,

Alessandro Luiz . II. Zimann, Felipe Joel . III.

Universidade do Estado de Santa Catarina, Centro de

Ciências Tecnológicas, Programa de Pós-Graduação em

Engenharia Elétrica. IV. Título.

## **HENRIQUE FERNANDES DE SOUZA**

### **METODOLOGIA DE IDENTIFICAÇÃO DE FALHAS DE CIRCUITO ABERTO EM CONVERSORES MULTINÍVEIS CHB**

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica do Centro de Ciências Tecnológicas da Universidade do Estado de Santa Catarina, como requisito parcial para a obtenção do grau de Mestre em Engenharia Elétrica.

Orientador: Alessandro Luiz Batschauer

Coorientador: Felipe Joel Zimann

#### **BANCA EXAMINADORA:**

Prof. Dr. Alessandro Luiz Batschauer

Universidade do Estado de Santa Catarina (UDESC - CCT) - Presidente da banca e orientador

Membros:

Prof. Dr. Tiago Davi Curi Busarello

Universidade Federal de Santa Catarina (UFSC - Blumenau)

Dr. Gustavo Lambert

Supplier Indústria e Comércio de Eletro-Eletrônicos Ltda.

Joinville, 28 de julho de 2023

## AGRADECIMENTOS

Gostaria de agradecer, primeiramente, a minha família, por sempre me incentivar a dar continuidade ao ensino superior e a pós-graduação. A meu pai, Edenarte Egídio de Souza, e minha mãe, Lucia Regina J. Fernandes, pelo apoio emocional, financeiro e psicológico durante estes longos anos. A minha namorada, e (espero que) futura esposa, Thaisa Aviz, por aguentar meus diversos dilemas existenciais e longas semanas de ausência, dedicadas a experimentação e escrita deste trabalho.

Agradeço ao professor Dr. Alessandro Luiz Batschauer pela orientação prestada, desde a graduação, que me ajudou a realizar este trabalho e contribuiu para meu desenvolvimento como pesquisador. A coorientação do professor Dr. Felipe Joel Zimann, que compartilhou diversas horas de experimentação em bancada e longas discussões filosóficas que contribuíram para que este trabalho pudesse ser concluído de forma bem sucedida.

Aos professores Dr. Marcello Mezaroba, Dr. Joselito Anastácio Heerdt, Dr. Sérgio Vidal Garcia Oliveira e Dr. Yales Rômulo de Novaes do grupo do Núcleo de Processamento de Energia Elétrica – nPEE da Universidade do Estado de Santa Catarina – UDESC. Aos amigos de laboratório Dr. Gustavo Lambert e Dr. Marcos Vinícius Bressan, pelas discussões técnicas e filosóficas, pelos conselhos, pelas experiências e pelo tempo que compartilhamos juntos.

Ao Dr. Rubens Tadeu Hock Jr., pela disponibilização do protótipo utilizado neste trabalho e pelas diversos auxílios para adequação e correta utilização do mesmo.

Aos meus amigos: Alexander Cesar Anzini, pelo auxílio na edição das imagens utilizadas neste trabalho; Bruno Guarienti de Oliveira, pelas dicas de programação em C; e Raul Knopp Neto, pelo excelente trabalho de revisão gramatical.

Por fim, agradeço a todos meus amigos, colegas e as pessoas que de alguma forma contribuíram com esta conquista. Impossível citar todos os momentos que foram vividos e todas pessoas que passaram em minha vida, mas saibam que sou eternamente grato e sempre serão lembrados. Agradeço a todos, pelos erros e acertos, pelas derrotas e conquistas, por me ajudar a fazer o meu melhor sempre.

## RESUMO

Este trabalho apresenta uma metodologia de identificação de falhas de circuito aberto aplicada ao conversor multinível CHB. Tal metodologia é aplicável aos conversores modulares já difundidos na literatura e na indústria e não depende da estratégia de modulação adotada. O trabalho propõe a utilização apenas de sinais já comumente sensoreados para o sistema de controle destes conversores, tornando-o um método universal e de baixo custo de implementação. Para tal, é proposta a leitura e condicionamento do nível médio da tensão de saída após uma falha de circuito aberto de um dos interruptores dos módulos. Este sinal é tratado através de um filtro média móvel e, a partir dele, é possível determinar a condição de falha do conversor. Com esta condição ativa, uma rotina de testes em conjunto com uma estratégia de correção, através do bypass dos módulos, é capaz de determinar o módulo danificado. O método é validado via simulação e experimentalmente através de um conversor cascata de pontes-completa monofásico com quatro módulos, operando com modulação PD-PWM.

**Palavras-chave:** Conversores modulares. Identificação de Falhas. Conversores Multiníveis. Falhas de circuito aberto. Filtro Média Móvel.

## ABSTRACT

This paper presents an open-circuit fault detection methodology applied to the multilevel converters CHB and MMC. This concept is applicable to modular converters already used by the industry and does not depend on the modulation strategy used. This paper proposes the use of only commonly measured signals for the control system of these converters, making it an universal and low-cost method. It proposes the measurement of the average output voltage after an open-circuit fault in one of the modules's switches. This signal is treated by a moving average filter and, by its results, is possible to determine the fault condition of the converter. With this condition set, a test routine alongside a correction strategy, through a bypass of the modules, is capable of determining the defective module. The method is validated via simulation and experimentation using a four-module single-phase full-bridge cascaded converter, operating with PD-PWM modulation.

**Keywords:** Modular Converters. Fault Identification. Multilevel Converters. Open-circuit Fault. Moving Average Filter.

## LISTA DE ILUSTRAÇÕES

|                                                                                                                                                                                                                                                                                                              |    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1 – Primeiro motor de indução proposto por Tesla, em exibição no Museu Britânico de Ciência, em Londres. . . . .                                                                                                                                                                                      | 18 |

| Figura 2 – Consumo energético mundial de 1974 - 2019. . . . .                                                                                                                                                                                                                                                | 19 |

| Figura 3 – Esquema simplificado de um sistema HVDC. . . . .                                                                                                                                                                                                                                                  | 20 |

| Figura 4 – Sistema HVDC da empresa ABB. . . . .                                                                                                                                                                                                                                                              | 21 |

| Figura 5 – Braço de topologia CHB com $n$ células por fase e chave de <i>bypass</i> individual. . . . .                                                                                                                                                                                                      | 23 |

| Figura 6 – Braço de topologia MMC com $n$ células por fase e chave de <i>bypass</i> individual. . . . .                                                                                                                                                                                                      | 24 |

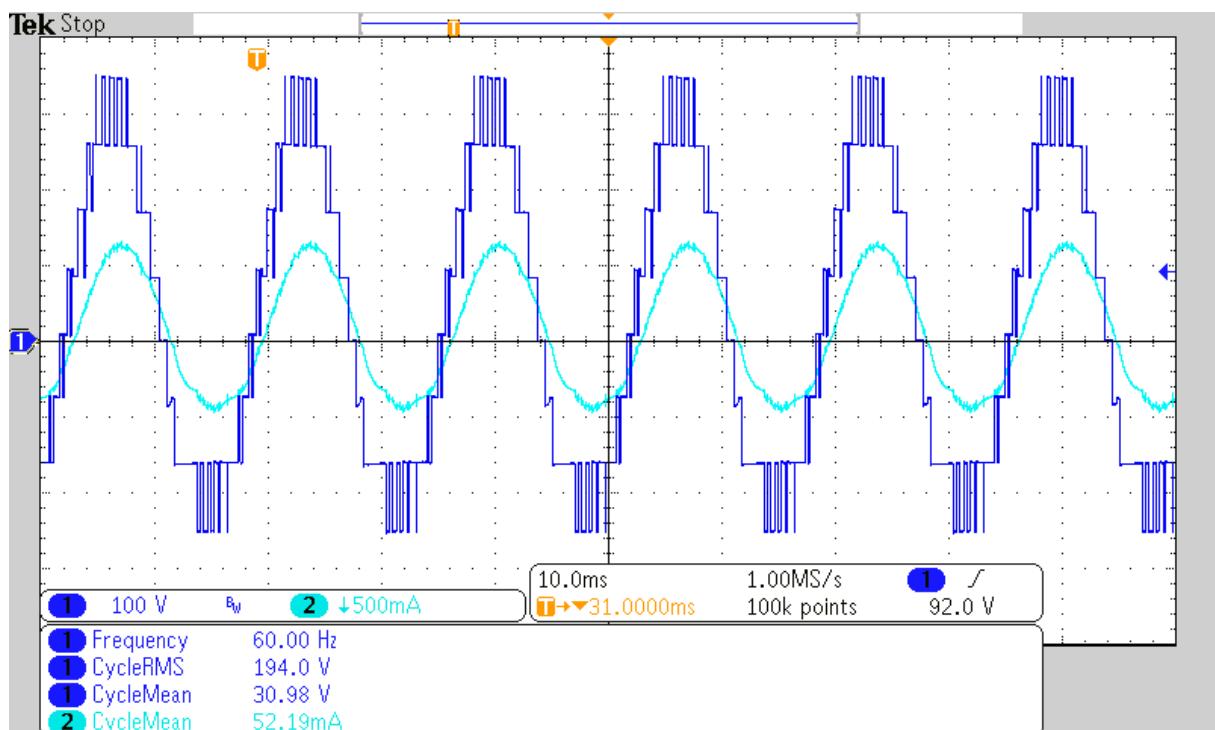

| Figura 7 – Formas de onda de tensão (Azul) [100 V/div] e corrente (Ciano) [500 mA V/div] de saída de um conversor CHB com falha de um semicondutor do semibraço inferior. . . . .                                                                                                                            | 25 |

| Figura 8 – Análise harmônica das formas de onda de tensão e corrente de saída de um conversor CHB com falha em um dos módulos. . . . .                                                                                                                                                                       | 25 |

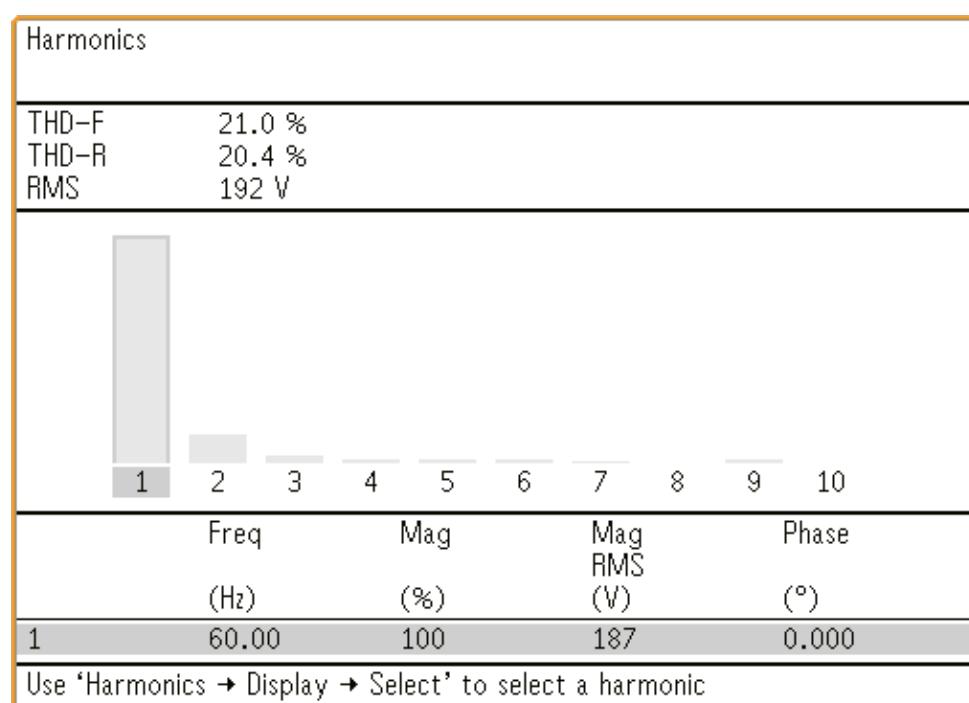

| Figura 9 – Modelo 3D com visualização interna de um IGBT. . . . .                                                                                                                                                                                                                                            | 26 |

| Figura 10 – Levantamentos das taxas de falhas em conversores: <b>(a)</b> Distribuição das fontes de estresses; <b>(b)</b> Distribuição de falhas entre os principais componentes. . . . .                                                                                                                    | 29 |

| Figura 11 – Etapas tradicionais de funcionamento da topologia ponte completa com circulação de corrente pelo banco capacitivo. . . . .                                                                                                                                                                       | 32 |

| Figura 12 – Etapas tradicionais de funcionamento da topologia ponte completa sem circulação de corrente pelo banco capacitivo. . . . .                                                                                                                                                                       | 33 |

| Figura 13 – Etapas adicionais de funcionamento da topologia ponte completa com falha em circuito aberto do interruptor G2. . . . .                                                                                                                                                                           | 33 |

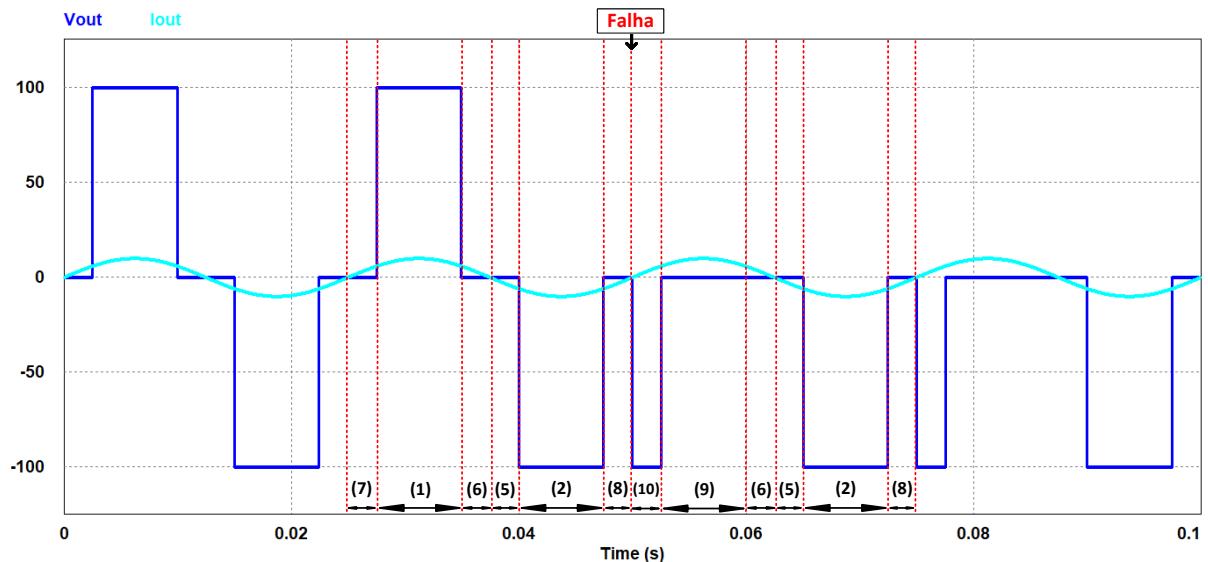

| Figura 14 – Formas de onda de tensão (Azul) e corrente (Ciano) pré e pós-falha do interruptor G2. . . . .                                                                                                                                                                                                    | 34 |

| Figura 15 – Formas de onda simuladas sob operação normal. <b>(a)</b> Tensões de saída. <b>(b)</b> Correntes do braço e corrente diferencial. <b>(c)</b> Tensões dos capacitores da parte superior do braço da fase $a$ . <b>(d)</b> Tensões dos capacitores da parte inferior do braço da fase $a$ . . . . . | 36 |

| Figura 16 – Formas de onda simuladas sob falha de circuito aberto na fase $a$ . <b>(a)</b> Corrente diferencial. <b>(b)</b> Tensões dos capacitores da parte superior do braço da fase $a$ . <b>(c)</b> Tensões dos capacitores da parte inferior do braço da fase $a$ . . . . .                             | 37 |

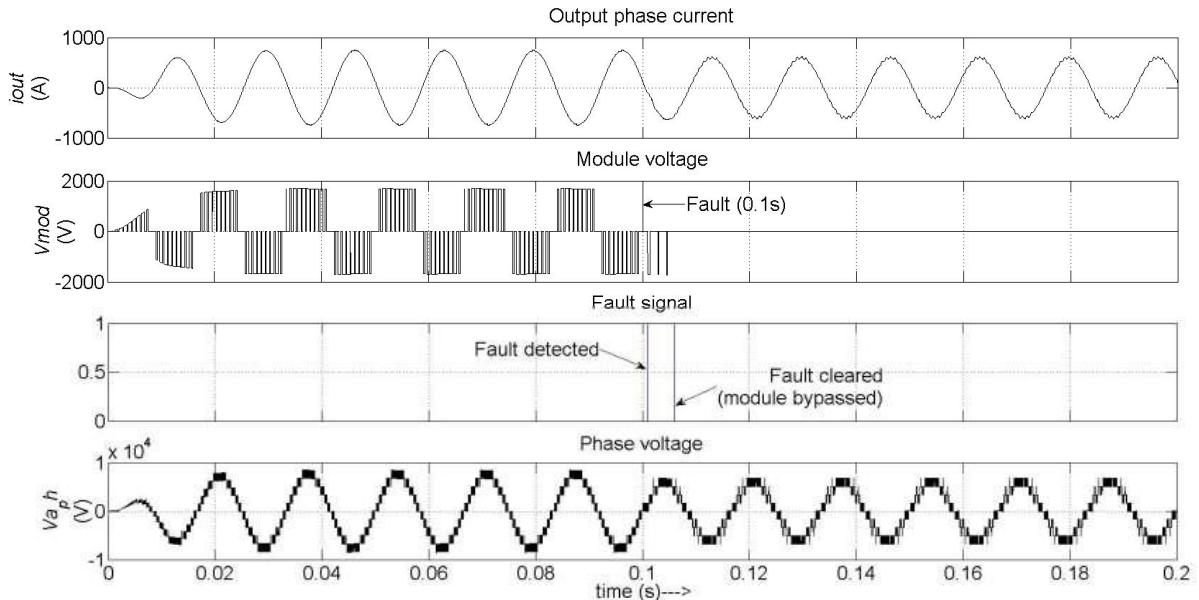

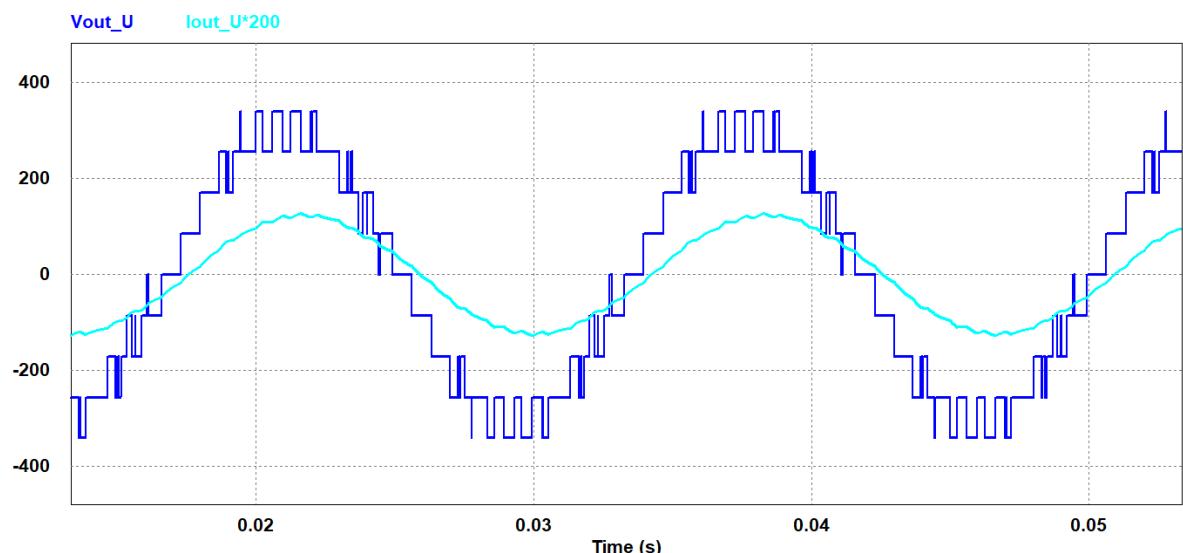

| Figura 17 – Formas de onda de tensão e corrente simuladas para falha no interruptor G2 do módulo 1, sem correção. . . . .                                                                                                                                                                                    | 38 |

| Figura 18 – Formas de onda de tensão e corrente simuladas para falha no interruptor G2 do módulo 1, com correção. . . . .                                                                                                                                                                                    | 39 |

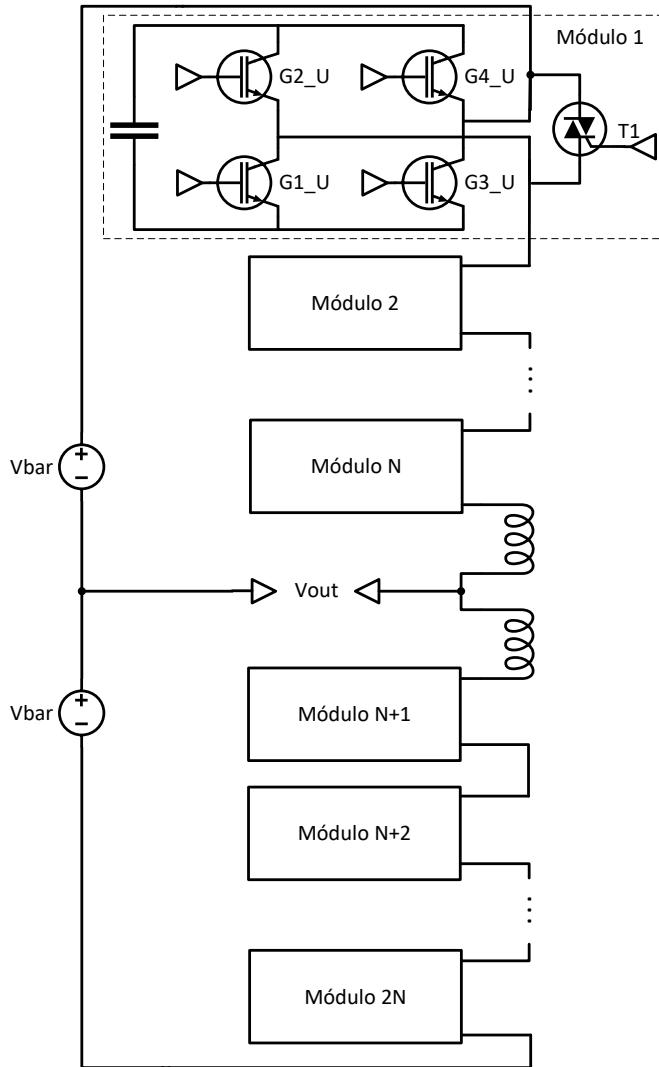

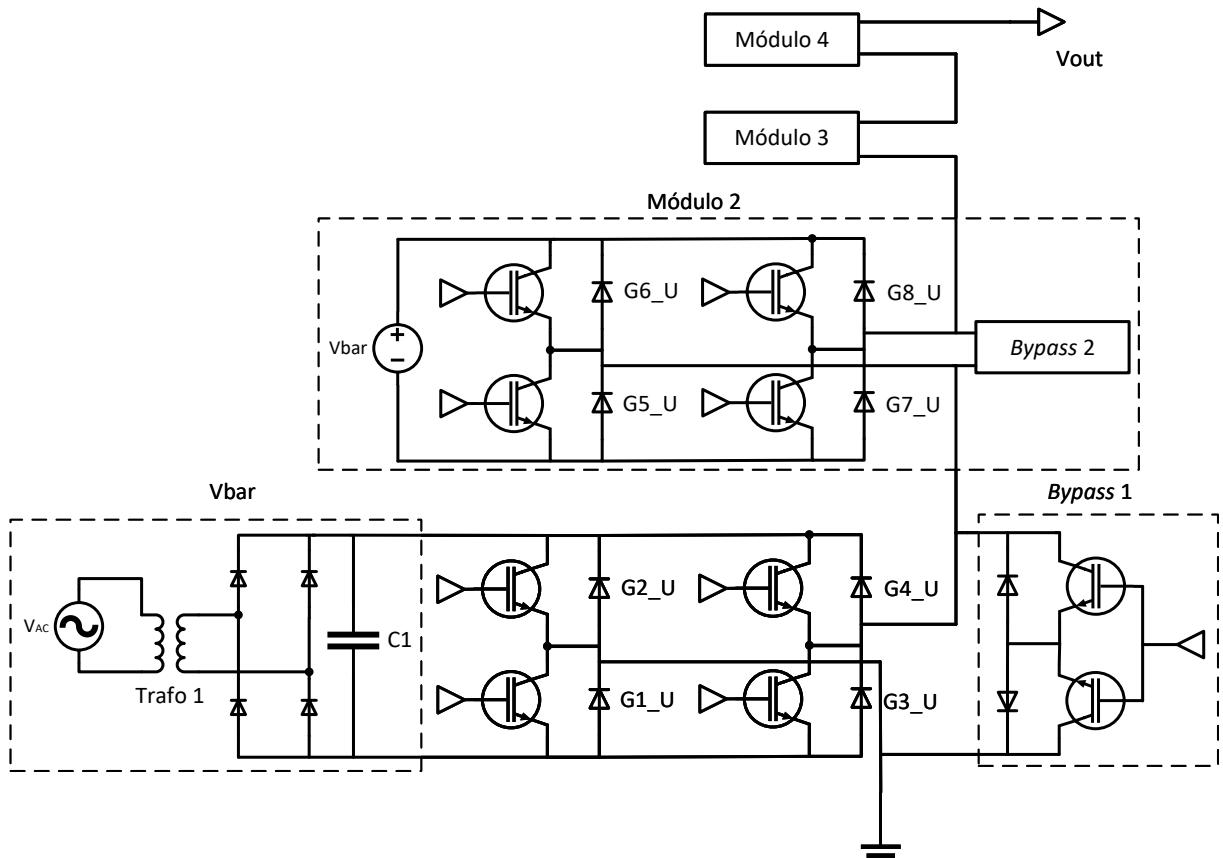

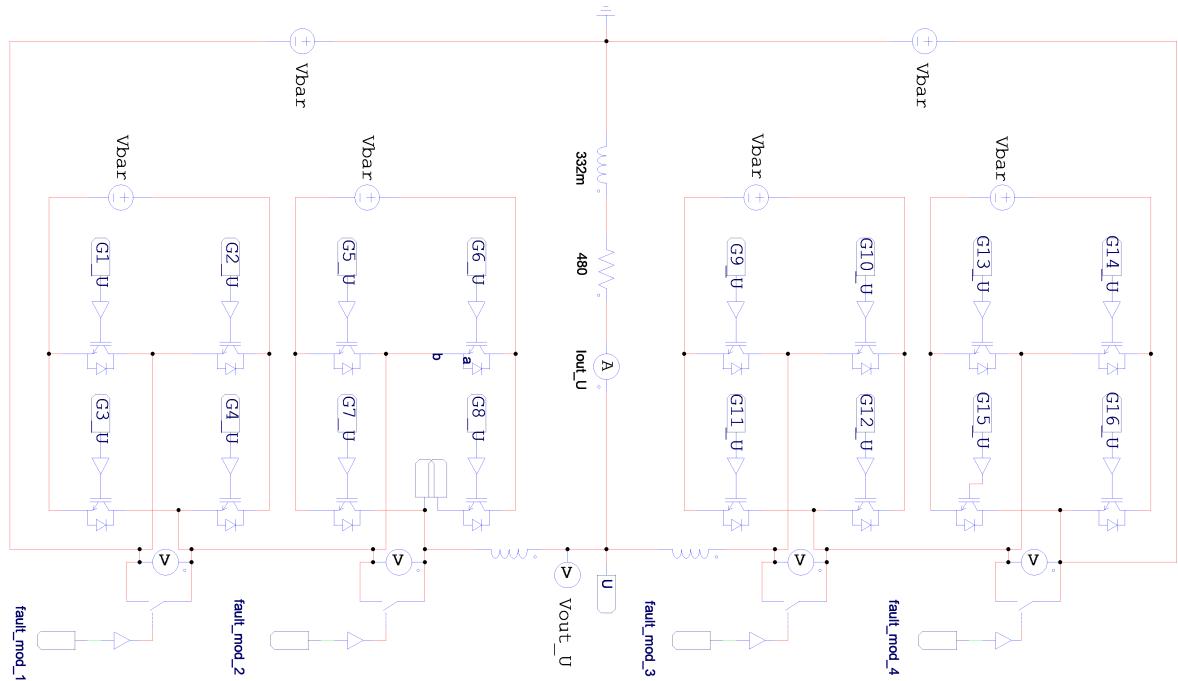

| Figura 19 – Conversor CHB utilizado para simulação e experimentação. . . . .                                                                                                                                                                                                                                 | 44 |

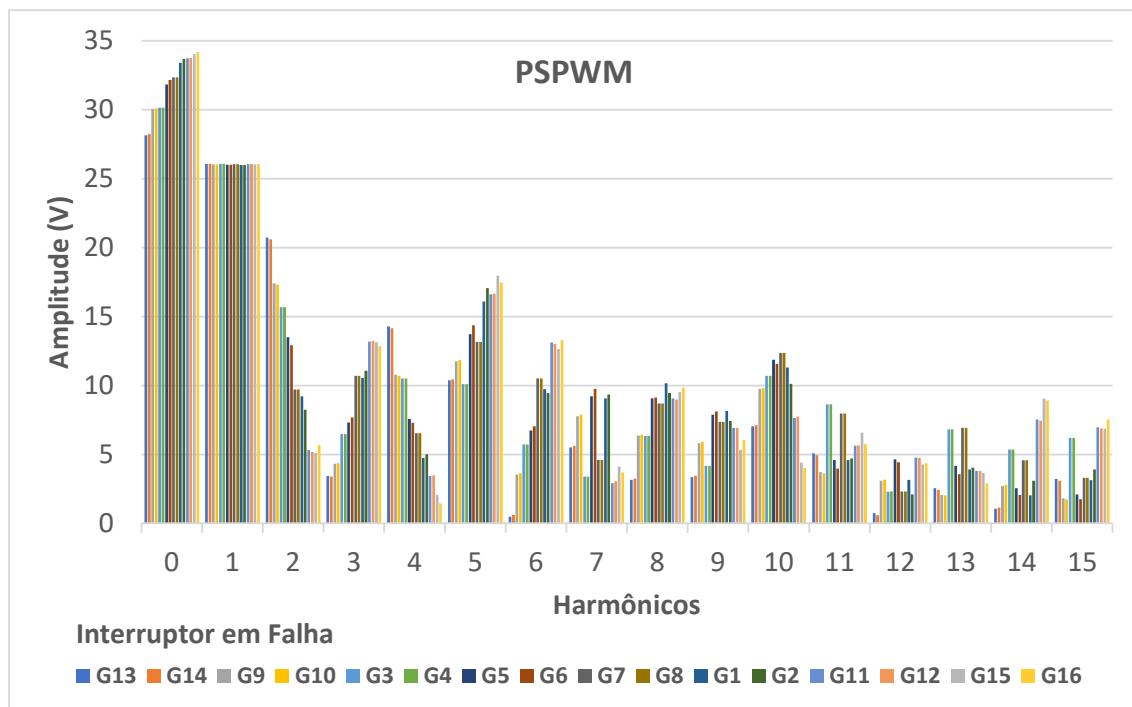

| Figura 20 – Análise harmônica pós-falha para falha individual de semicondutor utilizando modulação PS-PWM. . . . .                                                                                                                                                                                           | 45 |

|                                                                                                                                                                                                      |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

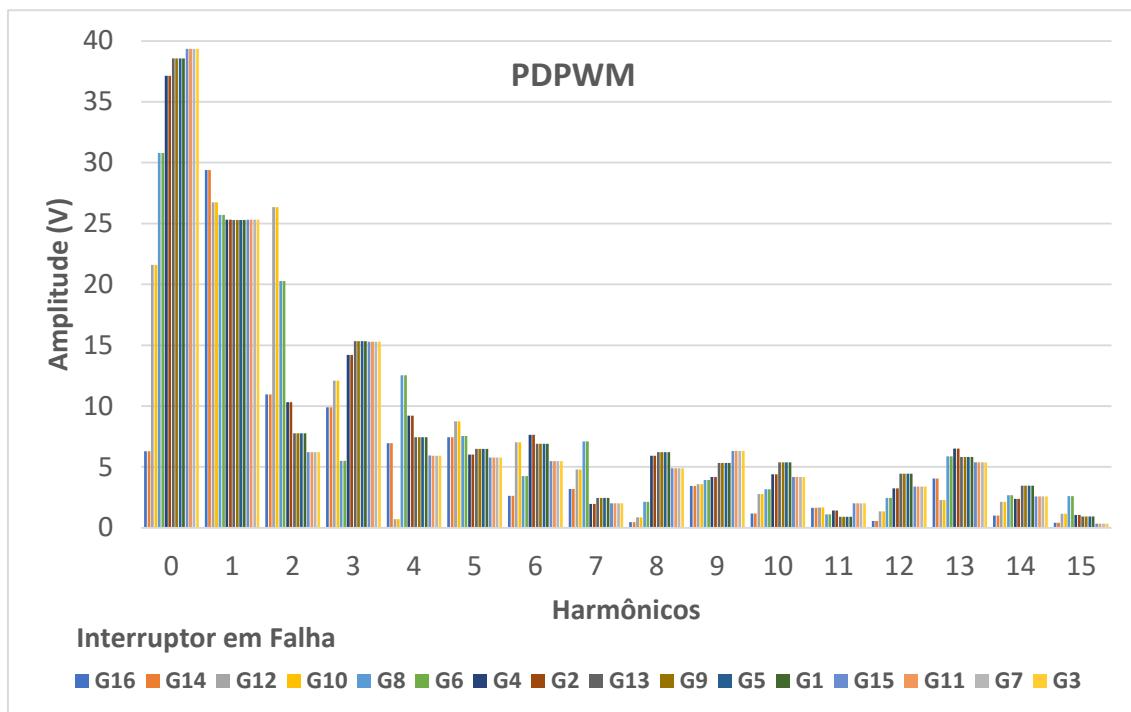

| Figura 21 – Análise harmônica pós-falha para falha individual de semicondutor utilizando modulação PD-PWM. . . . .                                                                                   | 47 |

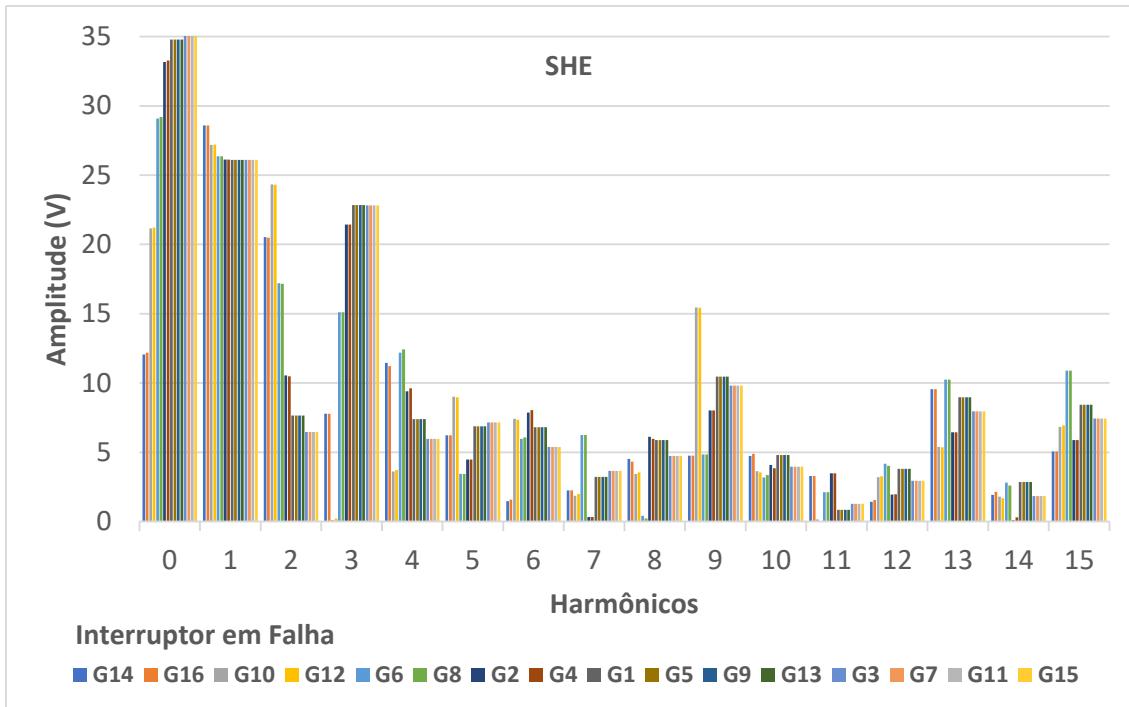

| Figura 22 – Análise harmônica pós-falha para falha individual de semicondutor utilizando modulação SHE. . . . .                                                                                      | 48 |

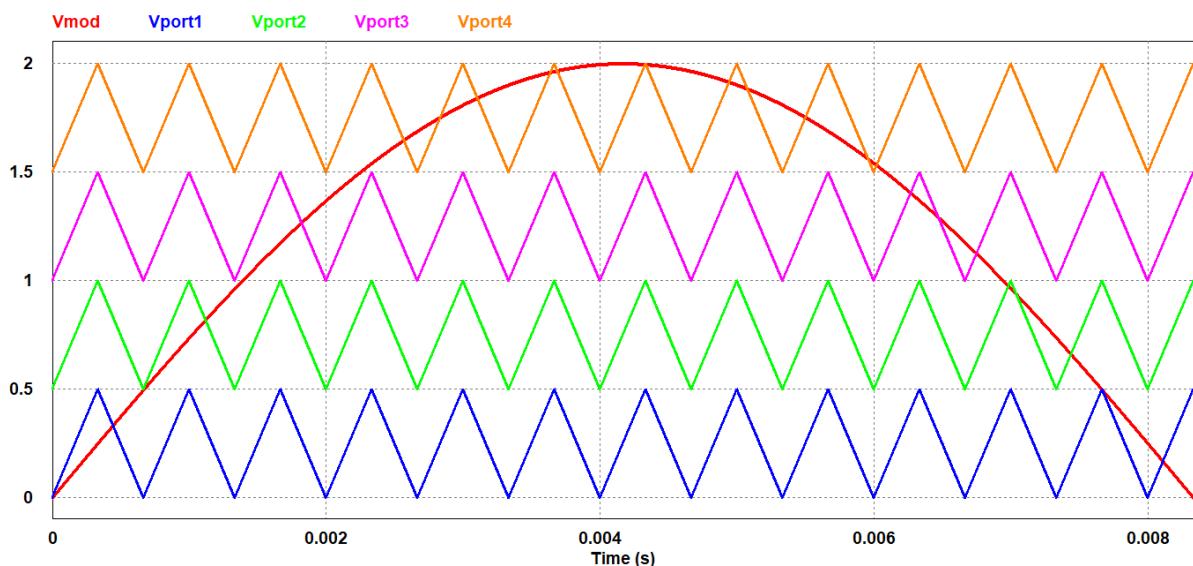

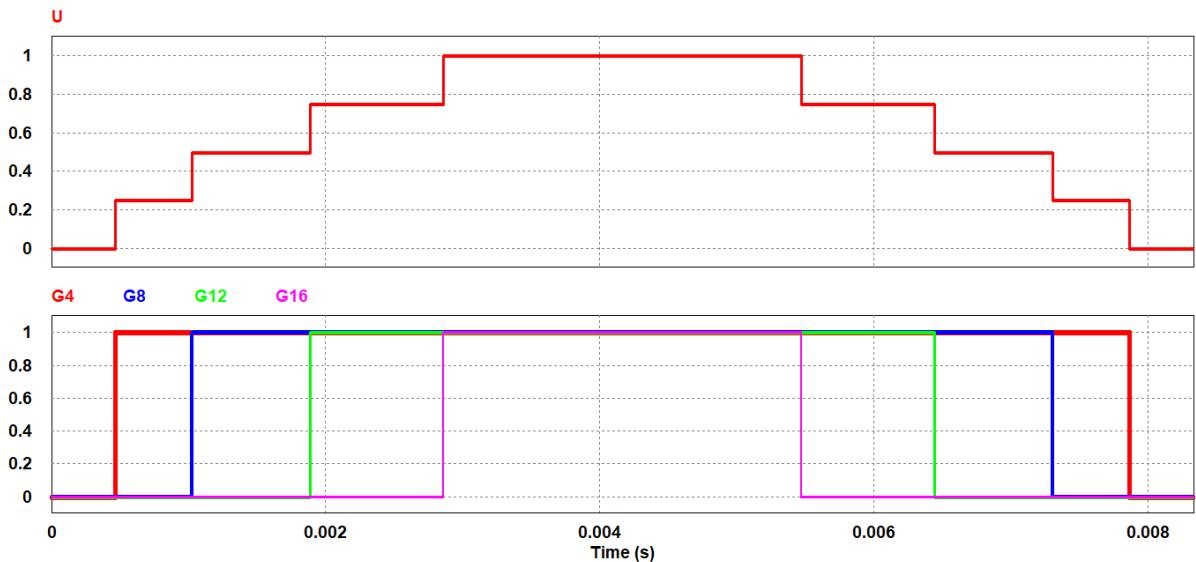

| Figura 23 – Formas de onda do semiciclo positivo da modulação PD-PWM. . . . .                                                                                                                        | 48 |

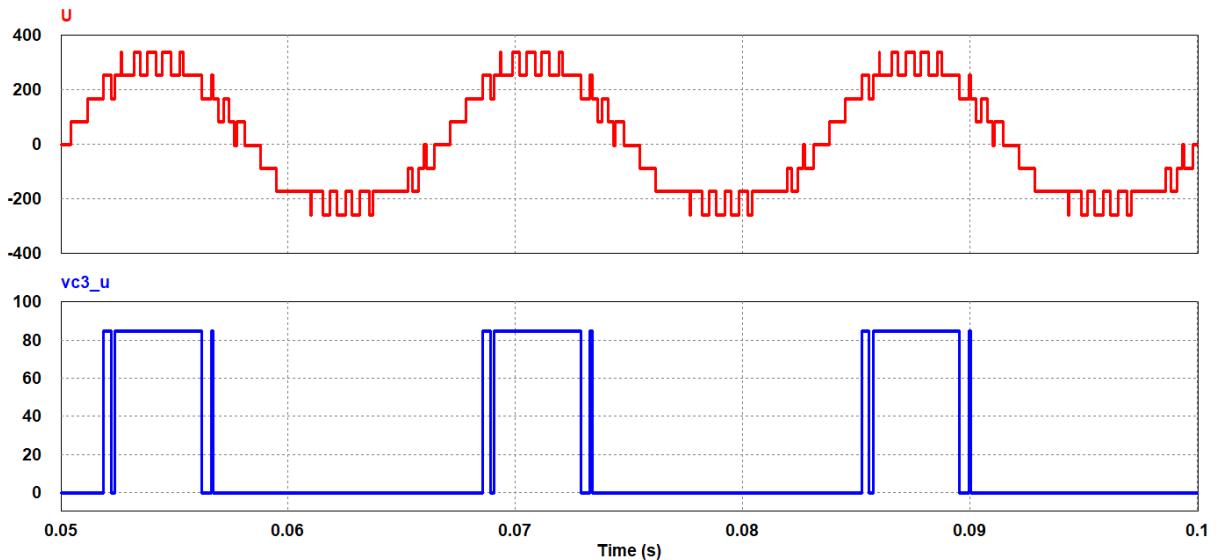

| Figura 24 – Formas de onda do semiciclo positivo da modulação SHE. . . . .                                                                                                                           | 49 |

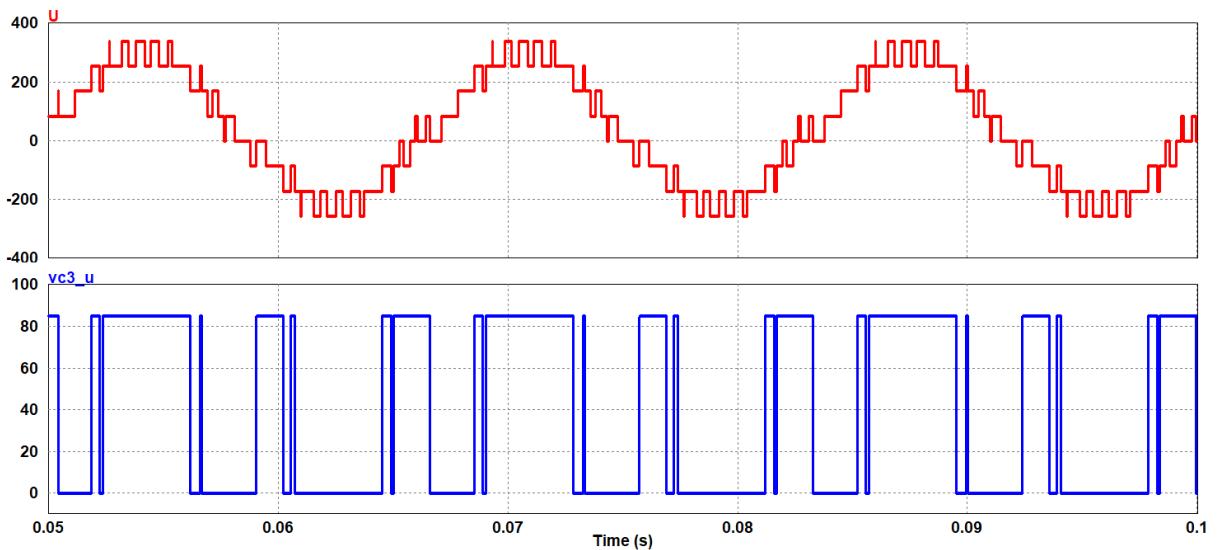

| Figura 25 – Formas de onda da tensão de saída pós-falha do interruptor 10, utilizando modulação PD-PWM. . . . .                                                                                      | 51 |

| Figura 26 – Formas de onda da tensão de saída pós-falha do interruptor 11, utilizando modulação PD-PWM. . . . .                                                                                      | 51 |

| Figura 27 – Exemplo de filtro média móvel com caixa 3x3. . . . .                                                                                                                                     | 52 |

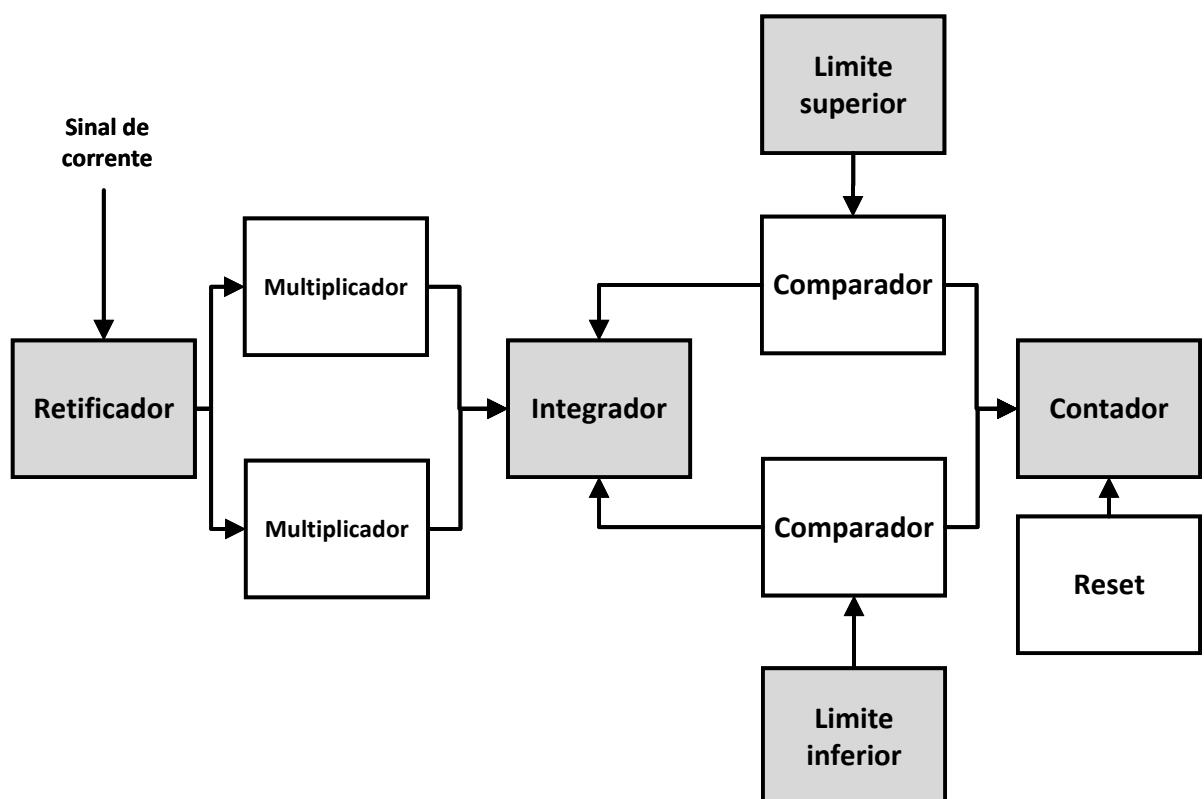

| Figura 28 – Estrutura de detecção do nível médio em sinais senoidais. . . . .                                                                                                                        | 53 |

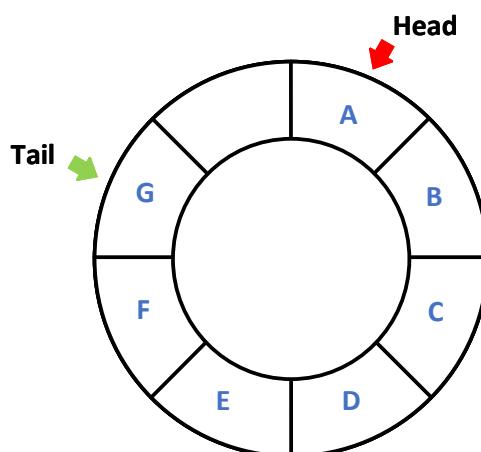

| Figura 29 – Exemplo conceitual de um <i>buffer</i> circular com 8 posições. . . . .                                                                                                                  | 54 |

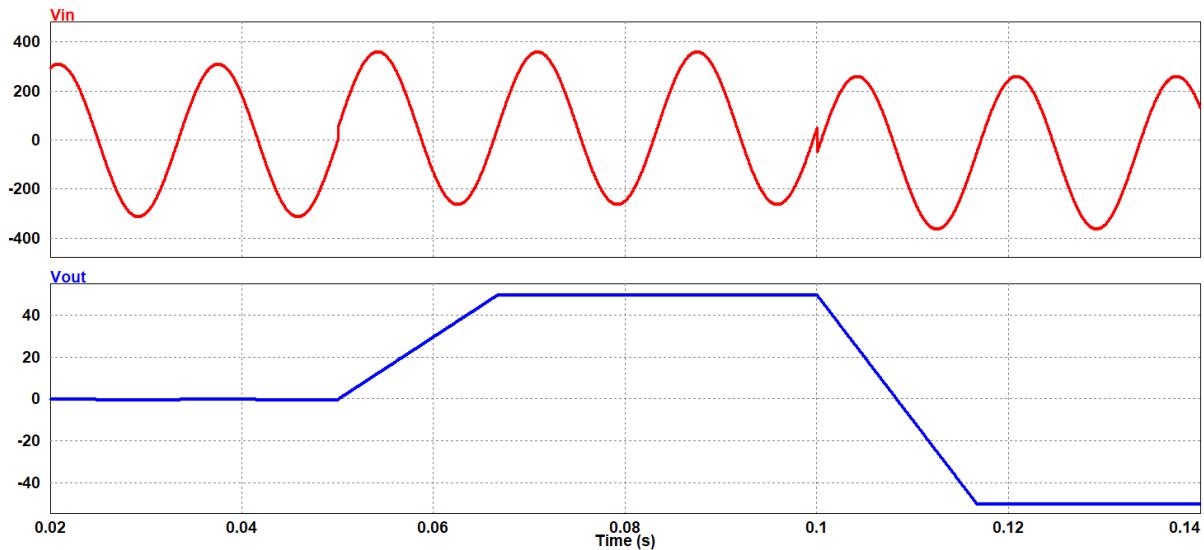

| Figura 30 – Forma de onda de tensão de entrada e nível médio obtido com a utilização de um FMM. . . . .                                                                                              | 55 |

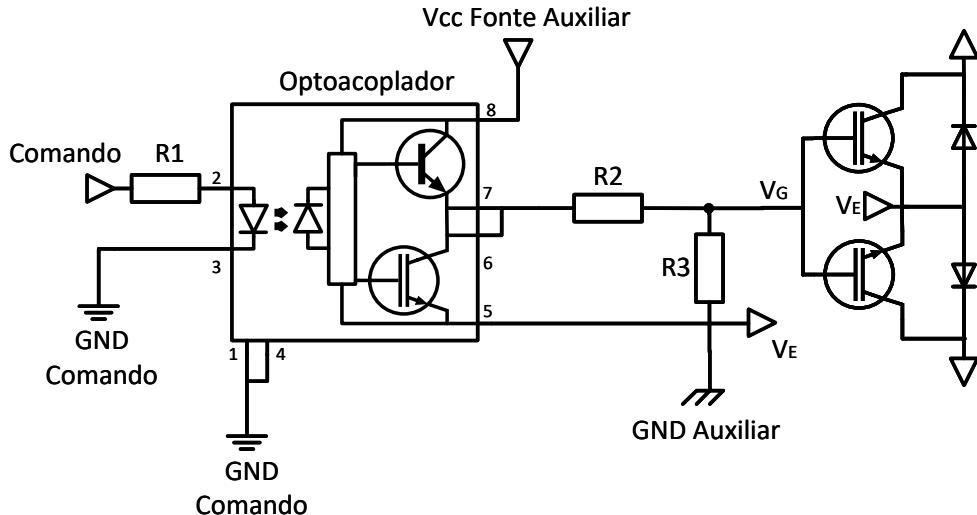

| Figura 31 – Circuito de <i>bypass</i> proposto. . . . .                                                                                                                                              | 57 |

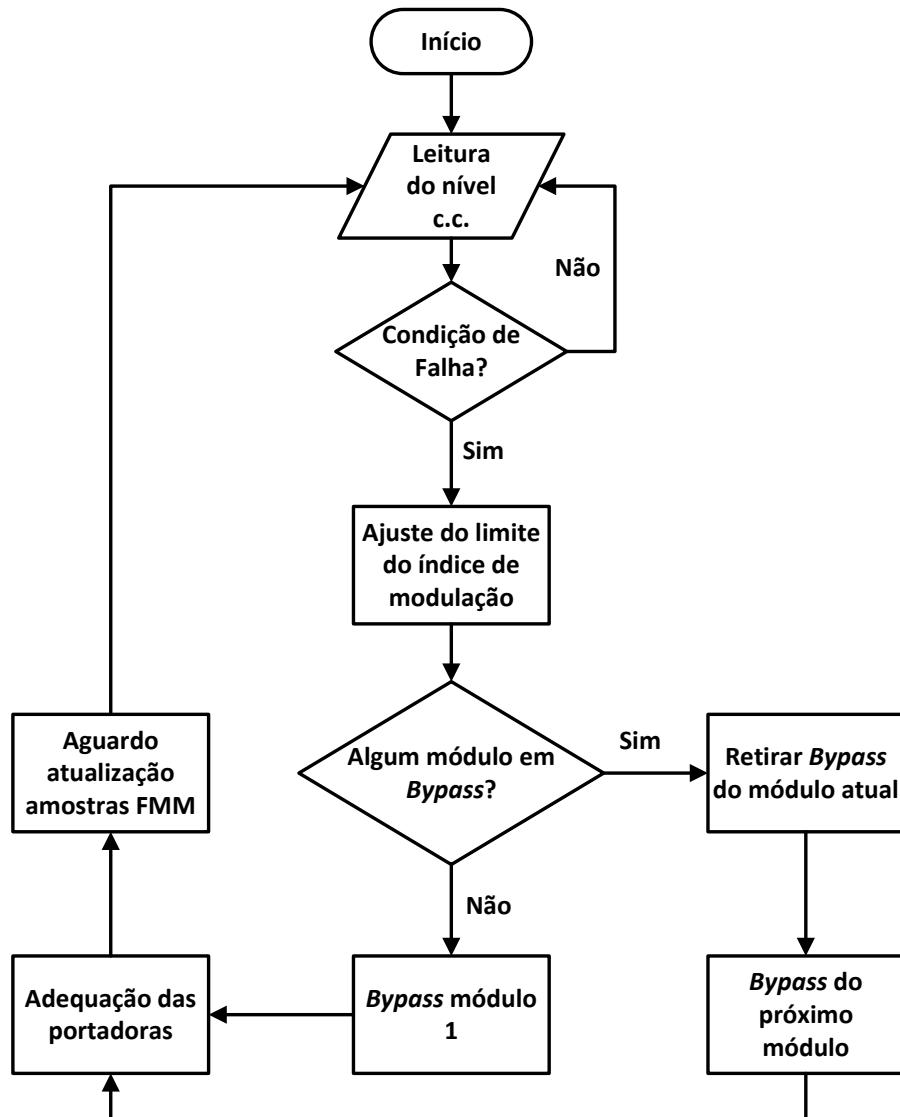

| Figura 32 – Fluxograma de funcionamento da rotina de testes do módulo danificado. . . .                                                                                                              | 58 |

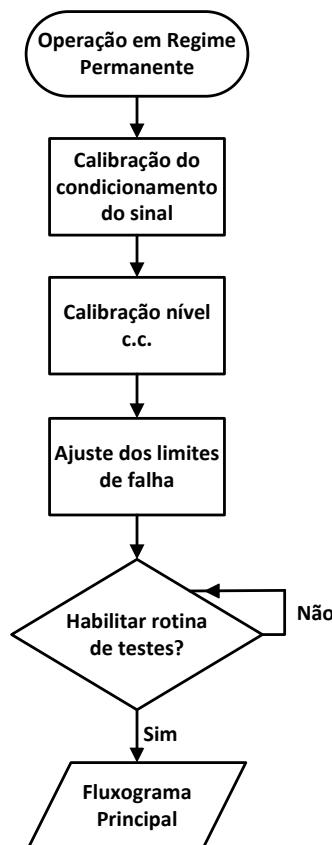

| Figura 33 – Fluxograma de inicialização do conversor. . . . .                                                                                                                                        | 59 |

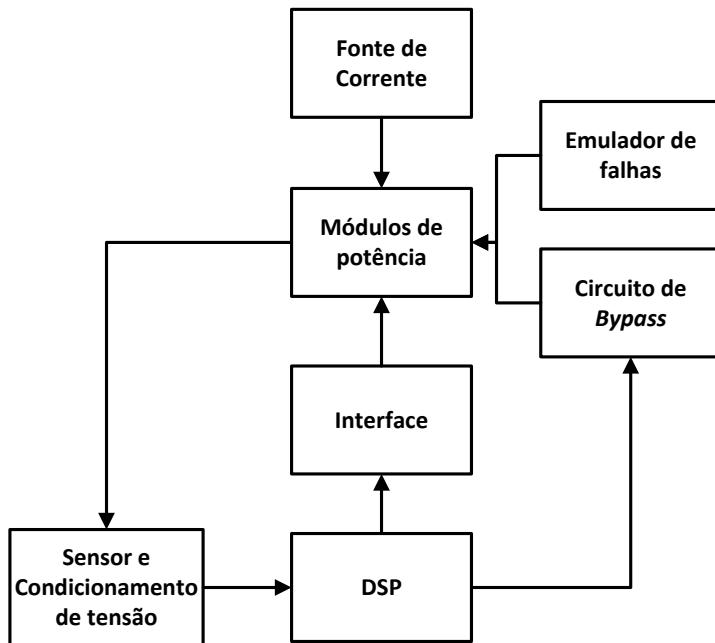

| Figura 34 – Diagrama de blocos representativo da estrutura implementada para validação experimental. . . . .                                                                                         | 62 |

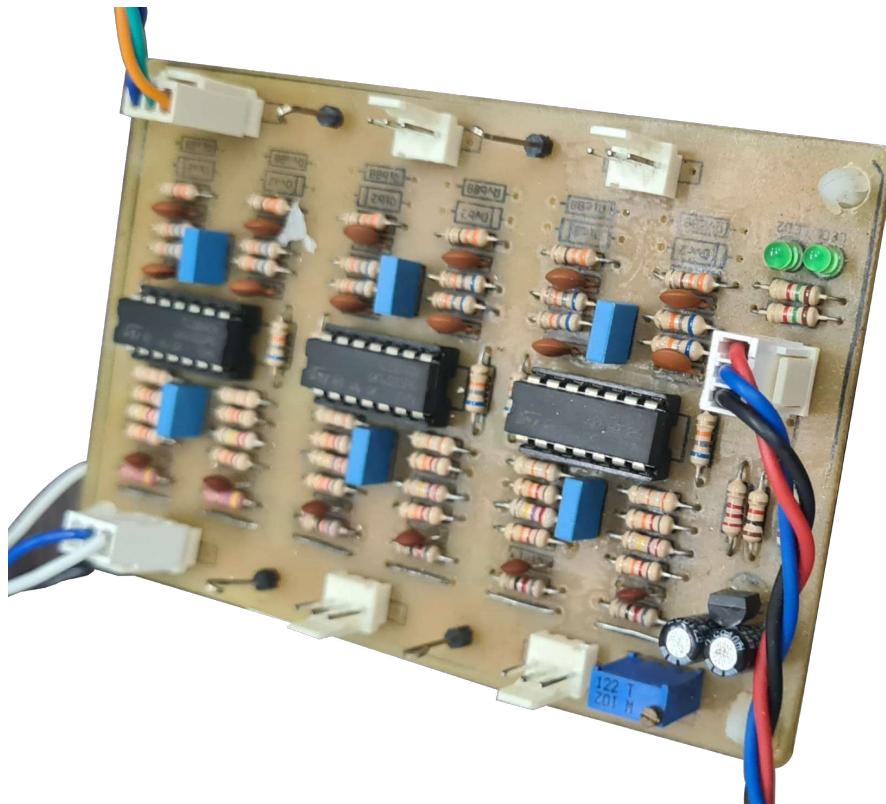

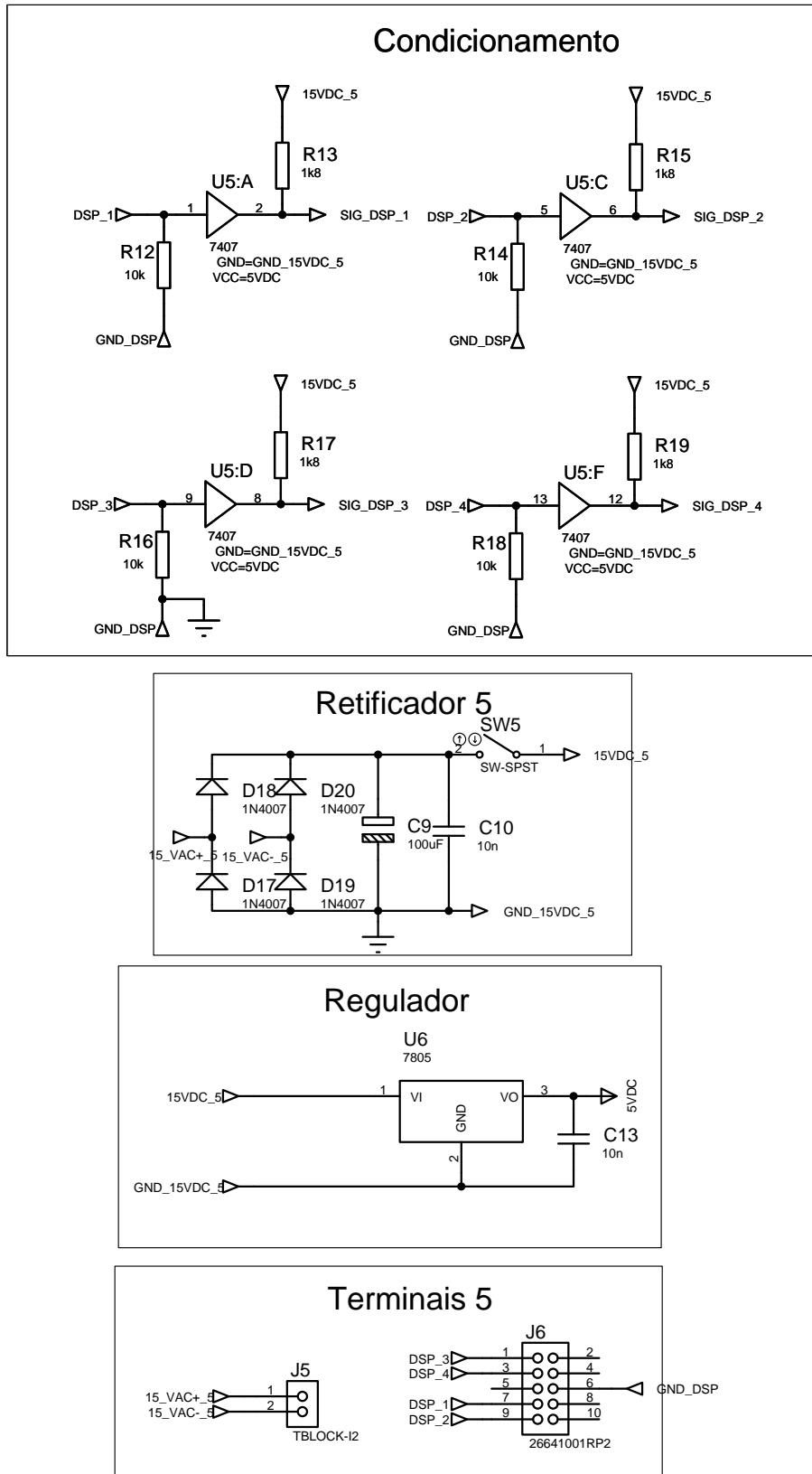

| Figura 35 – Placa de condicionamento do sinal de leitura de tensão de saída. . . . .                                                                                                                 | 63 |

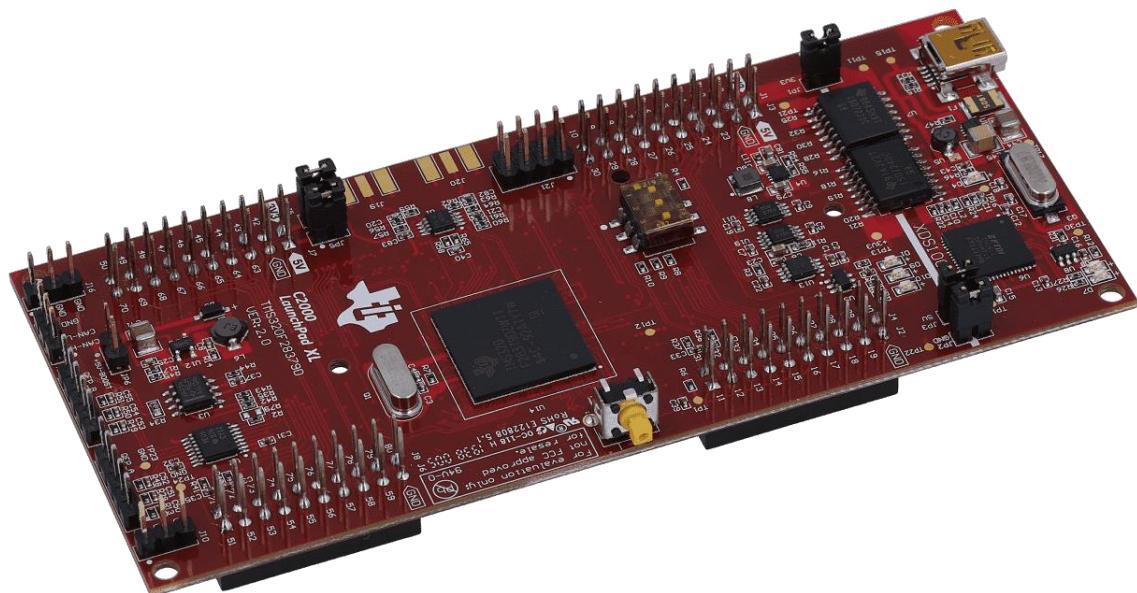

| Figura 36 – Imagem do kit LAUNCHXL-F28379D com o DSP utilizado. . . . .                                                                                                                              | 63 |

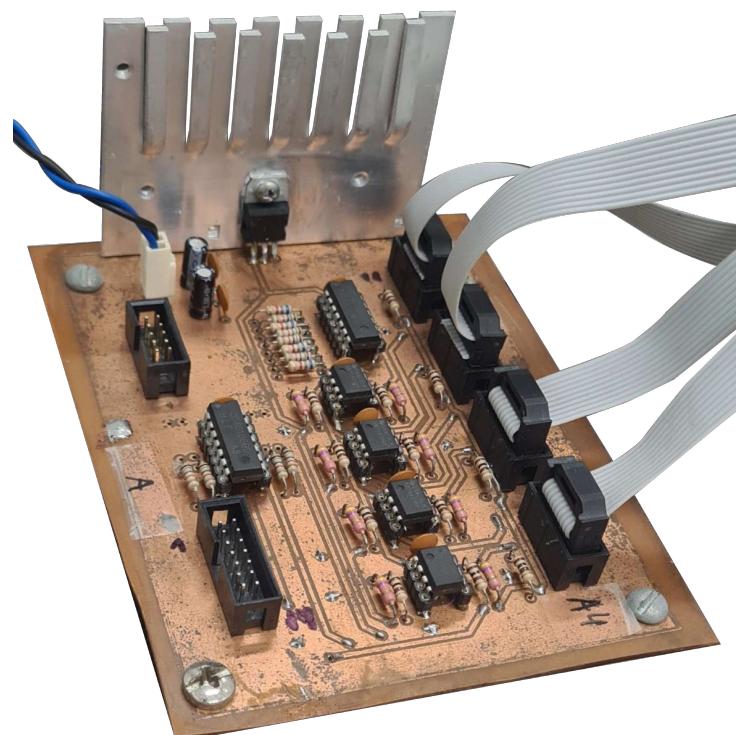

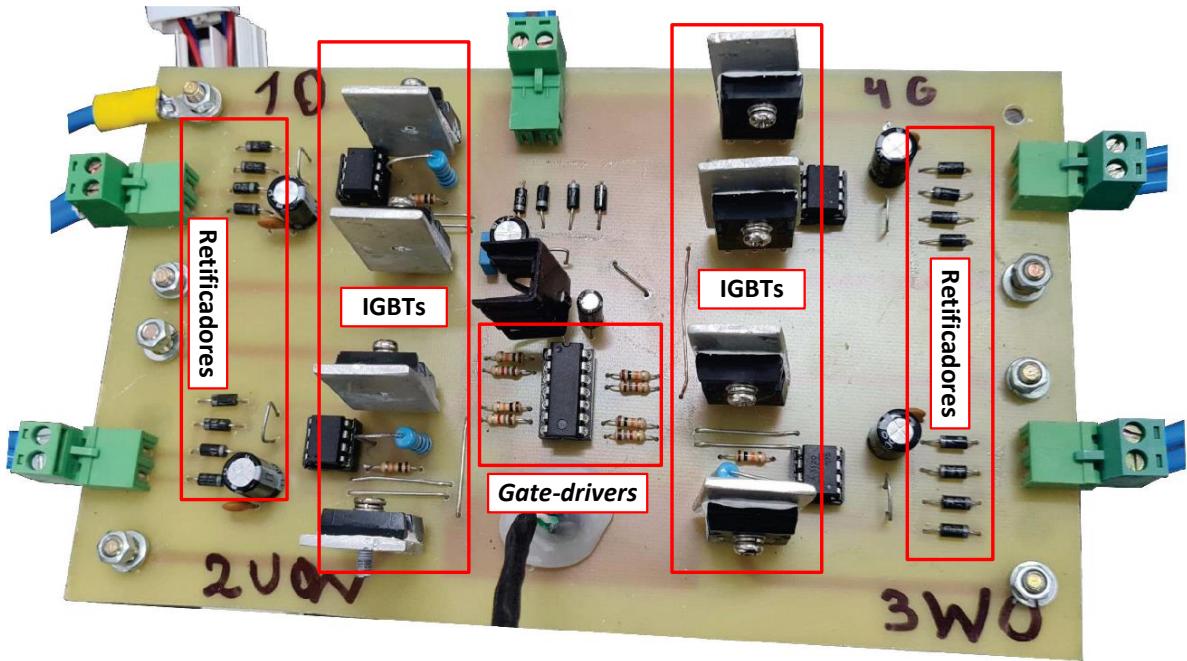

| Figura 37 – Placa de interface entre DSP e os <i>gate-drivers</i> dos módulos de potência. . . .                                                                                                     | 64 |

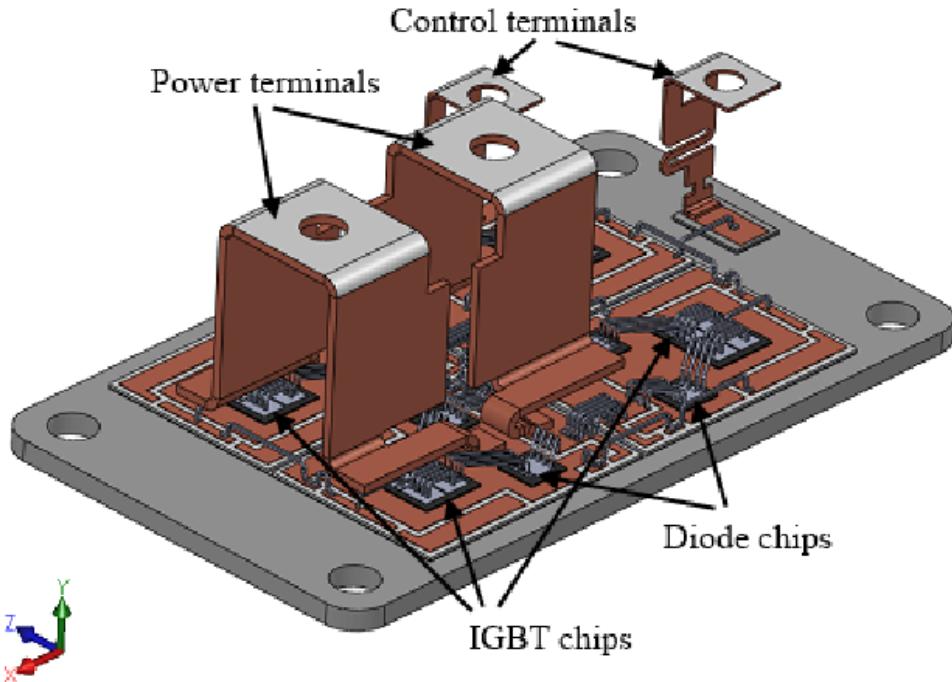

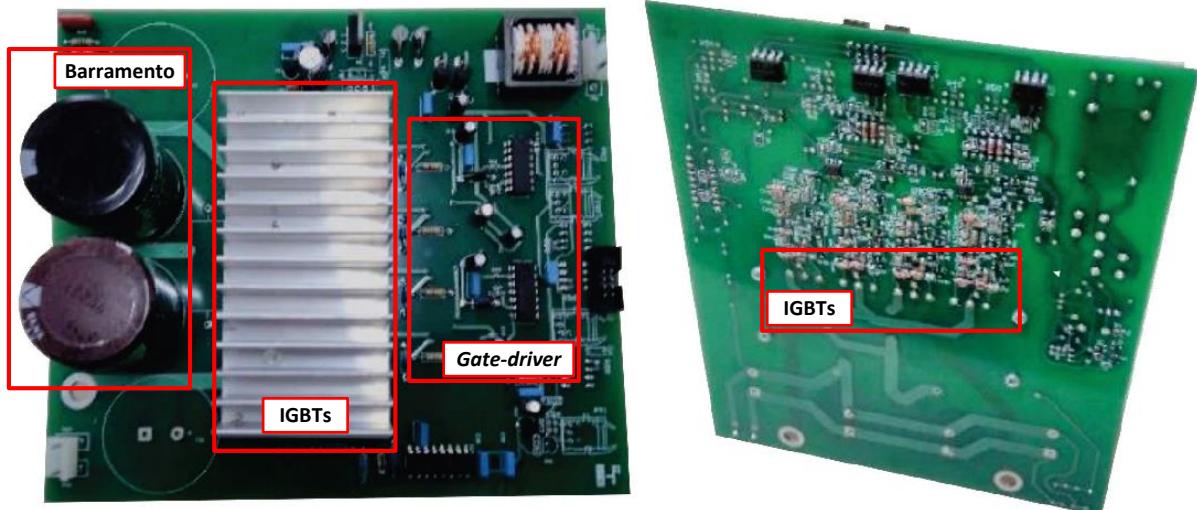

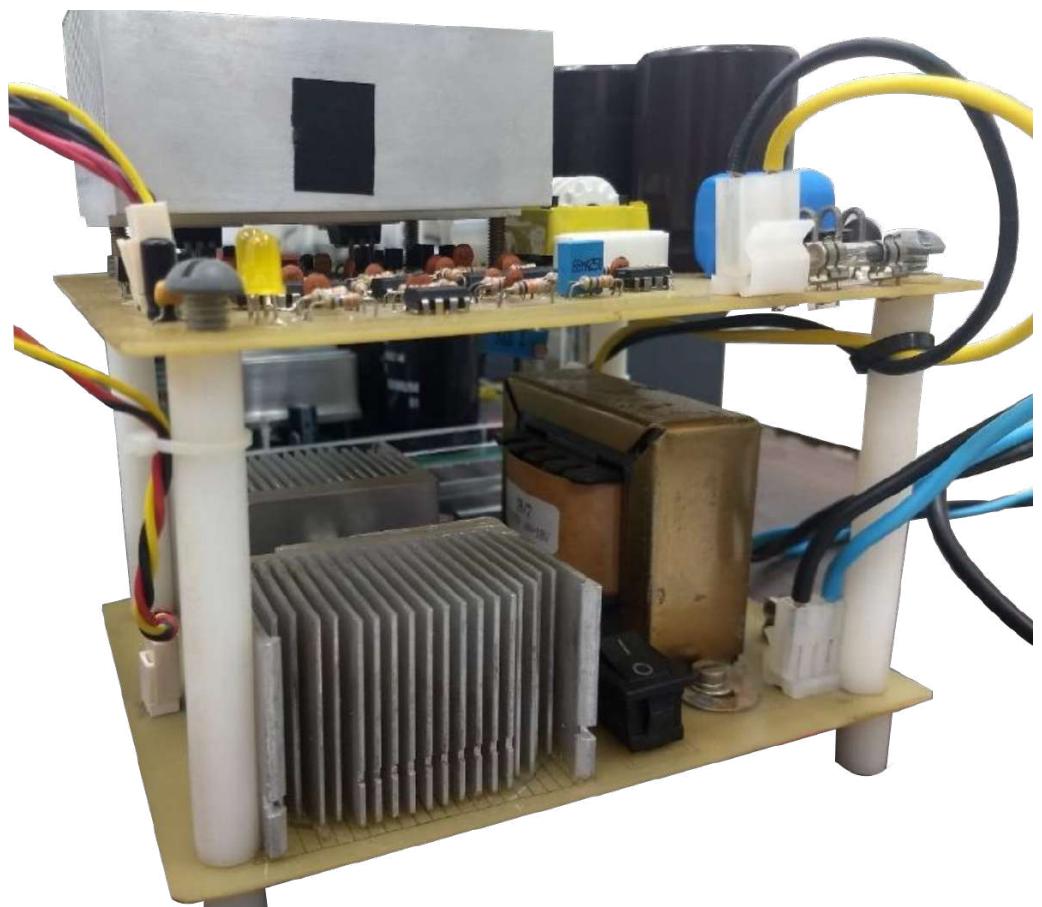

| Figura 38 – Módulo ponte completa utilizado. . . . .                                                                                                                                                 | 65 |

| Figura 39 – Fonte de corrente em média frequência para alimentação isolada dos módulos. .                                                                                                            | 65 |

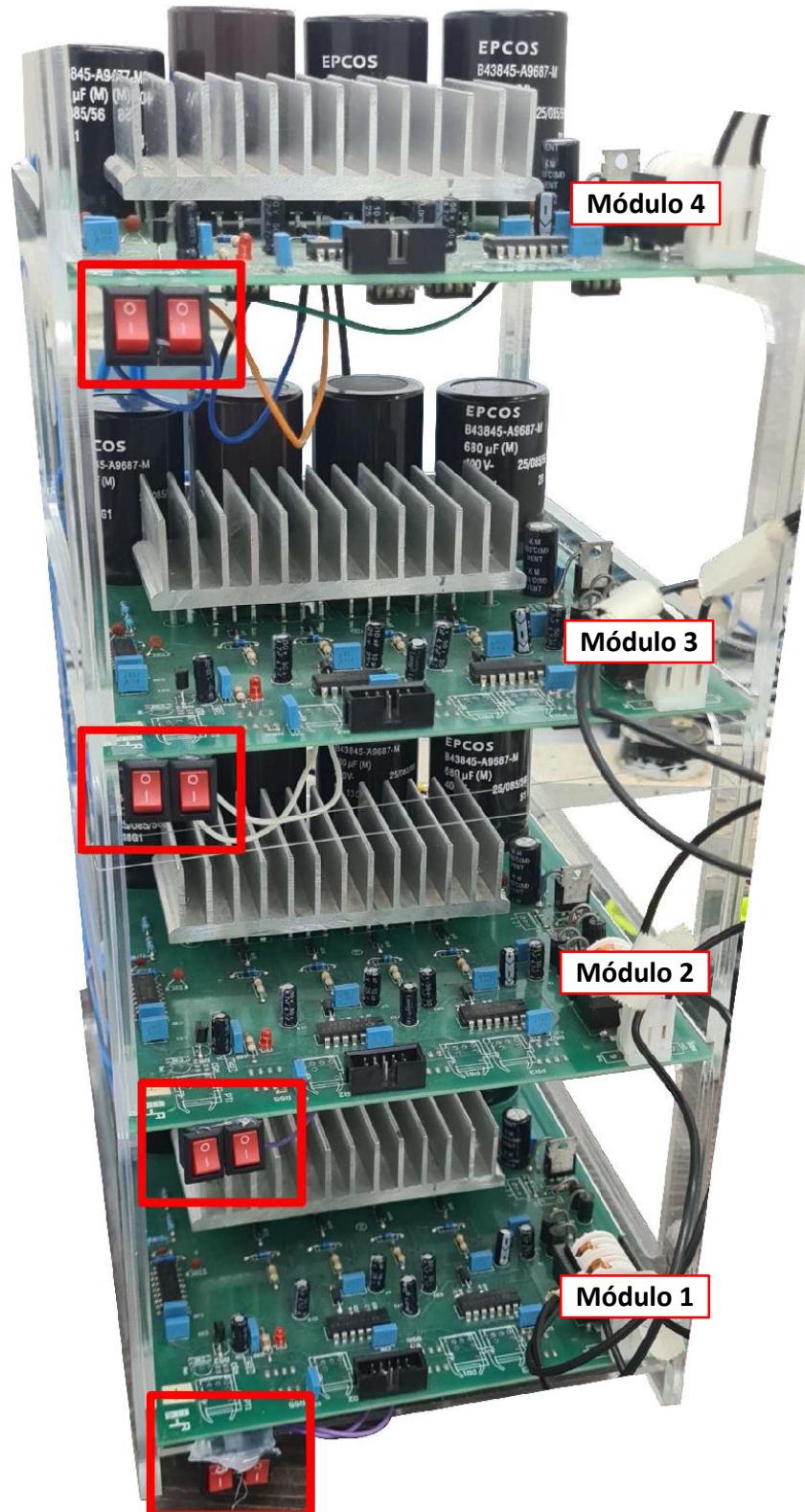

| Figura 40 – Conversor CHB utilizado, com chaves de emulação de falhas em evidência. .                                                                                                                | 67 |

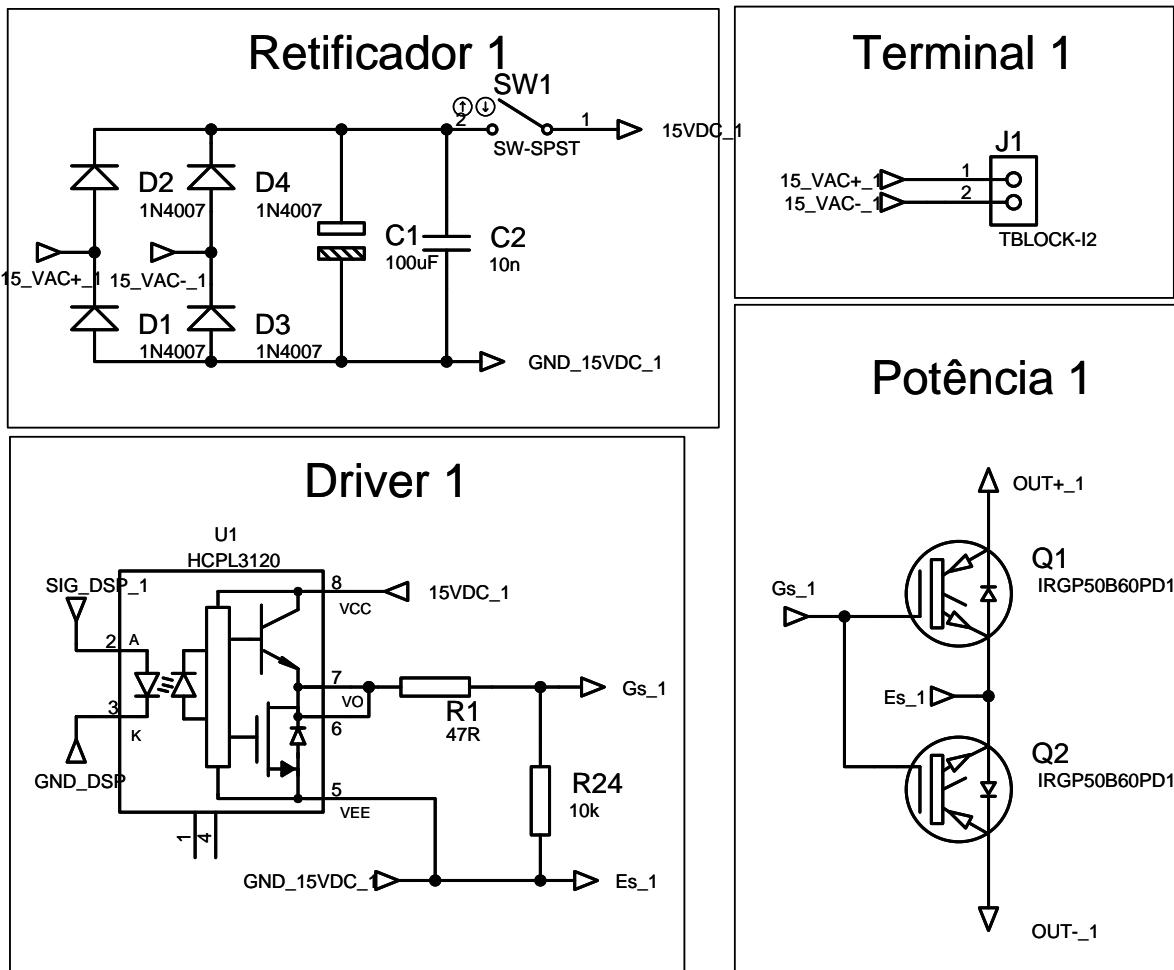

| Figura 41 – Circuito de <i>bypass</i> confeccionado. . . . .                                                                                                                                         | 68 |

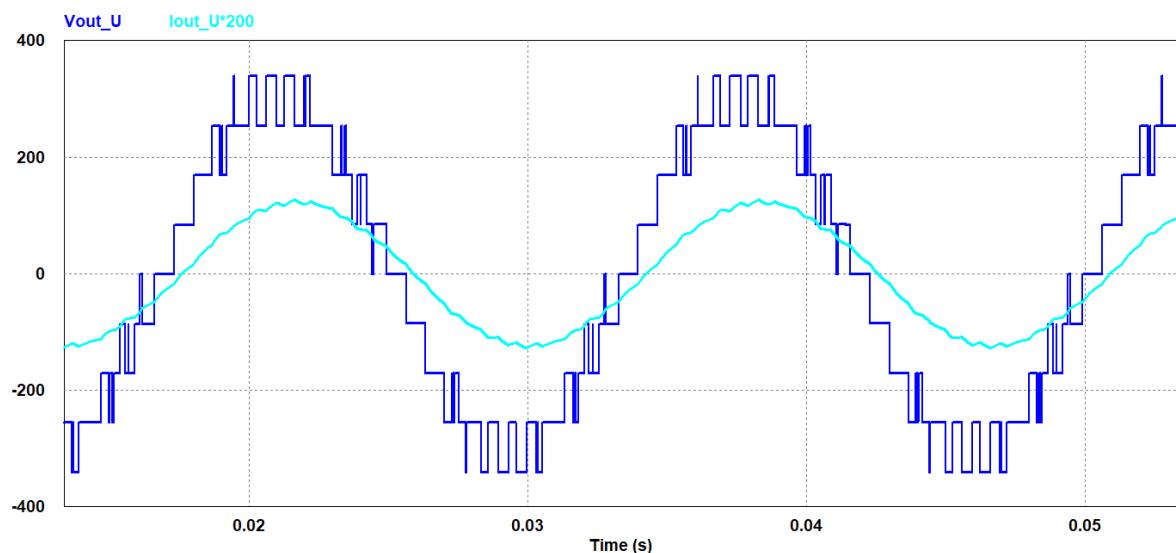

| Figura 42 – Formas de onda de tensão (Azul) [100 V/div] e corrente (Ciano) [500mA/div] de saída experimentais para funcionamento normal do conversor. . . . .                                        | 69 |

| Figura 43 – Formas de onda de tensão (Azul) e corrente (Ciano) de saída via simulação para funcionamento normal do conversor. . . . .                                                                | 69 |

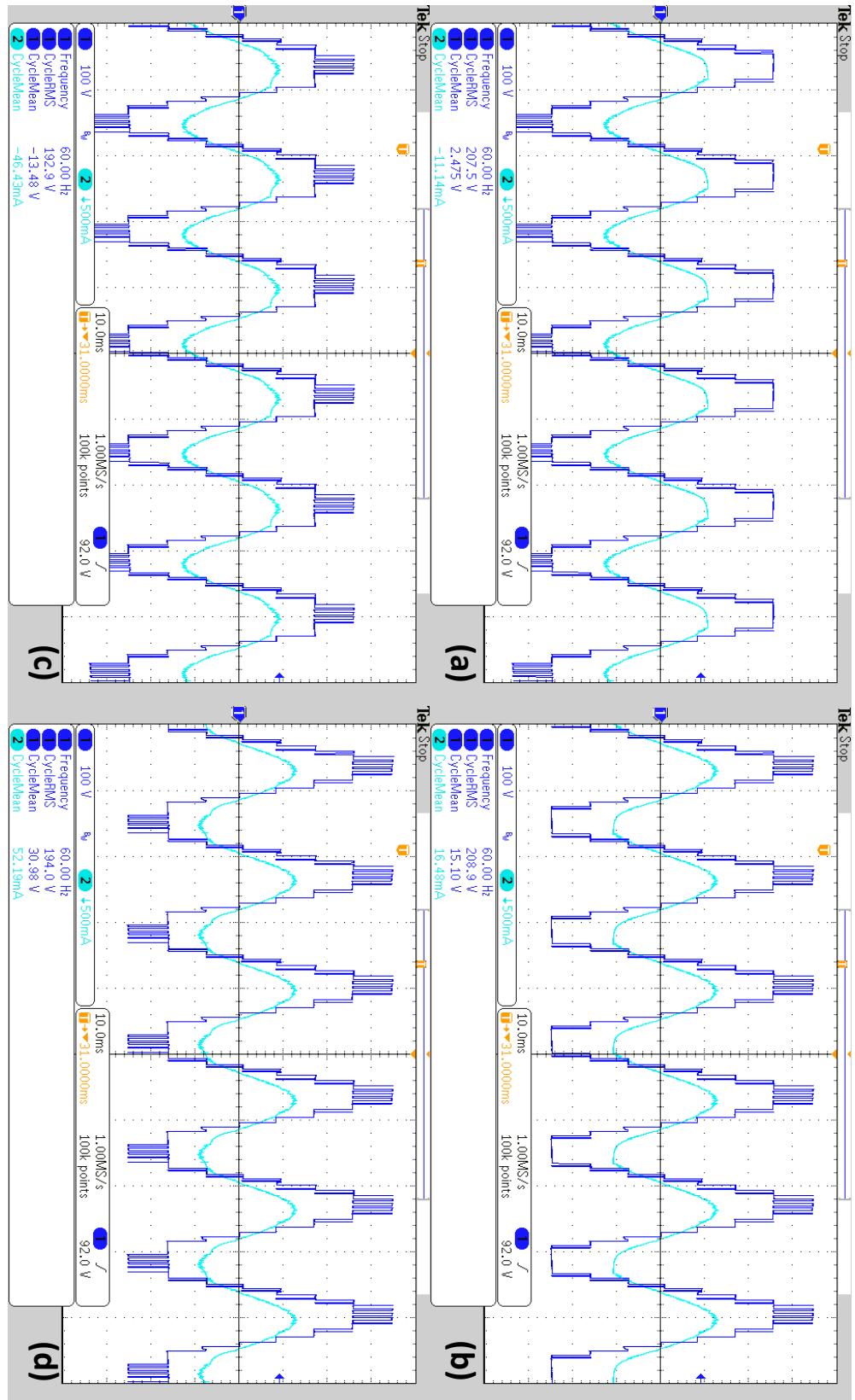

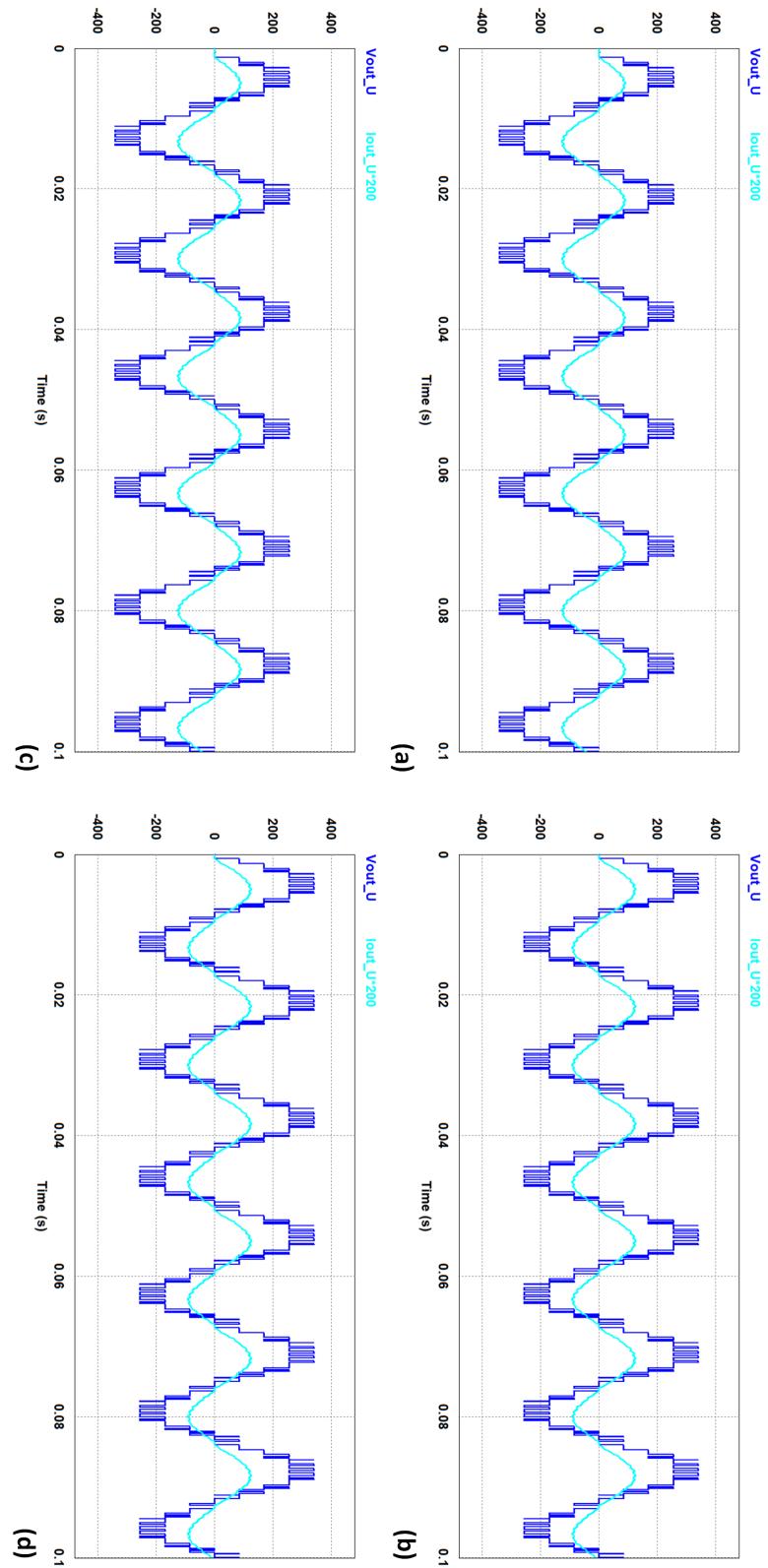

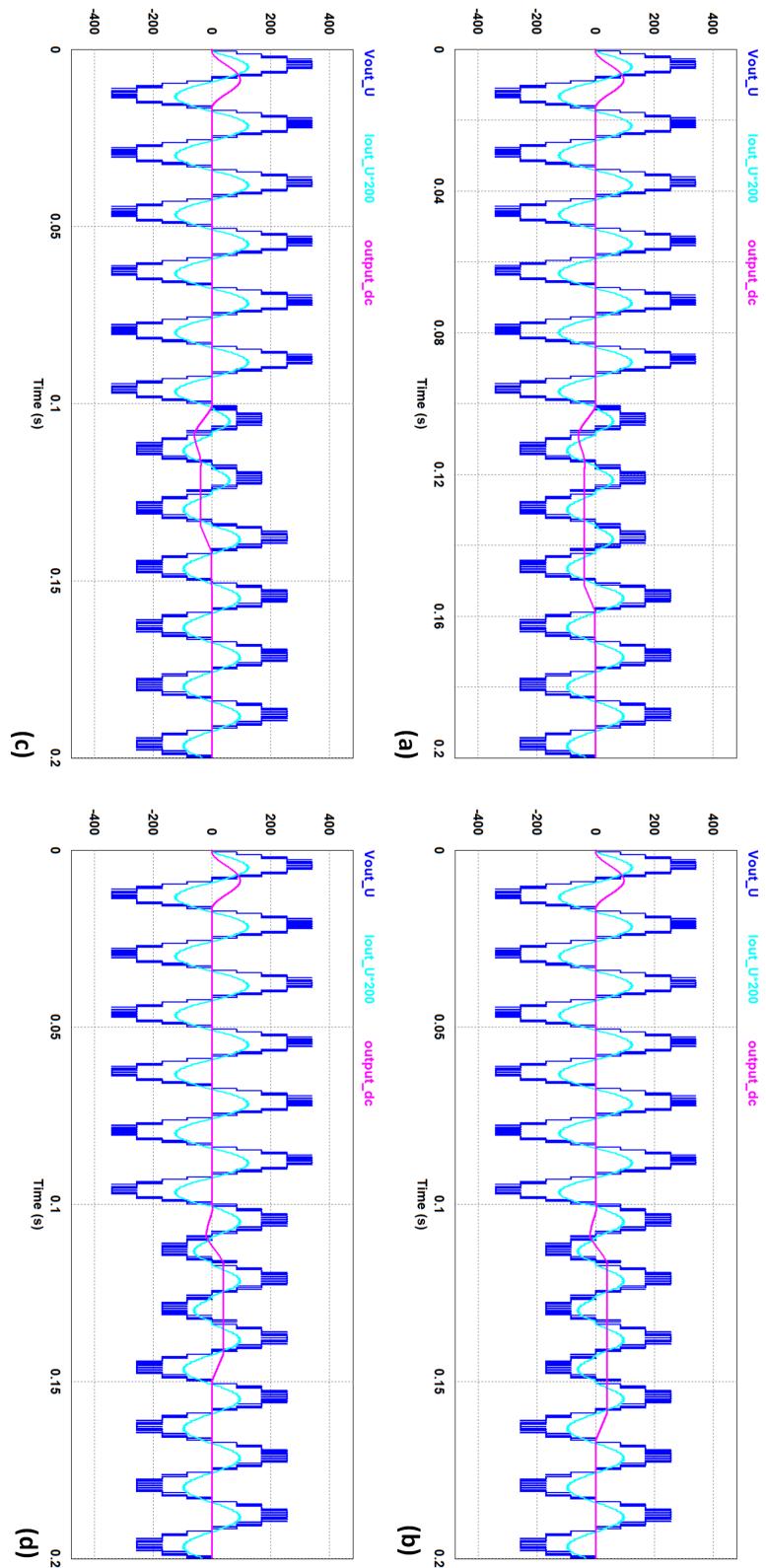

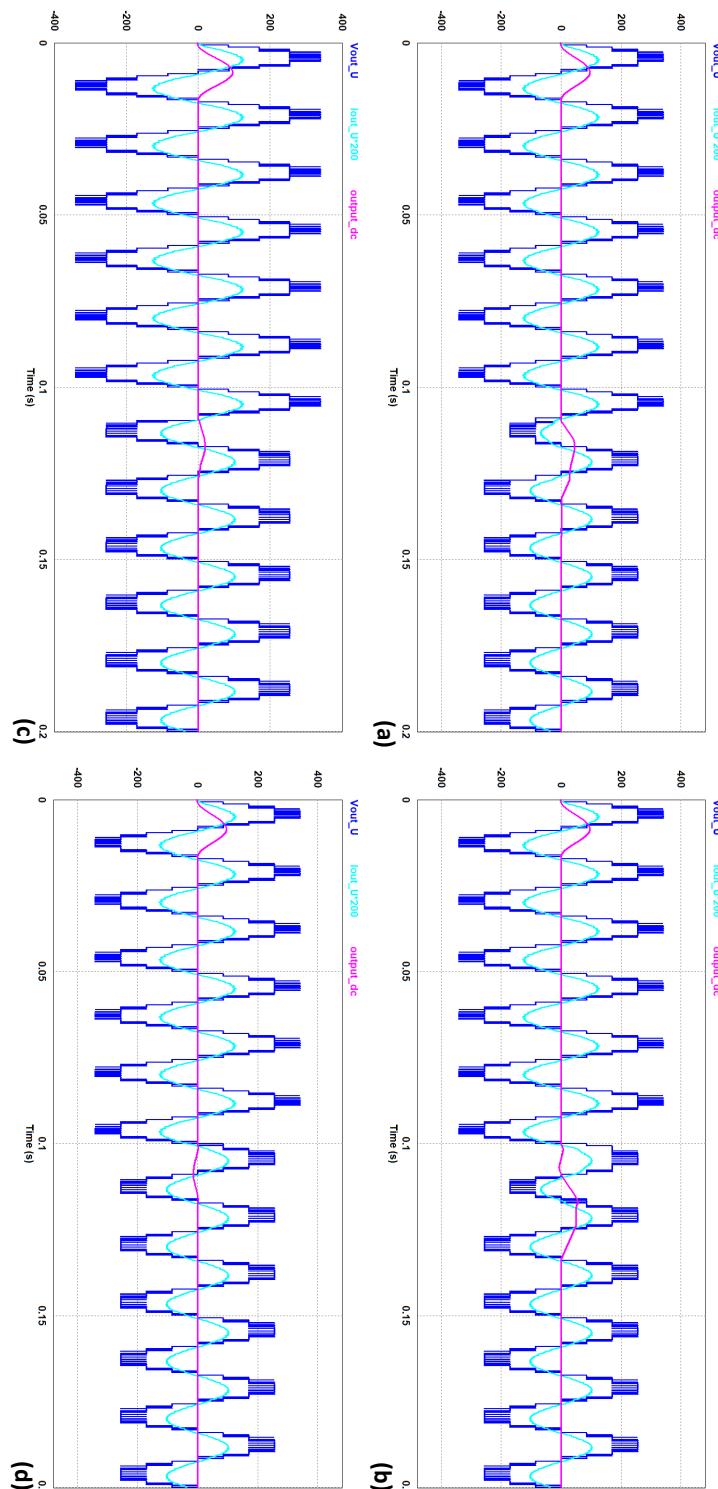

| Figura 44 – Formas de onda de tensão (Azul) [100 V/div] e corrente (Ciano) [500mA/div] de saída experimentais para condição de falha dos interruptores: (a) G14, (b) G16, (c) G10 e (d) G12. . . . . | 72 |

| Figura 45 – Formas de onda de tensão (Azul) [100 V/div] e corrente (Ciano) [500mA/div] de saída experimentais para condição de falha dos interruptores: (a) G6, (b) G8, (c) G2 e (d) G4. . . . .     | 73 |

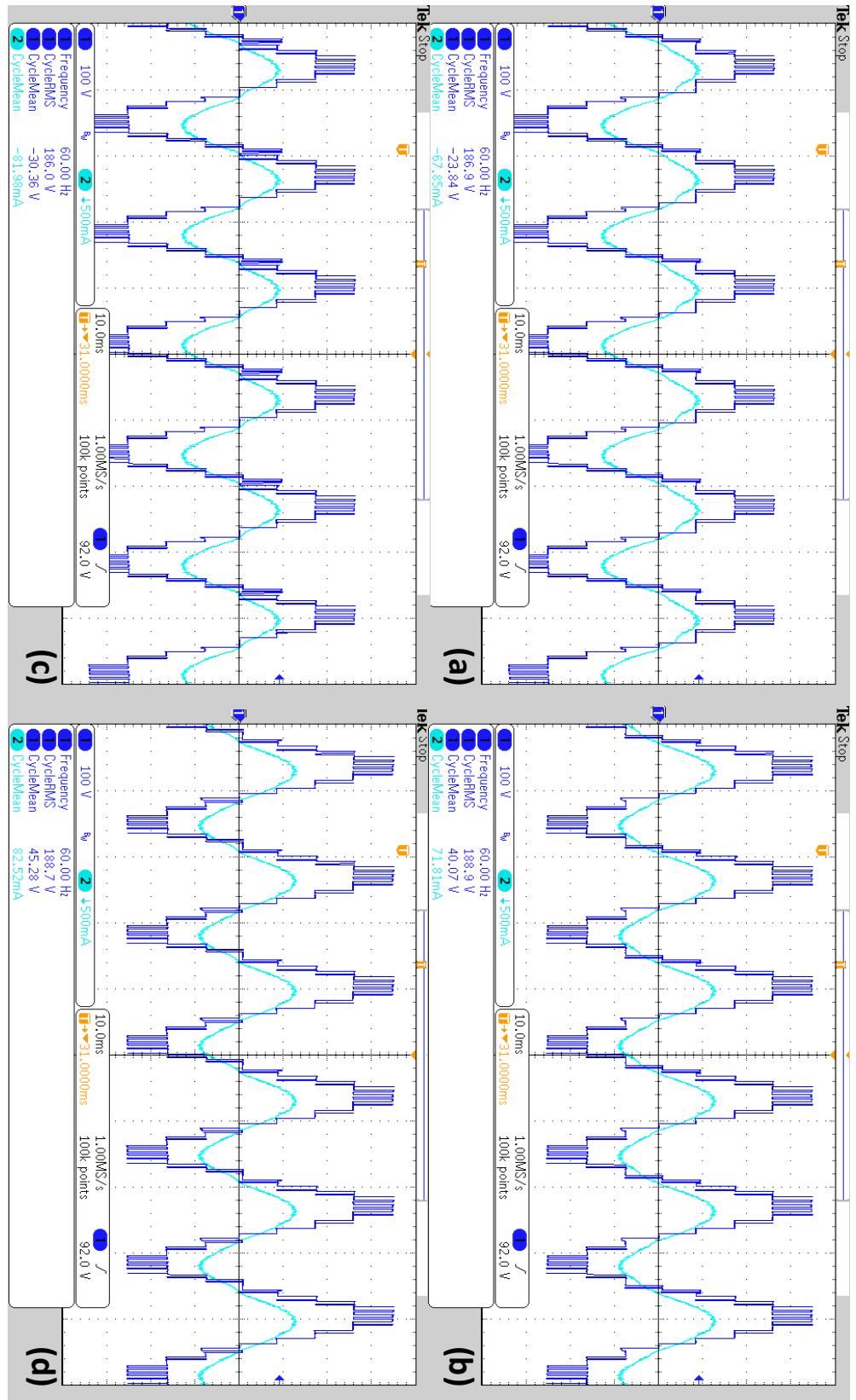

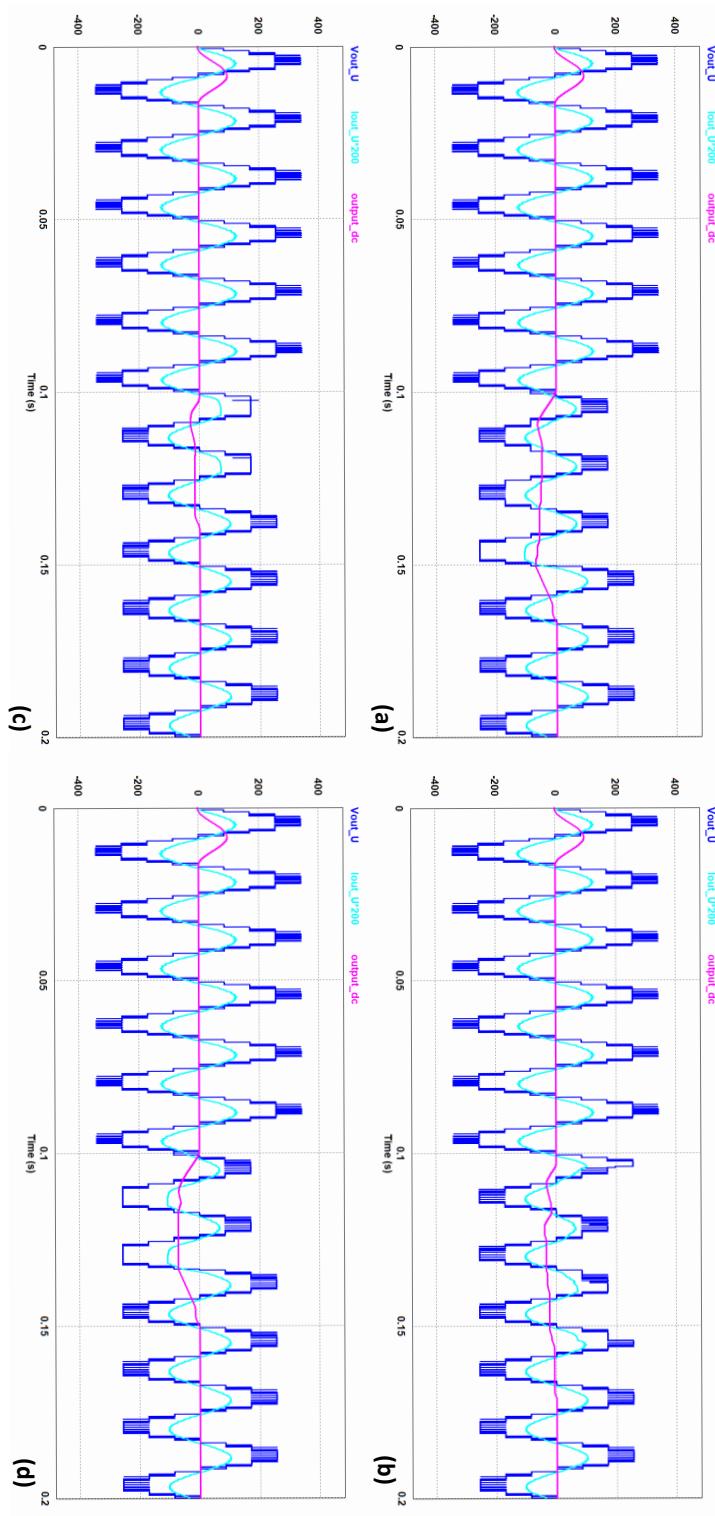

| Figura 46 – Formas de onda de tensão (Azul) e corrente (Ciano) de saída via simulação para condição de falha dos interruptores: (a) G13, (b) G15, (c) G9 e (d) G11. .                                | 74 |

|                                                                                                                                                                                                                                                                                                                                                  |     |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 47 – Formas de onda de tensão (Azul) e corrente (Ciano) de saída via simulação para condição de falha dos interruptores: <b>(a)</b> G5, <b>(b)</b> G7, <b>(c)</b> G1 e <b>(d)</b> G3. . . . .                                                                                                                                             | 75  |

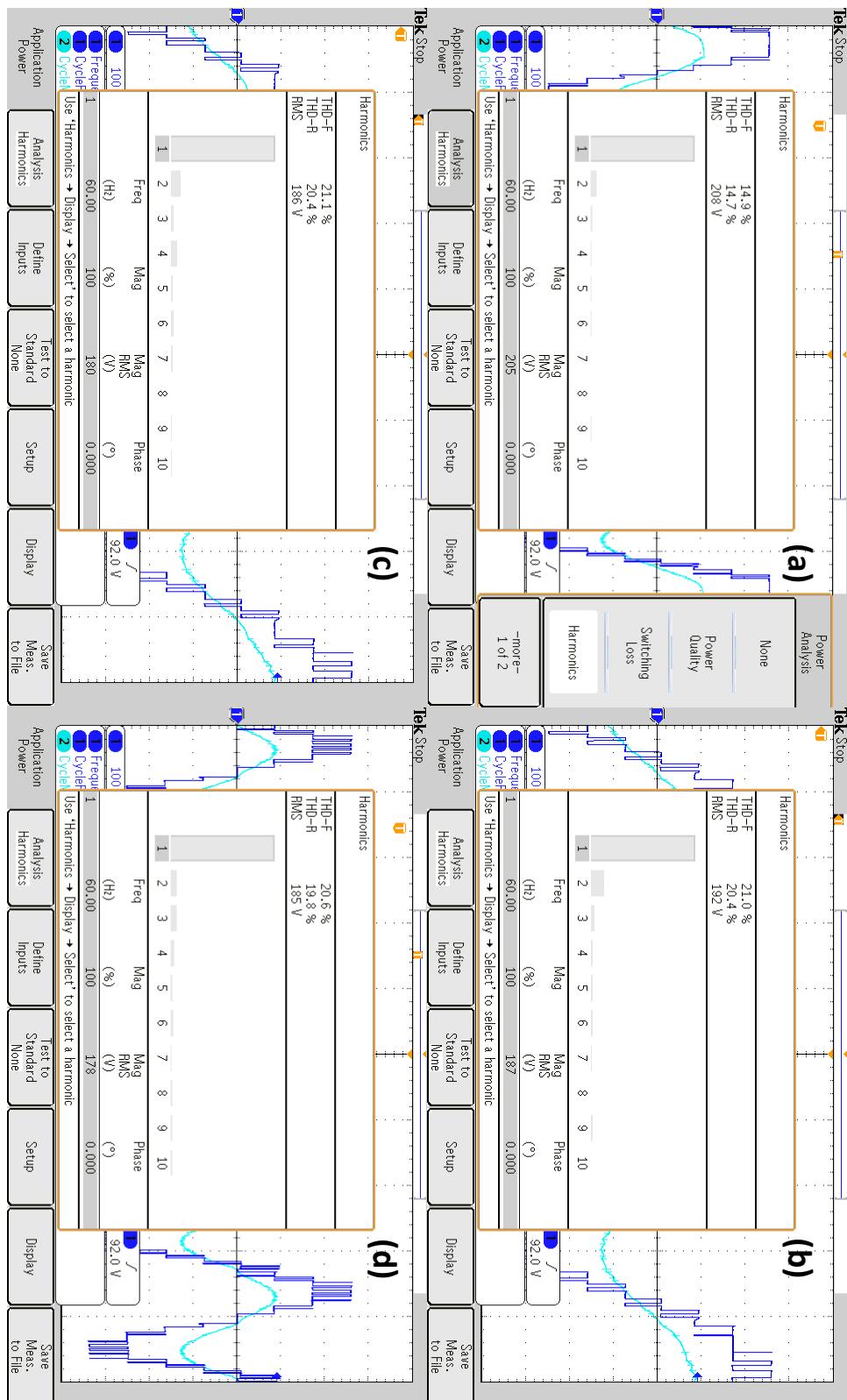

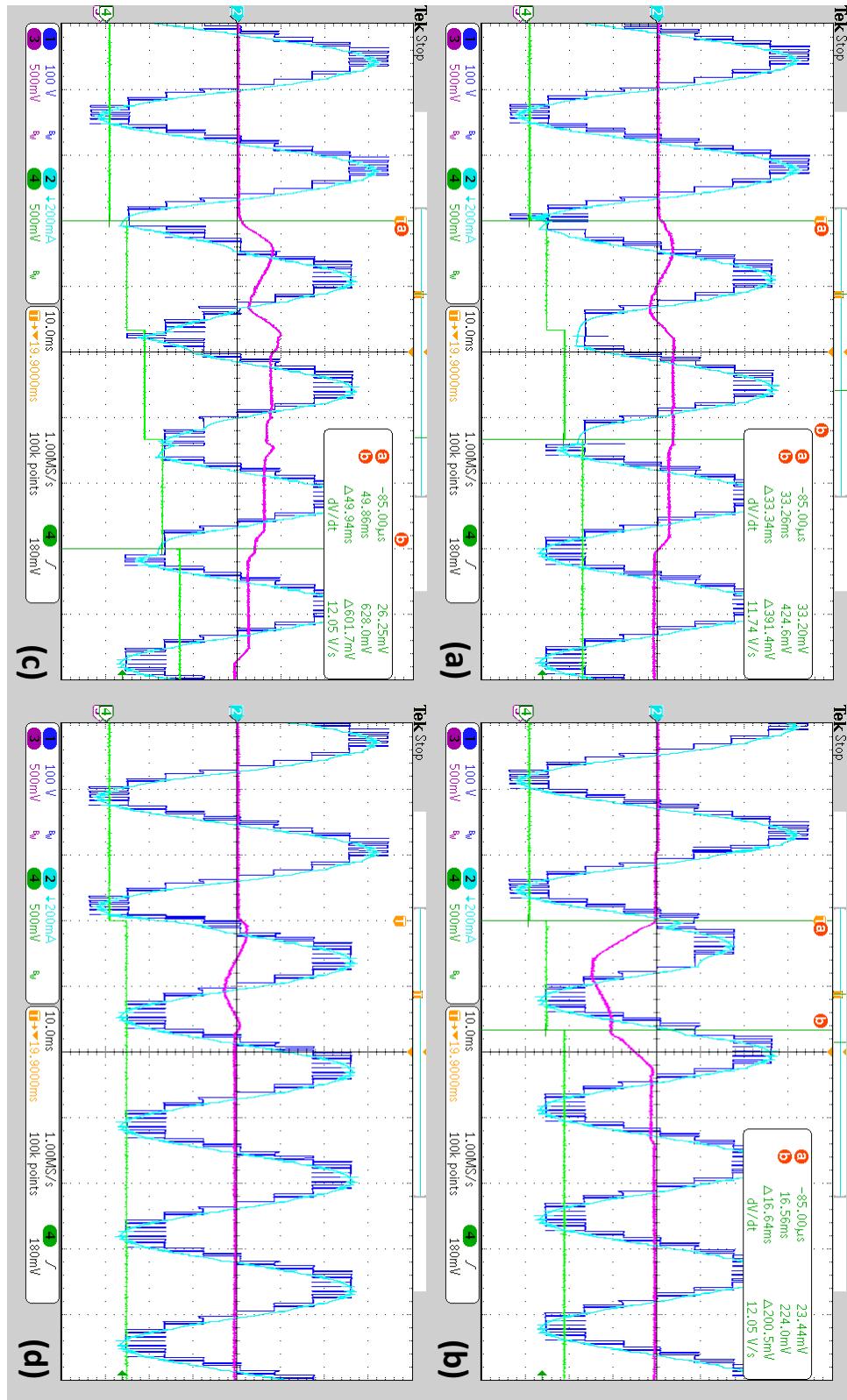

| Figura 48 – Espectros harmônicos experimentais da tensão de saída para condição de falha dos interruptores: <b>(a)</b> G14, <b>(b)</b> G10, <b>(c)</b> G6 e <b>(d)</b> G2. . . . .                                                                                                                                                               | 76  |

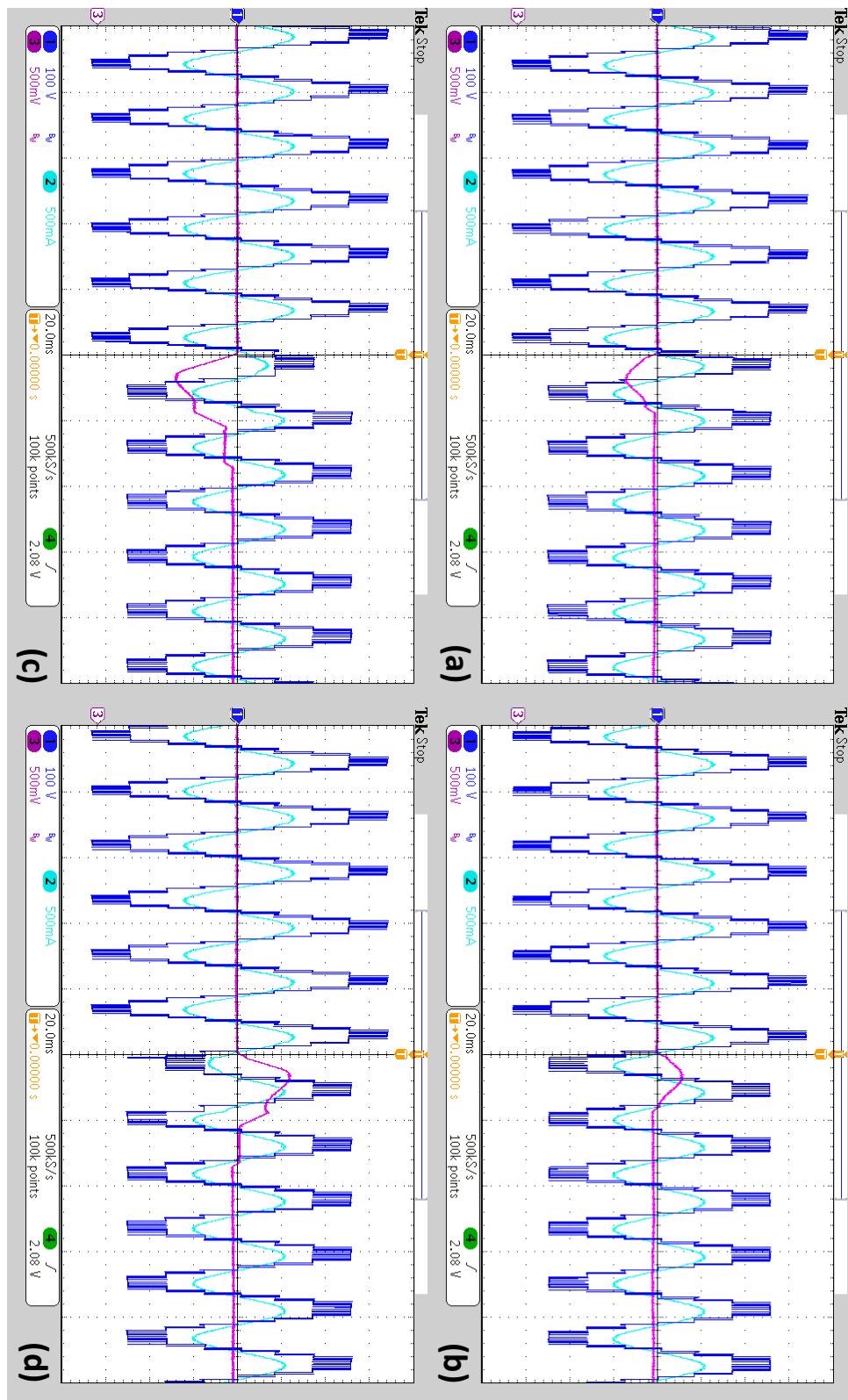

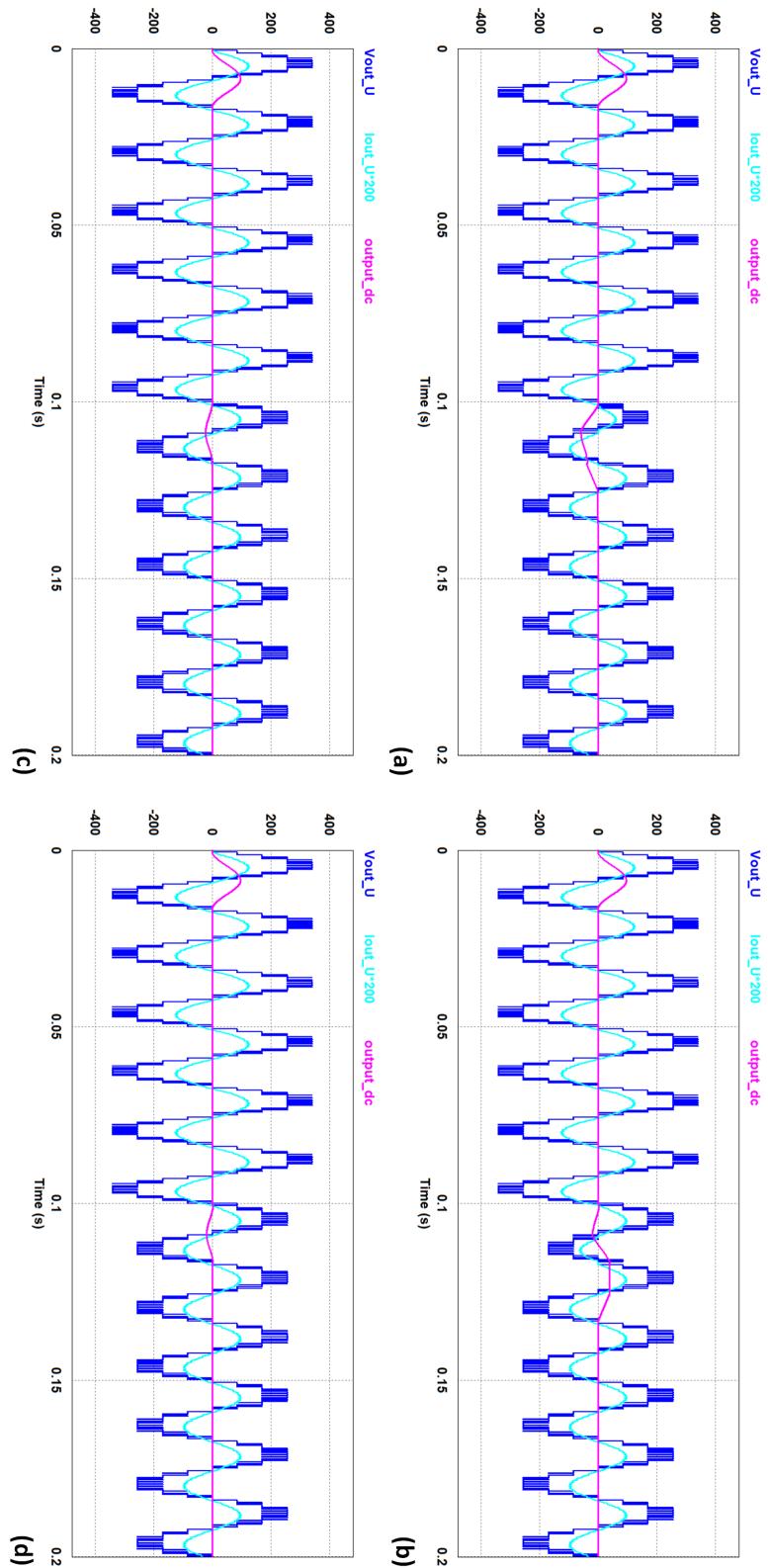

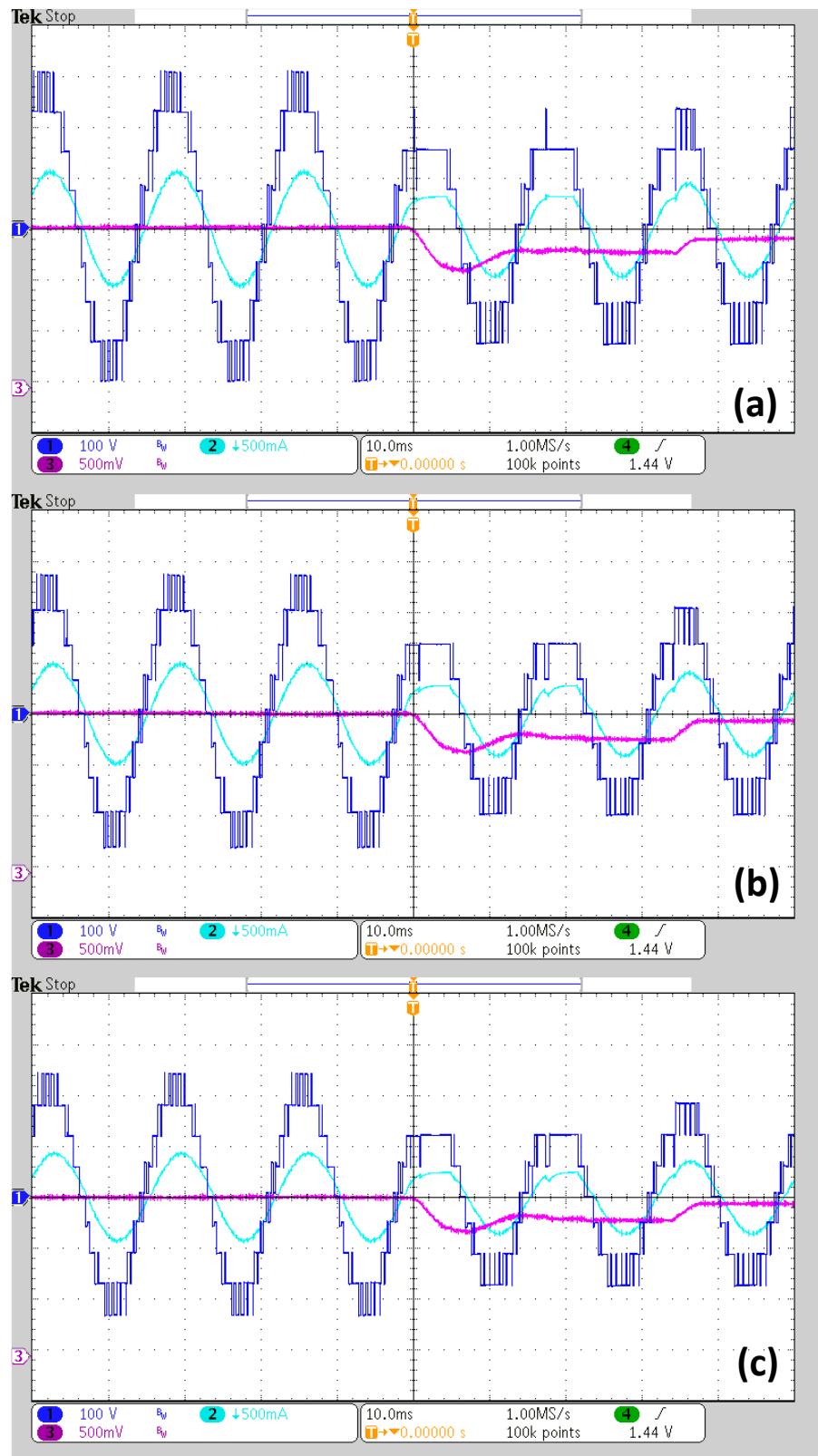

| Figura 49 – Formas de onda de tensão (Azul) [100 V/div], corrente (Ciano) [500mA/div] e nível c.c. (Rosa) [500 mV/div] de saída experimentais para identificação e correção de falha dos interruptores: <b>(a)</b> G14, <b>(b)</b> G16, <b>(c)</b> G10 e <b>(d)</b> G12. . . . .                                                                 | 79  |

| Figura 50 – Formas de onda de tensão (Azul) [100 V/div], corrente (Ciano) [500mA/div] e nível c.c. (Rosa) [500 mV/div] de saída experimentais para identificação e correção de falha dos interruptores: <b>(a)</b> G6, <b>(b)</b> G8, <b>(c)</b> G2 e <b>(d)</b> G4. . . . .                                                                     | 80  |

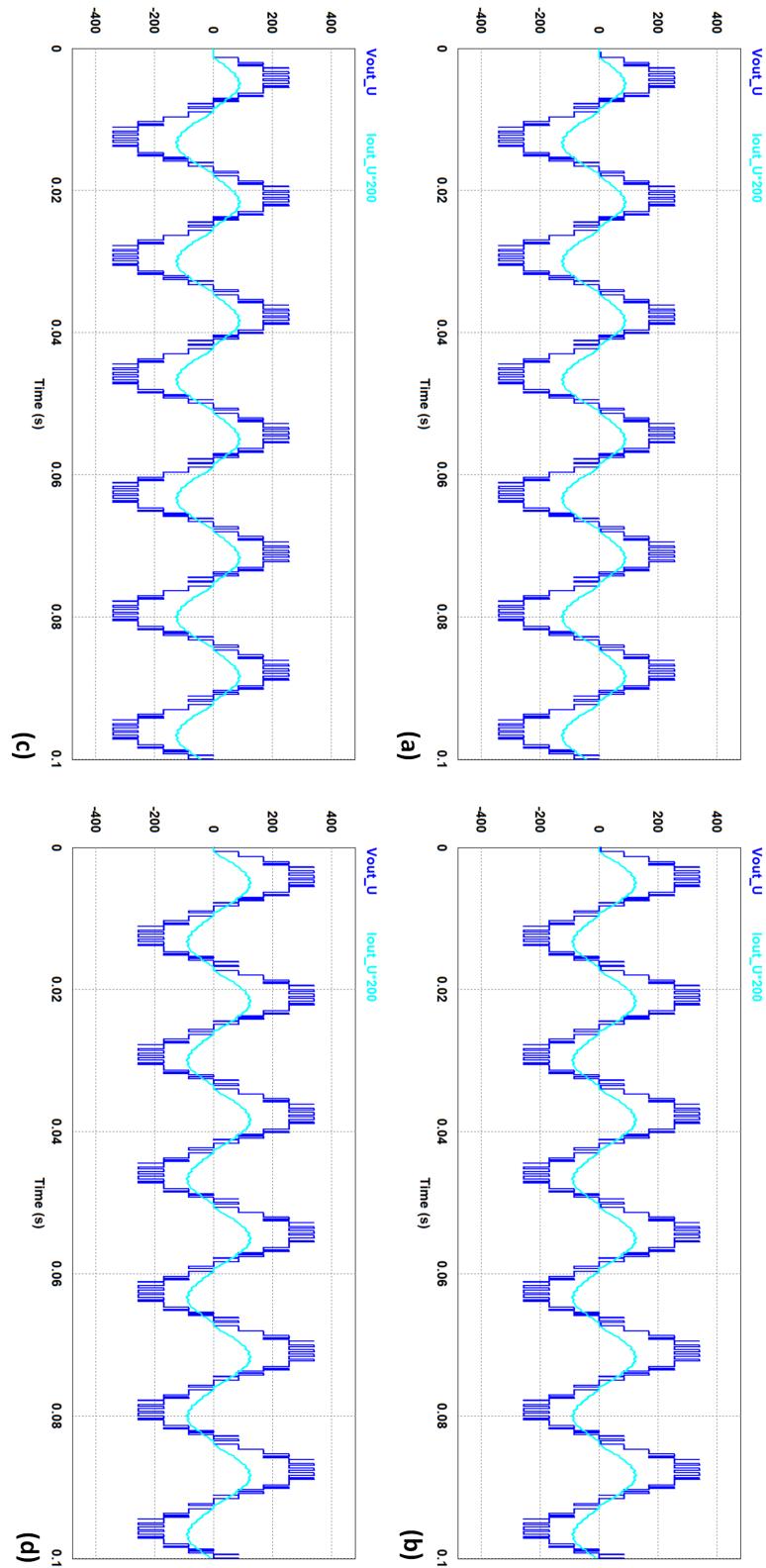

| Figura 51 – Formas de onda de tensão (Azul), corrente (Ciano) e nível c.c. (Rosa) de saída via simulação para identificação e correção de falha dos interruptores: <b>(a)</b> G13, <b>(b)</b> G15, <b>(c)</b> G9 e <b>(d)</b> G11. . . . .                                                                                                       | 81  |

| Figura 52 – Formas de onda de tensão (Azul), corrente (Ciano) e nível c.c. (Rosa) de saída via simulação para identificação e correção de falha dos interruptores: <b>(a)</b> G5, <b>(b)</b> G7, <b>(c)</b> G1 e <b>(d)</b> G3. . . . .                                                                                                          | 82  |

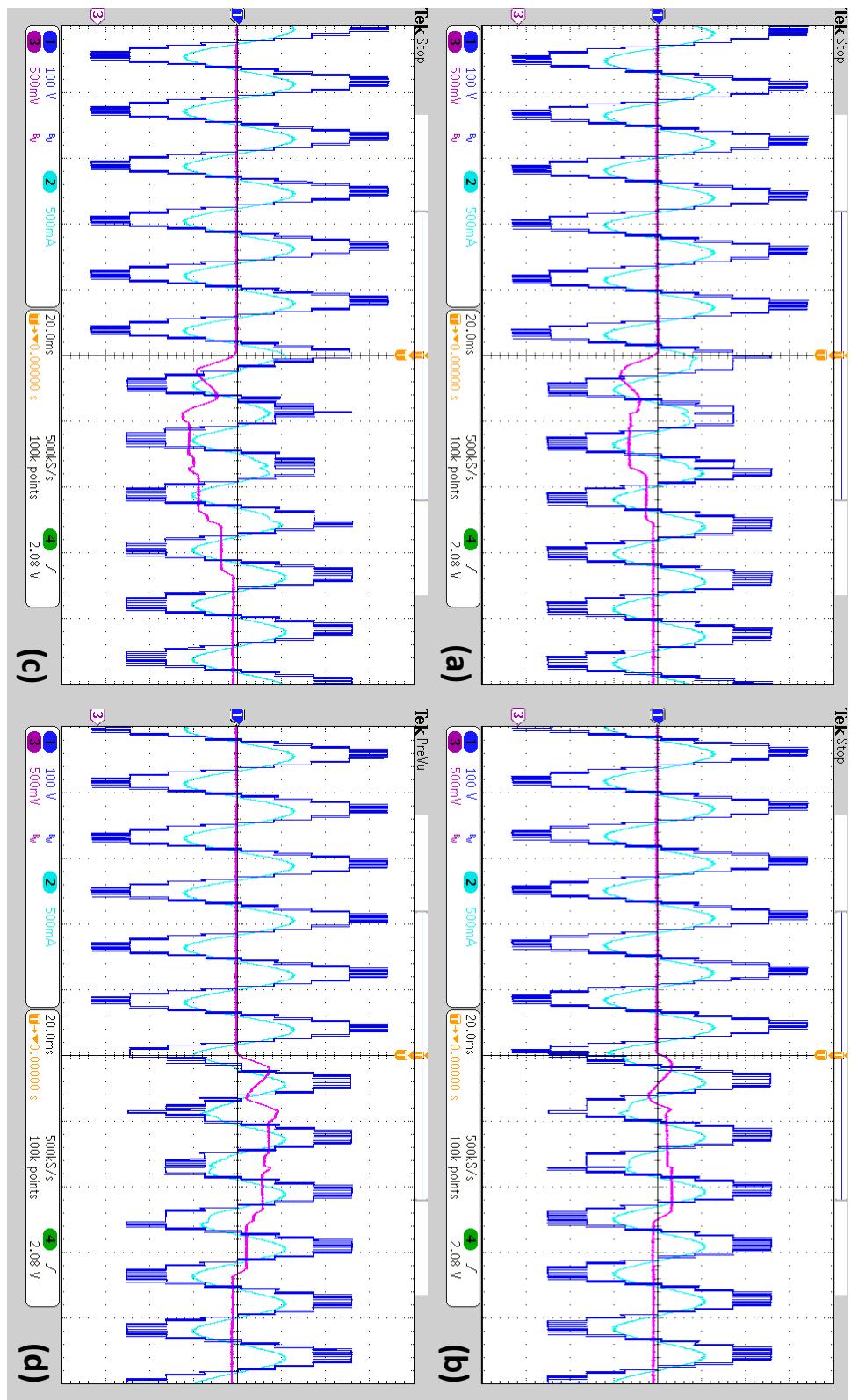

| Figura 53 – Formas de onda de tensão (Azul) [100 V/div], corrente (Ciano) [500mA/div] e nível c.c. (Rosa) [500 mV/div] de saída experimentais com identificação do módulo em <i>bypass</i> (Verde) [500 mV/div] para identificação e correção de falha dos interruptores: <b>(a)</b> G14, <b>(b)</b> G10, <b>(c)</b> G6 e <b>(d)</b> G2. . . . . | 83  |

| Figura 54 – Parâmetros qualitativos para formas de onda de tensão e corrente pré ( <b>(a)</b> e <b>(c)</b> ) e pós ( <b>(b)</b> e <b>(d)</b> ) falha. . . . .                                                                                                                                                                                    | 85  |

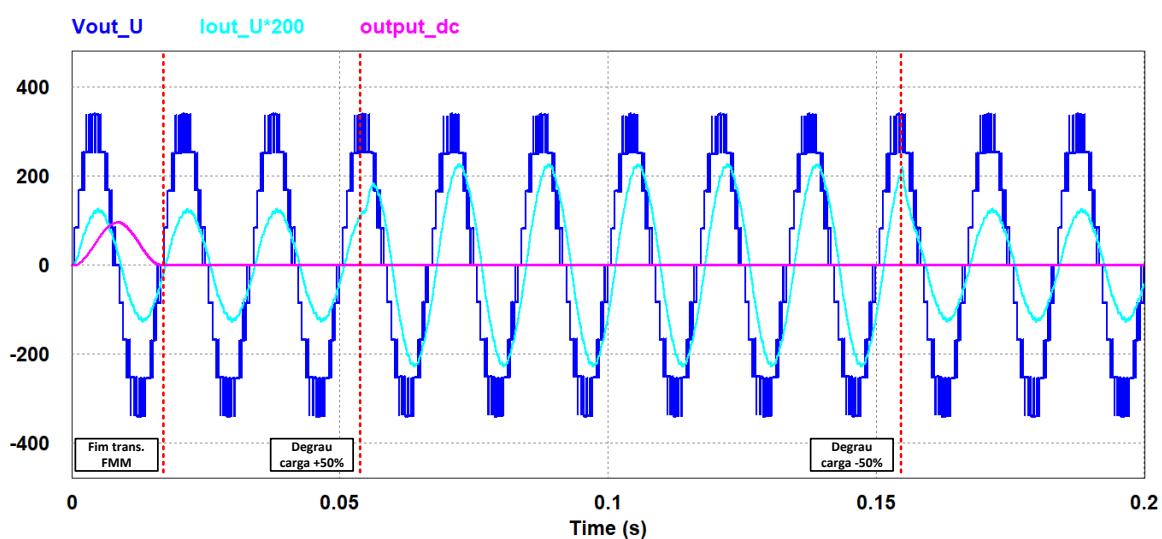

| Figura 55 – Formas de onda de tensão (Azul), corrente (Ciano) [x10] e nível c.c. (Rosa) de saída experimentais para degrau de carga de +50% e -50%. . . . .                                                                                                                                                                                      | 86  |

| Figura 56 – Identificação de falha no interruptor G10 com barramento reduzido para: <b>(a)</b> 0,9 p.u., <b>(b)</b> 0,8 p.u. e <b>(c)</b> 0,7 p.u. . . . .                                                                                                                                                                                       | 88  |

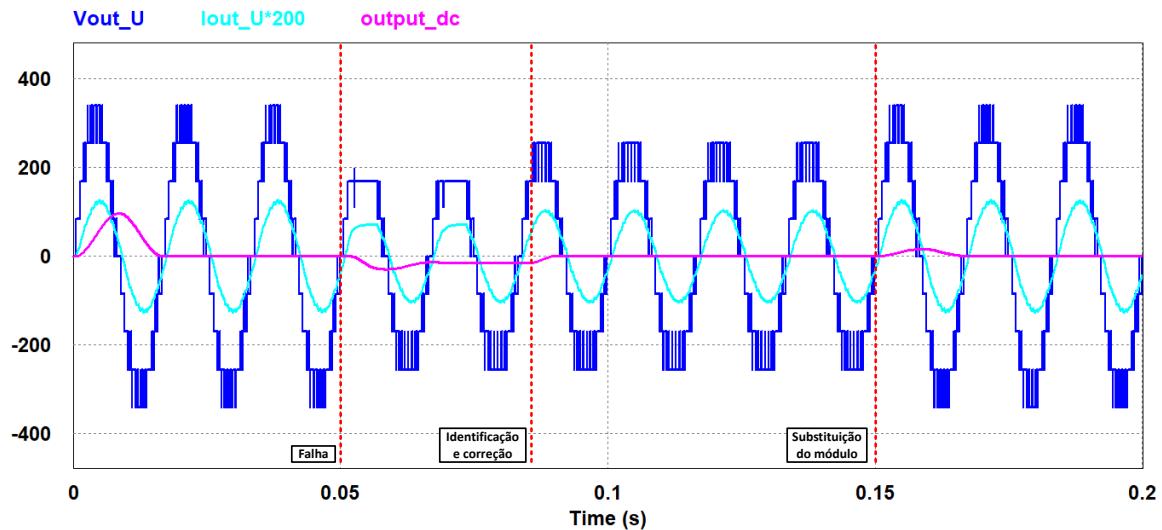

| Figura 57 – Formas de onda de tensão (Azul), corrente (Ciano) [x10] e nível c.c. (Rosa) de saída experimentais para reposição do módulo danificado. . . . .                                                                                                                                                                                      | 90  |

| Figura 58 – Esquemático do módulo de <i>bypass</i> confeccionado - <i>Gate-driver</i> e potência. .                                                                                                                                                                                                                                              | 105 |

| Figura 59 – Esquemático do módulo de <i>bypass</i> confeccionado - Condicionamento e regulação. . . . .                                                                                                                                                                                                                                          | 106 |

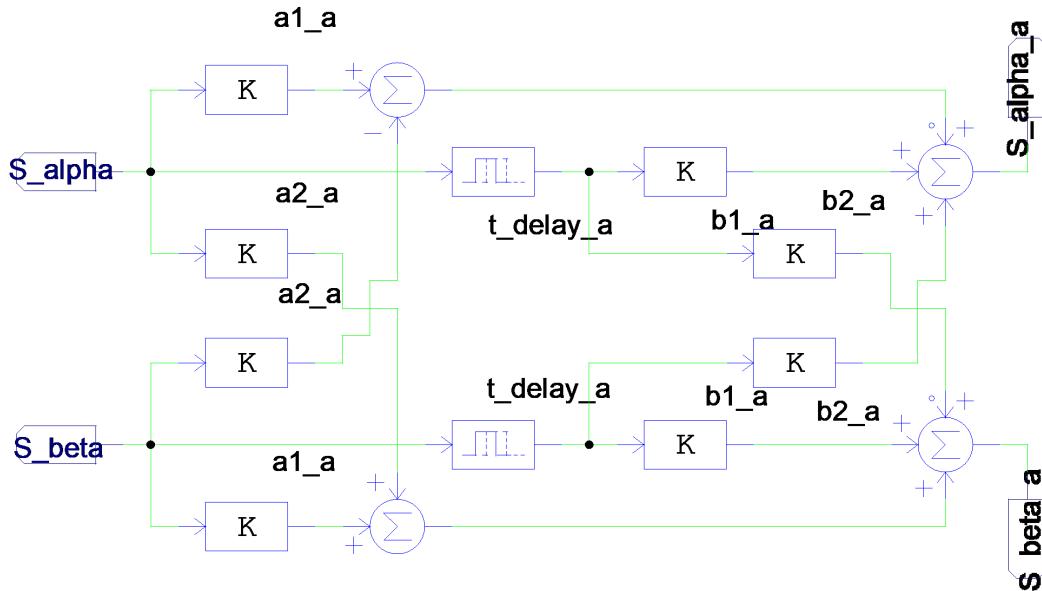

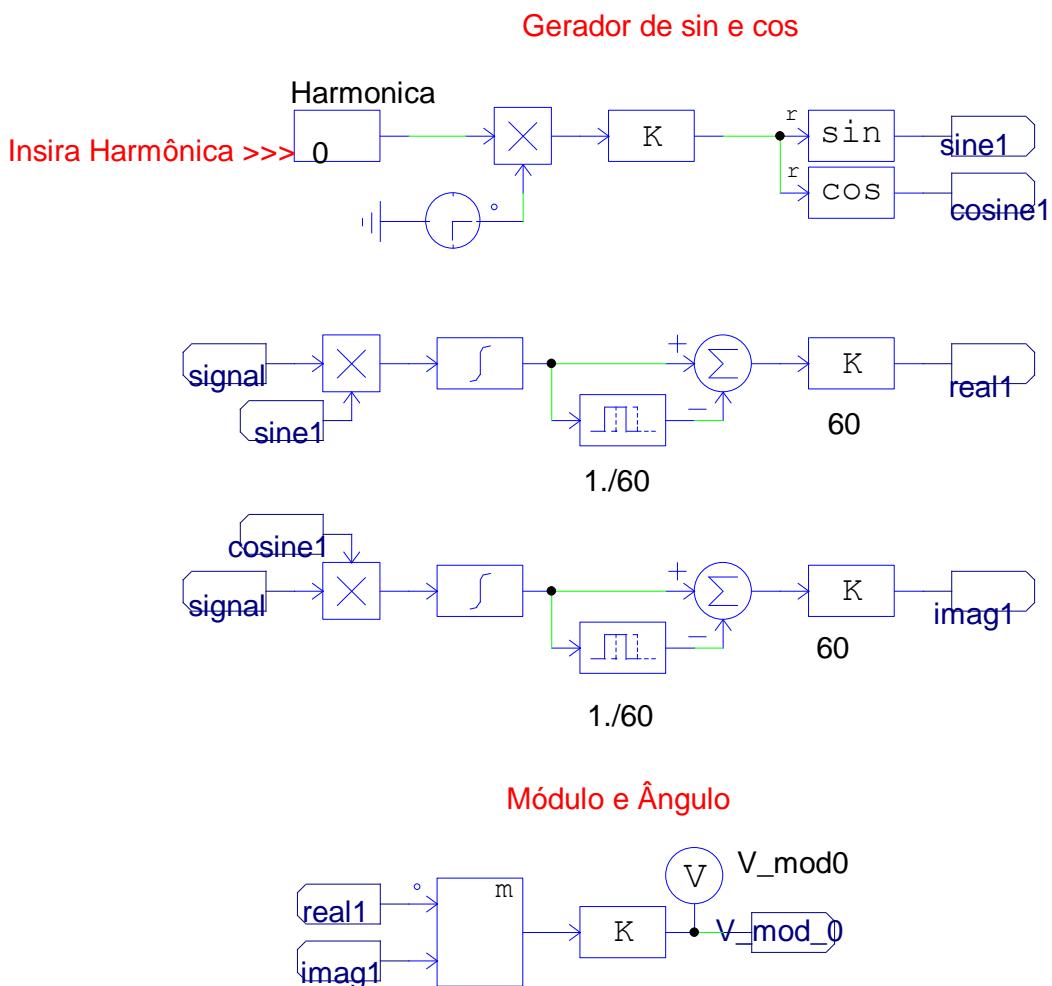

| Figura 60 – Implementação da operação GDSC em notação escalar para utilização em <i>software</i> de simulação. . . . .                                                                                                                                                                                                                           | 110 |

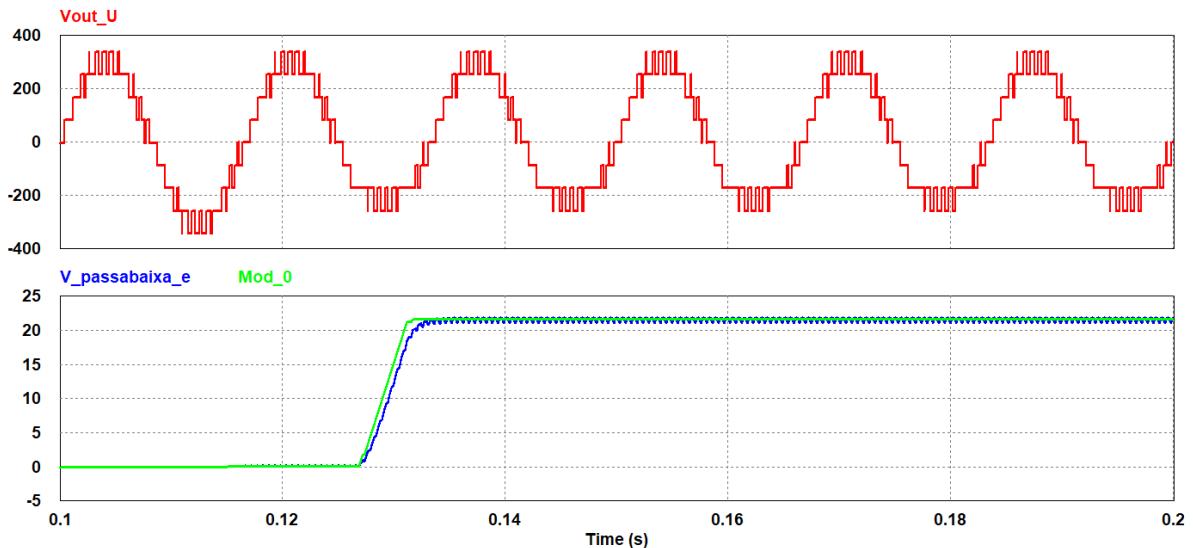

| Figura 61 – Formas de onda de tensão de saída (vermelho), nível médio da saída via GDSC (azul) e nível médio da saída via DFT (verde). . . . .                                                                                                                                                                                                   | 111 |

| Figura 62 – Implementação em diagrama de blocos da DFT. . . . .                                                                                                                                                                                                                                                                                  | 112 |

| Figura 63 – Formas de onda do nível médio da tensão de saída, calculados via FMM discreto (vermelho) e DFT analógica (azul). . . . .                                                                                                                                                                                                             | 113 |

| Figura 64 – Conversor MMC com 4 módulos por braço simulado. . . . .                                                                                                                                                                                                                                                                              | 114 |

|                                                                                                                                                                                                                                                               |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Figura 65 – Formas de onda de tensão (Azul) e corrente (Ciano) de saída via simulação para funcionamento normal do conversor MMC. . . . .                                                                                                                     | 115 |

| Figura 66 – Formas de onda de tensão (Azul), corrente (Ciano) e nível c.c. (Rosa) de saída via simulação, do conversor MMC, para identificação e correção de falha dos interruptores: <b>(a)</b> G13, <b>(b)</b> G15, <b>(c)</b> G9 e <b>(d)</b> G11. . . . . | 116 |

| Figura 67 – Formas de onda de tensão (Azul), corrente (Ciano) e nível c.c. (Rosa) de saída via simulação, do conversor MMC, para identificação e correção de falha dos interruptores: <b>(a)</b> G5, <b>(b)</b> G7, <b>(c)</b> G1 e <b>(d)</b> G3. . . . .    | 117 |

## LISTA DE TABELAS

|                                                                                                                                                                                                       |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| Tabela 1 – Parâmetros utilizados por Ghazanfari e Mohamed (2016) . . . . .                                                                                                                            | 35  |

| Tabela 2 – Parâmetros utilizados por Mukherjee, Zagrodnik e Wang (2016). . . . .                                                                                                                      | 38  |

| Tabela 3 – Comparação das estruturas de identificação de falha . . . . .                                                                                                                              | 42  |

| Tabela 4 – Parâmetros utilizados do conversor base utilizado para simulação e experimentação da técnica de identificação. . . . .                                                                     | 44  |

| Tabela 5 – Nível médio da tensão de saída pós-falha para falha individual de semicondutor utilizando modulação PS-PWM e identificação por cor do módulo correspondente ao interruptor. . . . .        | 46  |

| Tabela 6 – Nível médio da tensão de saída pós-falha para falha individual de semicondutor utilizando modulações PD-PWM e SHE e identificação por cor do módulo correspondente ao interruptor. . . . . | 50  |

| Tabela 7 – Padrão de cores utilizado para as formas de onda apresentadas. . . . .                                                                                                                     | 61  |

| Tabela 8 – Lista de componentes do módulo de <i>bypass</i> . . . . .                                                                                                                                  | 107 |

| Tabela 9 – Parâmetros calculados para as operações GDSC. . . . .                                                                                                                                      | 111 |

## LISTA DE ABREVIATURAS E SIGLAS

|           |                                                                      |

|-----------|----------------------------------------------------------------------|

| APOD-PWM  | <i>Alternate Phase Opposition Disposition Pulse-Width Modulation</i> |

| c.a.      | Corrente Alternada                                                   |

| c.c.      | Corrente Contínua                                                    |

| c.c.-c.c. | Corrente Contínua para Corrente Contínua                             |

| CHB       | <i>Cascaded H-Bridge</i>                                             |

| CI        | Circuito Integrado                                                   |

| CNN       | <i>Convolutional Neural Network</i>                                  |

| DFT       | <i>Discrete Fourier Transform</i>                                    |

| DSP       | <i>Digital Signal Processor</i>                                      |

| FC        | <i>Flying Capacitor</i>                                              |

| FMM       | Filtro Média Móvel                                                   |

| FP        | Fator de Potência                                                    |

| FPGA      | <i>Field-Programmable Gate Array</i>                                 |

| GDSC      | <i>Generalized Delayed Signal Cancellation</i>                       |

| HVDC      | <i>High Voltage Direct Current</i>                                   |

| IGBT      | <i>Insulated-Gate Bipolar transistor</i>                             |

| LED       | <i>Light-Emitting Diode</i>                                          |

| MMC       | <i>Modular Multilevel Converter</i>                                  |

| MOSFET    | <i>Metal Oxide Semiconductor Field Effect Transistor</i>             |

| NPC       | <i>Neutral Point Clamped</i>                                         |

| PD-PWM    | <i>Phase Disposition Pulse-Width Modulation</i>                      |

| POD-PWM   | <i>Phase Opposition Disposition Pulse-Width Modulation</i>           |

| PS-PWM    | <i>Phase-Shift Pulse-Width Modulation</i>                            |

| PWM       | <i>Pulse-Width Modulation</i>                                        |

| RL        | Resistivo-indutivo                                                   |

| SHE       | <i>Selective Harmonic Elimination</i>                                |

| SHM       | <i>Selective Harmonic Mitigation</i>                                 |

| SVM       | <i>Space Vector Modulation</i>                                       |

| THD       | <i>Total Harmonic Distortion</i>                                     |

| VCE       | <i>Voltage Collector-Emitter</i>                                     |

VSI

*Voltage Source Inverter*

## LISTA DE SÍMBOLOS

|           |                           |

|-----------|---------------------------|

| !         | Fatorial                  |

| $\pm$     | Mais ou menos             |

| %         | Percentual                |

| $f$       | Frequência                |

| $fs$      | Frequência de Comutação   |

| $I_{out}$ | Corrente de Saída         |

| $k$       | Posição em um Vetor       |

| $N$       | Número de Módulos         |

| $V_{bar}$ | Tensão do Barramento c.c. |

| $V_{out}$ | Tensão de Saída           |

| A         | Ampère                    |

| Hz        | Hertz                     |

| kHz       | Kilohertz                 |

| $L$       | Tamanho do Vetor          |

| ms        | Milisegundo               |

| $^\circ$  | Graus                     |

| p.u.      | Sistema por unidade       |

| s         | Segundo                   |

| V         | Volt                      |

| VA        | Volt-Ampère               |

| W         | Watts                     |

## SUMÁRIO

|          |                                                                    |           |

|----------|--------------------------------------------------------------------|-----------|

| <b>1</b> | <b>INTRODUÇÃO . . . . .</b>                                        | <b>17</b> |

| 1.1      | OBJETIVO GERAL . . . . .                                           | 26        |

| 1.2      | OBJETIVOS ESPECÍFICOS . . . . .                                    | 26        |

| 1.3      | DELIMITAÇÕES DO TRABALHO . . . . .                                 | 27        |

| 1.4      | ESTRUTURA DO TRABALHO . . . . .                                    | 27        |

| 1.5      | TRABALHO PUBLICADO . . . . .                                       | 28        |

| <b>2</b> | <b>REVISÃO BIBLIOGRÁFICA . . . . .</b>                             | <b>29</b> |

| 2.1      | OPERAÇÃO DO MÓDULO PONTE COMPLETA EM FALHA . . . . .               | 31        |

| 2.2      | ESTRATÉGIAS DE IDENTIFICAÇÃO DE FALHAS . . . . .                   | 34        |

| 2.2.1    | Variação da tensão no barramento c.c. . . . .                      | 34        |

| 2.2.2    | Leitura individual da tensão de saída dos módulos . . . . .        | 37        |

| 2.2.3    | Estratégia de modulação dedicada . . . . .                         | 40        |

| 2.2.4    | Outras Estratégias . . . . .                                       | 40        |

| 2.3      | CONSIDERAÇÕES E DISCUSSÕES . . . . .                               | 42        |

| <b>3</b> | <b>METODOLOGIA PROPOSTA PARA IDENTIFICAÇÃO DE FALHAS</b> . . . . . | <b>43</b> |

| 3.1      | DETERMINAÇÃO DO PADRÃO HARMÔNICO . . . . .                         | 43        |

| 3.1.1    | Conversor e parâmetros utilizados . . . . .                        | 43        |

| 3.1.2    | Análise harmônica das modulações . . . . .                         | 44        |

| 3.1.2.1  | <i>PS-PWM</i> . . . . .                                            | 45        |

| 3.1.2.2  | <i>PD-PWM e SHE</i> . . . . .                                      | 47        |

| 3.1.2.3  | <i>Considerações e discussões</i> . . . . .                        | 51        |

| 3.2      | FILTRO DIGITAL PARA O NÍVEL MÉDIO . . . . .                        | 52        |

| 3.3      | ESTRATÉGIA DE CORREÇÃO . . . . .                                   | 55        |

| 3.4      | IDENTIFICAÇÃO DO MÓDULO DANIFICADO . . . . .                       | 57        |

| <b>4</b> | <b>RESULTADOS DE SIMULAÇÃO E EXPERIMENTAIS . . . . .</b>           | <b>61</b> |

| 4.1      | APRESENTAÇÃO DO PROTÓTIPO . . . . .                                | 61        |

| 4.2      | FUNCIONAMENTO NORMAL . . . . .                                     | 68        |

| 4.3      | FALHA DOS INTERRUPTORES . . . . .                                  | 70        |

| 4.4      | IDENTIFICAÇÃO E CORREÇÃO DAS FALHAS . . . . .                      | 77        |

| 4.5      | RESULTADOS QUALITATIVOS - PRÉ E PÓS-FALHA . . . . .                | 84        |

| 4.6      | DEGRAU DE CARGA . . . . .                                          | 86        |

| 4.7      | FUNCIONAMENTO DO MÉTODO COM BARRAMENTO REDUZIDO . . . . .          | 87        |

| 4.8      | REPOSIÇÃO DO MÓDULO DANIFICADO . . . . .                           | 89        |

| 4.9      | CONSIDERAÇÕES E DISCUSSÕES . . . . .                               | 90        |

| <b>5</b> | <b>CONCLUSÕES . . . . .</b>                                        | <b>92</b> |

|     |                                                                 |            |

|-----|-----------------------------------------------------------------|------------|

| 5.1 | SUGESTÕES PARA DA TRABALHOS FUTUROS . . . . .                   | 94         |

|     | <b>REFERÊNCIAS . . . . .</b>                                    | <b>96</b>  |

|     | <b>APÊNDICE A – PROGRAMAÇÃO BLOCO C . . . . .</b>               | <b>100</b> |

|     | <b>APÊNDICE B – ESQUEMÁTICO MÓDULO DE BYPASS . . . . .</b>      | <b>105</b> |

|     | <b>APÊNDICE C – ESTRATÉGIA DE IDENTIFICAÇÃO GDSC . . . . .</b>  | <b>108</b> |

|     | <b>APÊNDICE D – ESTRATÉGIA DE IDENTIFICAÇÃO - MMC . . . . .</b> | <b>114</b> |

## 1 INTRODUÇÃO

As principais aplicações da energia elétrica iniciaram com a corrente contínua. Todas as descobertas básicas feitas por Volta, Ampère e Ohm no início do século XIX utilizavam corrente contínua (KIMBARK, 1971). As primeiras lâmpadas utilizavam uma tensão contínua de alta amplitude aplicada a dois terminais encapsulados dentro de uma câmara fechada completa com algum gás, que era ionizado e emitia luz. As lâmpadas incandescentes só foram surgir no fim do século XIX.

A primeira estação de transmissão elétrica criada contemplava o fornecimento de energia em 110 V de corrente contínua e foi criada por Thomas Edison em 1882 na cidade de Nova Iorque (LOBENSTEIN; SULZBERGER, 2008). Por se tratar de uma tecnologia extremamente moderna para a época, tal estratégia foi adotada em várias das grandes cidades ao redor do mundo.

No final do século XIX, deu-se início a corrida entre as duas principais estratégias de transmissão de energia elétrica: corrente alternada (c.a.) e corrente contínua (c.c.). Os principais nomes por trás desta corrida eram o de Thomas Edison e o de Nikola Tesla, juntamente a George Westinghouse (MCNICHOL, 2011). Edison, que já havia instituído como padrão a transmissão de energia elétrica baseada em corrente contínua nos Estados Unidos da América, era oposto a estratégia proposta por Tesla e Westinghouse. Esta abordagem se baseava na facilidade de geração, distribuição, transmissão e maior aplicabilidade da corrente alternada, vide a possibilidade de utilização de transformadores e motores elétricos de indução, além da implementação de sistemas polifásicos.

O motor elétrico de indução de gaiola foi patenteado em 1889, pelo engenheiro eletricista Michael von Dolivo Dobrowolsky, da firma AEG, de Berlim, utilizando-se do modelo proposto por Nikola Tesla (Figura 1). Este era simples, silencioso, tinha menos manutenção e alta segurança em operação (VAVILOV, 1945). A predominância da corrente alternada foi absoluta. O crescimento industrial da época adotou os motores elétricos a indução como base das maiores e melhores linhas produtivas. Desta forma, a geração de energia em corrente alternada se provou a estratégia mais eficaz, especialmente com o advento dos geradores baseados em turbinas à vapor.

Apesar da completa aceitação da superioridade da corrente alternada nos pontos de vista de transmissão e aplicação, as vantagens da corrente contínua não podem ser descartadas. Entre estas vantagens, a mais notória é a sua aplicação em sistemas criados no início do século XX e que iriam revolucionar as duas guerras mundiais que ainda estariam por vir: a eletrônica.

Criado em 1905 por John Ambrose Fleming, o diodo foi o primeiro componente eletrônico inventado. Sua utilização, na época, era exclusivamente para detecção de sinais telegráficos. A evolução natural deste sistema possibilitou também a emissão de sinais em larga escala, dando início às primeiras transmissões de voz via rádio.

Os avanços tecnológicos de meados do século XX, culminados por ambas as guerras, criaram, além das primeiras estações de rádio, que possibilitavam a transmissão de voz, as

Figura 1 – Primeiro motor de indução proposto por Tesla, em exibição no Museu Britânico de Ciência, em Londres.

Fonte: Retirado de Tesla (1887).

redes televisivas, quando se adotou a utilização das válvulas termiônicas, grandes componentes eletrônicos capazes de controlar a intensidade de corrente elétrica contínua.

As válvulas foram substituídas em 1947 pelo transistor, componente de mesma funcionalidade, porém de peso, volume e custo muito inferior. A criação do transistor propiciou um grande incentivo para a indústria eletrônica, que era, até então, limitada a utilização de equipamentos de grande volume. Através do transistor e seus derivados futuros (MOSFET, IGBT) diversos ramos da eletrônica foram abertos, dentre estes, a eletrônica de potência.

A eletrônica de potência é uma ciência aplicada que aborda a conversão e o controle de fluxo de energia elétrica entre dois ou mais sistemas distintos, através de conversores estáticos de potência (BARBI, 2012). Dentre os principais equipamentos possíveis após o advento da eletrônica de potência, é possível citar o inversor de frequência, a *soft-starter* e os conversores c.c. - c.c. (corrente contínua para corrente contínua) utilizados em fontes de alimentação diversas.

Atualmente, a área da eletrônica de potência pode ser citada como uma das mais limitantes da evolução tecnológica. Isto é, a mesma está diretamente atrelada a capacidade de aumento de processamento de dados de um computador, a diminuição de peso e volume de um aparelho celular, mantendo as mesmas propriedades de processamento e carga, ou até mesmo a autonomia de um veículo elétrico.

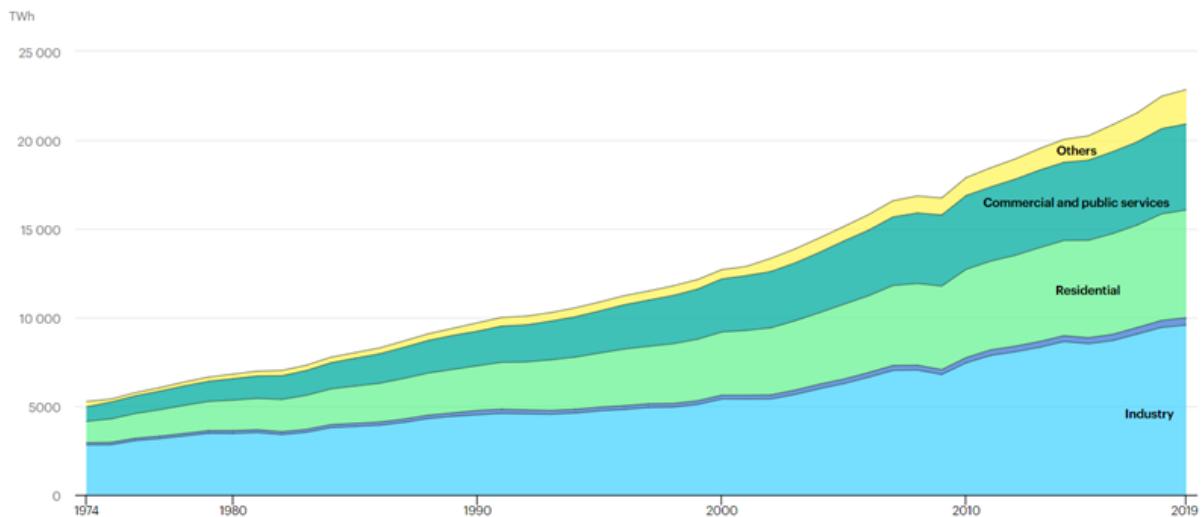

Entre as principais áreas de estudo da eletrônica de potência, a transmissão de energia elétrica pode ser citada, tendo em vista que o consumo industrial e doméstico mais que que duplicou do início do século XX até meados do mesmo século e atingiu valores dez vezes maiores na entrada do século XXI. A necessidade de aumento na eficiência da geração e transmissão de energia elétrica passou a ser uma prioridade. A interligação dos sistemas elétricos nacionais e a adoção de gerações alternativas de energia passou de luxo para uma necessidade em diversos países que viam sua demanda energética aumentando cada vez mais. O grande aumento do consumo industrial e doméstico, a partir de 1974, (IEA, 2021) é demonstrado na Figura 2.

Figura 2 – Consumo energético mundial de 1974 - 2019.

Fonte: Retirado de IEA (2021).

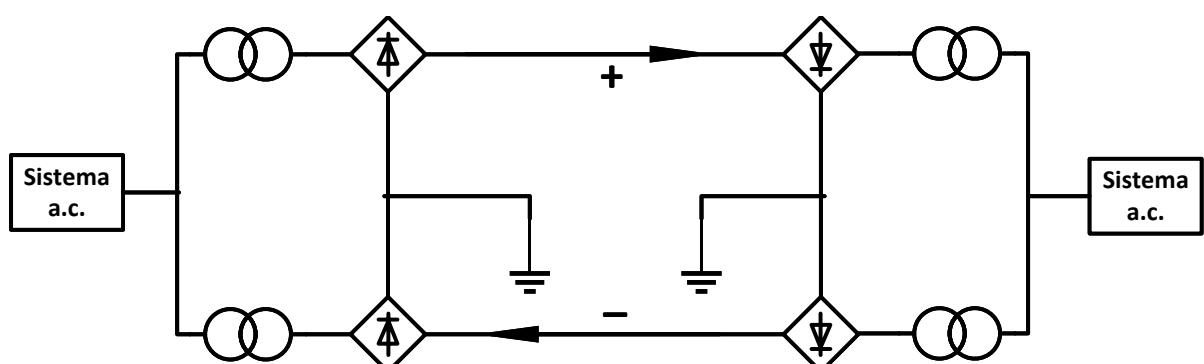

Uma das técnicas de transmissão de maior interesse para eletrônica de potência é a de Transmissão de Corrente Contínua em Alta Tensão (*High-Voltage Direct Current - HVDC*).

Esta técnica se baseia na introdução de barramentos em corrente contínua como meio principal de transmissão de energia a longas distâncias. Sistemas HVDC são compostos de basicamente quatro partes principais (ANDRADE; LEÃO, 2012):

- Transformadores: responsáveis pela adaptação da tensão alternada para níveis de trabalho aceitáveis dos conversores. Possibilita também a divisão entre os sistemas, através da isolação galvânica intrínseca do componente.

- Conversores: conexão direta entre a parte alternada e contínua do sistema. São formados por topologias difundidas na área de eletrônica de potência capazes de processar energia de sistemas alternados polifásicos para um sistema contínuo único ou vice-versa. Sistemas em HVDC se utilizam, normalmente, de dois tipos de conversão básica: a retificação, na qual há a conversão para corrente contínua, e a inversão, na qual há a transformação de volta para corrente alternada. Caso haja distribuição de energia diretamente em corrente contínua, não há necessidade da inversão.

- Condutores: a parte específica de transmissão do sistema é feita por estes componentes. Podem ser classificados pela quantidade de cabeamentos energizados utilizados: monopolares (com um condutor carregado apenas, geralmente de polaridade negativa), bipolar (com dois condutores carregados, positivo e negativo) ou homopolar (com dois ou mais condutores carregados de mesma polaridade, geralmente negativa).

- Controle e proteção: possíveis pelo alto nível eletrônico do sistema. O conhecimento em tempo real das diversas variáveis do sistema, tensão, corrente, frequência e potência (tanto

ativa quanto reativa), facilitam as estratégias de adaptação e contenção de problemas desta estratégia.

A Figura 3 apresenta um esquema básico de um sistema HVDC. Os sistemas de transmissão HVDC apresentam diversas vantagens em comparação aos sistemas em corrente alternada (WANG; REDFERN, 2010):

- Maior capacidade de transmissão por condutor carregado, e, portanto, menor custo de implementação das linhas em comparação a sistemas de mesmo processamento de potência em corrente alternada.

- Diminuição do efeito pelicular (*skin*) e das perdas de transmissão, visto a ausência das perdas geradas por aspectos relacionados à frequência.

- Eliminação dos problemas de regulação de tensão, que são gerados pela circulação de potência reativa.

- Facilidade de integração de geradores de energia independentes, pela possibilidade de acoplamento direto ao barramento contínuo, no qual a frequência e amplitudes da tensão são ajustados.

- Possibilidade de integração de dois sistemas em corrente alternada com diferentes características (amplitude e frequência).

Apesar de todos os benefícios apresentados, os sistemas de transmissão HVDC apresentam contrapontos que devem ser levados em conta antes de sua implementação. Entre estas desvantagens, é possível citar:

- Custo de implementação elevado da parte eletrônica.

Figura 3 – Esquema simplificado de um sistema HVDC.

Fonte: Adaptado de Wang e Redfern (2010).

Figura 4 – Sistema HVDC da empresa ABB.

Fonte: Retirado de Callavik (2017).

- Introdução de harmônicos gerados pela comutação dos dispositivos eletrônicos do conversor.

- Menor confiabilidade, se comparados a sistemas de transmissão em corrente alternada tradicionais.

- Dificuldade de proteção em caso de falta na linha, gerada pela alta inércia da corrente c.c. que dificulta a abertura do circuito.

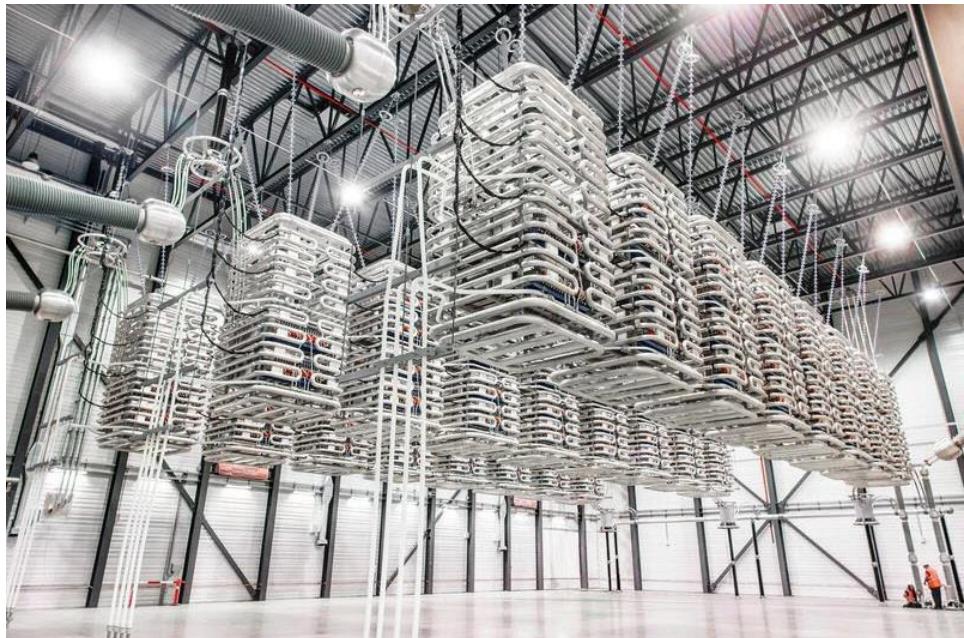

Os avanços tecnológicos, tanto do ponto de vista de produção dos componentes eletrônicos, quanto do ponto de vista científico de melhoria das topologias e estratégias de controle, mitigam cada vez mais os efeitos dos dois primeiros itens citados como desvantagens para a utilização de sistemas HVDC. O foco deste trabalho, contudo, está intrinsecamente relacionado ao terceiro item apontado como desvantagem deste sistema: confiabilidade.

Mesmo se tratando de um sistema com alto nível de controle, pela natureza eletrônica do mesmo, os sistemas de transmissão HVDC possuem maior possibilidade de falha, quando comparados aos sistemas em corrente alternada, que se utilizam, quase que exclusivamente, de componentes passivos com alta robustez.

Outra aplicação similar à HVDC, na qual o conversor deve, idealmente, apresentar funcionamento ininterrupto é no acionamento e controle de velocidade de motores de alta tensão. Estes motores quando utilizados em aplicações do setor petroquímico, naval, alimentícios e de geração de energia, especialmente, possuem característica de serviço essencial. A parada destes motores pode representar uma situação perigosa para atividade, como sobreaquecimento,

perda do produto não finalizado ou danificação completa do equipamento por impossibilidade de reacionamento, vide a alta inércia destes motores para partida com carga (WEG, 2021).

Por se tratarem de equipamentos de uso essencial, os conversores destes sistemas devem apresentar estratégias de controle para mitigação/eliminação dos efeitos de uma falha. As falhas de semicondutores se mostram como as mais danosas para o funcionamento pleno do equipamento. Isto se dá pela sua natureza topológica (HE; YANG; WANG, 2020).

Topologias utilizadas nestas aplicações devem suportar alto processamento de potência e grandes níveis de tensão e corrente. Pela limitação tecnológica das tensões de bloqueio dos semicondutores, os conversores utilizados para esta aplicação são quase que exclusivamente os ditos como conversores modulares (GUO et al., 2014).

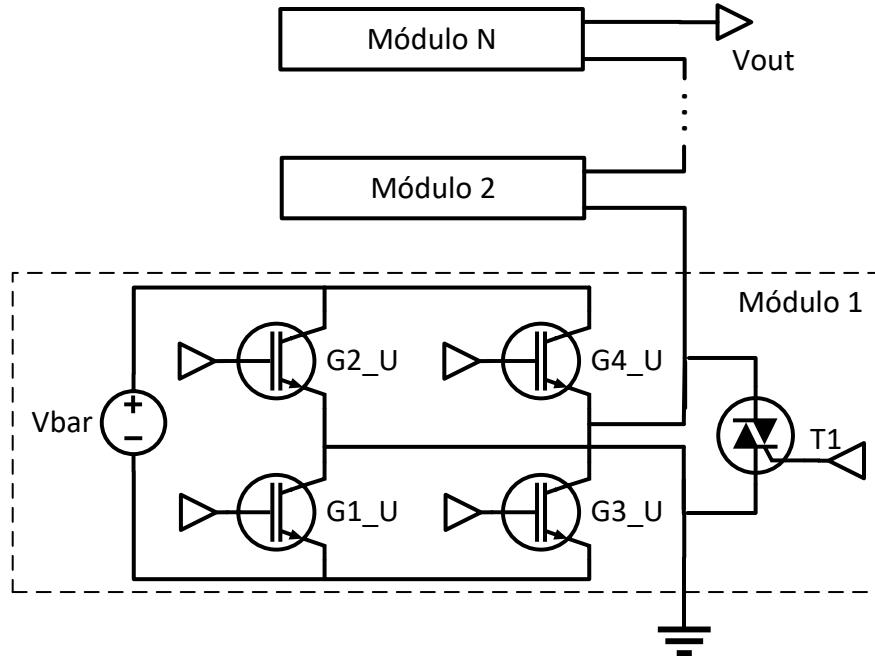

Os conversores modulares são aqueles formados pelo agrupamento de múltiplos conversores menores, já amplamente difundidos na literatura. Estes conversores pertencem ao grupo de conversores multiníveis, que possuem como maior característica a tensão de saída em configuração quase-quadrada (*staircase*) (BATSCHAUER, 2015), daí sua nomenclatura. A presença de múltiplos níveis de tensão de saída proporciona para a carga uma menor distorção harmônica total (*Total Harmonic Distortion - THD*) e menores derivadas de tensão.

Os conversores, pertencentes a esta categoria, mais utilizados são: Cascata de Pontes-Completa (*Cascaded H-Bridge - CHB*) e o Conversor Modular Multinível (*Modular Multilevel Converter – MMC*). A topologia básica destes conversores é apresentada na Figura 5 e na Figura 6, respectivamente. Entre os conversores multiníveis amplamente empregados na indústria e difundidos na literatura, mas que não se enquadram na característica modular, pode-se citar ainda o Conversor com Díodo de Grampeamento (*Neutral Point Clamped – NPC*) e o Conversor com Capacitores de Grampeamento (*Flying Capacitor – FC*), estes utilizados, majoritariamente, em aplicações de média tensão diversas (WEG, 2021).

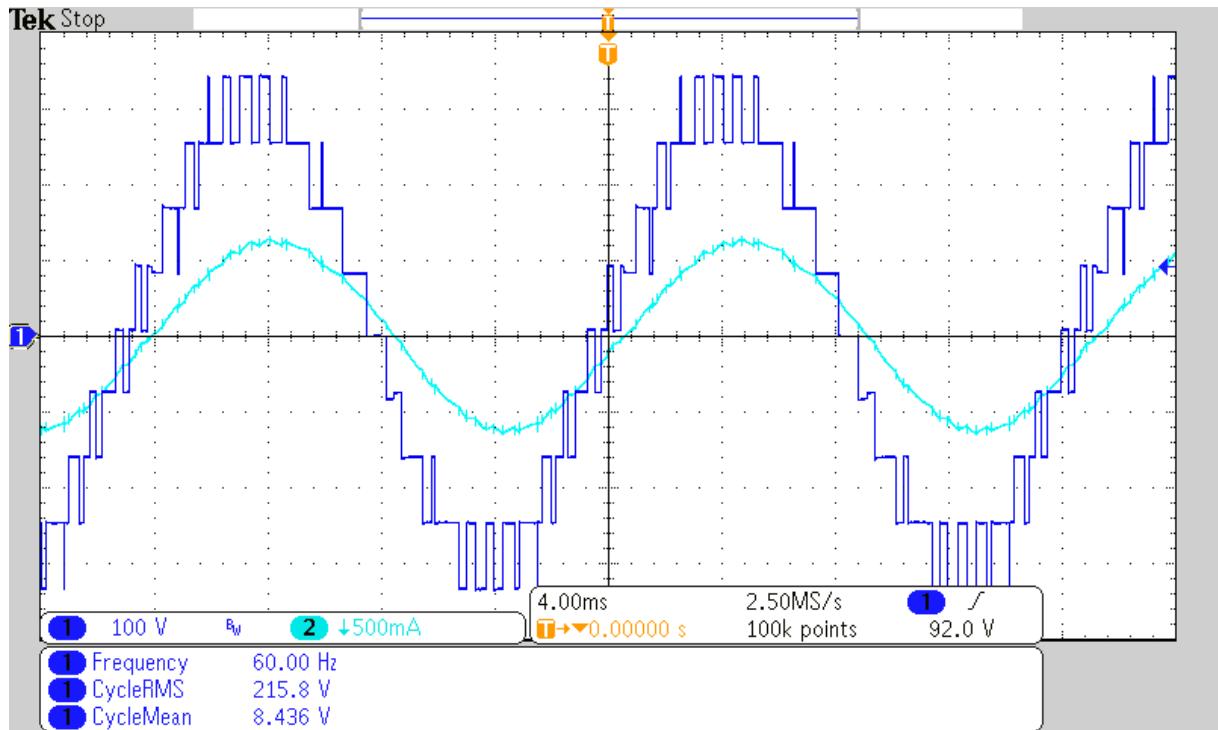

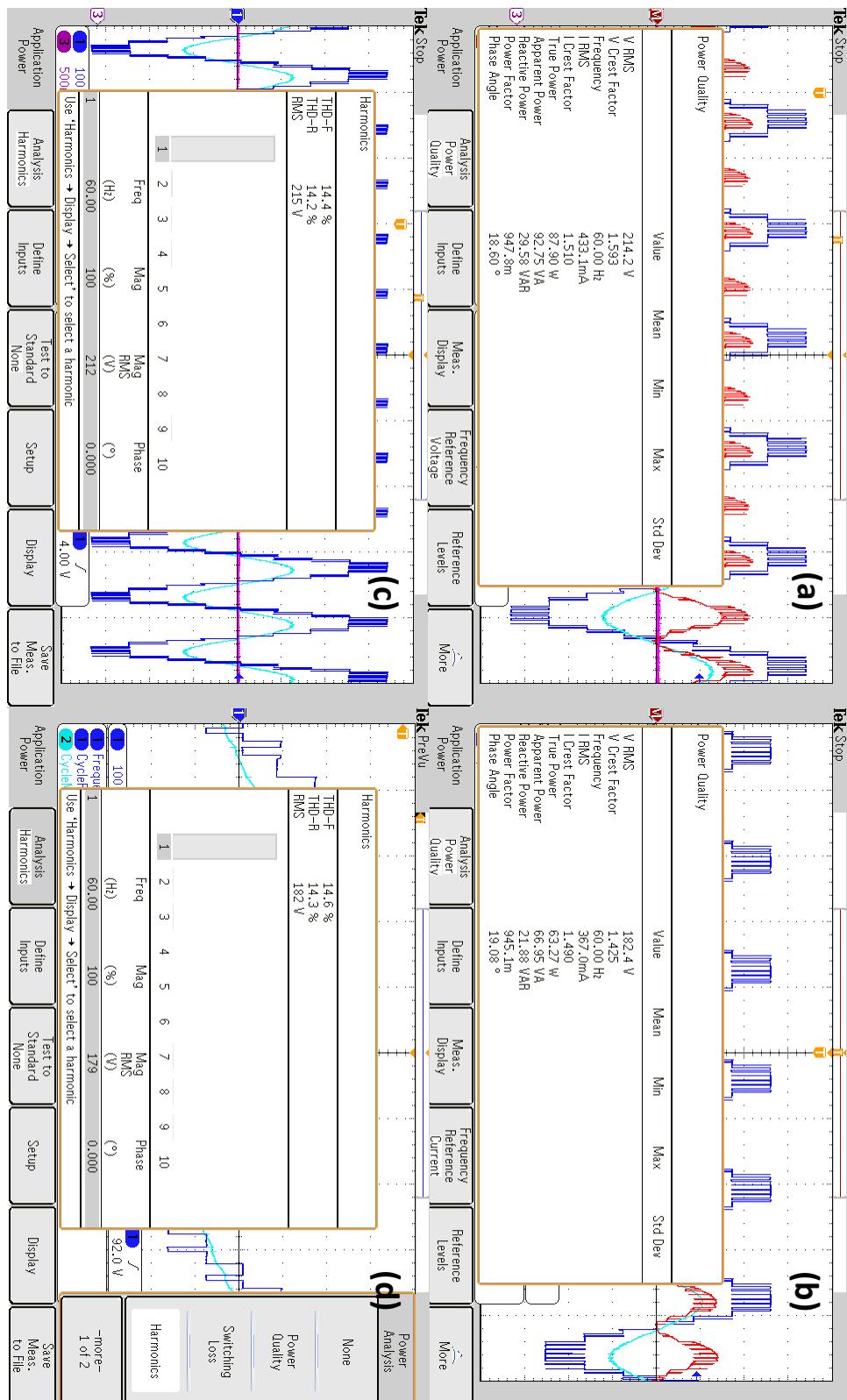

A produção e manutenção destes conversores é, dentro de suas proporções, simplificada, já que o equipamento utiliza múltiplos conversores idênticos associados numa configuração cascata (série). Isto gera, entretanto, uma característica funcional intrínseca. O mal funcionamento de um semicondutor e/ou um módulo não necessariamente impede o funcionamento completo do conversor, mas remove um dos níveis de tensão de saída. Esta situação é exemplificada na Figura 7.

Nesta situação é apresentado um resultado experimental de um conversor CHB monofásico com 4 módulos, operando com tensão de barramento de 85 V e modulação PD-PWM. É aplicada uma falha em um dos interruptores do módulo 3, responsável pelo processamento de um dos níveis de tensão negativa. Com isso, é possível notar que um dos níveis do semiciclo negativo da tensão de saída está faltando. Por esta razão, o nível médio da tensão de saída, que idealmente deve ser nulo, apresenta valor médio próximo de 31 V. Em adicional, a Figura 8 mostra a análise harmônica da forma de onda de tensão previamente apresentada, na qual é possível ver a inserção de harmônicos pares neste sinal. Para maior parte das aplicações em corrente alternada, tanto a inserção de harmônicos pares quanto a presença de um nível médio no

Figura 5 – Braço de topologia CHB com  $n$  células por fase e chave de bypass individual.

Fonte: Próprio autor, 2023.

signal são extremamente danosas, vide os reflexos de trepidação para cargas rotativas (motores) ou, especialmente, o de saturação de transformadores e indutores não preparados para estas condições, quando expostos ao nível médio.

Para um número elevado de níveis de tensão de saída, os reflexos da ausência de apenas um nível podem ser supridos pela ação de controle do conversor. Esta situação, entretanto, passa a ser crítica quando estes efeitos ultrapassam os limites de controle e, ainda mais, quando estes infringem as normativas de THD impostas pela legislação vigente.

Sendo o funcionamento destes equipamentos praticamente ininterrupto, a substituição dos módulos danificados exige um agendamento de parada do mesmo. Uma das estratégias mais comuns adotadas pela indústria para prolongamento e minimização destas situações é a utilização de módulos redundantes em paralelo (GHAZANFARI; MOHAMED, 2016), o que praticamente duplica o custo de produção do conversor.

Uma outra solução para esta situação é a utilização de um *bypass* temporário do módulo danificado, com adequação do índice de modulação. Esse *bypass* pode ser feito utilizando-se de chaves estáticas e/ou mecânicas em paralelo à saída de cada módulo, o que diminui consideravelmente o custo do equipamento, se comparado a utilização da redundância de módulos (MAHARJAN et al., 2021).

A maior dificuldade, em ambas as situações, entretanto, é a de identificação do módulo danificado. A queima dos interruptores em curto-circuito é de fácil identificação, já que os *gate-drivers* utilizados nestes componentes possuem um sistema integrado de identificação de saturação. Esta característica é necessária pois um curto-circuito destes componentes pode, muitas vezes, ser destrutivo ao conversor, pela possibilidade de curto do banco de capacitores

Figura 6 – Braço de topologia MMC com  $n$  células por fase e chave de *bypass* individual.

Fonte: Próprio autor, 2023.

acoplados aos mesmos.

Quando o interruptor é danificado em condição de circuito aberto, entretanto, esta identificação exige uma análise externa mais detalhada. Um interruptor do tipo IGBT (mais utilizado para aplicações deste porte) possui em antiparalelo um diodo, que entra em funcionamento em etapas de operação em que a corrente possui sentido inverso a polaridade da tensão. Diferente do MOSFET, este diodo não é intrínseco as junções, mas sim instalado externamente, conforme mostra a Figura 9.

Na queima em circuito aberto do IGBT, este diodo, na grande maioria dos casos, não é danificado, o que possibilita a continuidade da circulação da corrente pelo módulo. Esta situação é a responsável pela criação de formas de onda de tensão de saída como a apresentada na Figura 7, na qual o conversor continua operando com um dos níveis de tensão faltantes.

Figura 7 – Formas de onda de tensão (Azul) [100 V/div] e corrente (Ciano) [500 mA V/div] de saída de um conversor CHB com falha de um semicondutor do semibraço inferior.

Fonte: Próprio autor, 2023.

Figura 8 – Análise harmônica das formas de onda de tensão e corrente de saída de um conversor CHB com falha em um dos módulos.

Fonte: Próprio autor, 2023.

Figura 9 – Modelo 3D com visualização interna de um IGBT.

Fonte: Retirado de Popova et al. (2013).

## 1.1 OBJETIVO GERAL

Este trabalho propõe uma técnica de identificação de falhas que possa ser utilizada em ambos os conversores modulares previamente citados, o CHB e o MMC, utilizando-se de uma estratégia de modulação genérica, dentre as mais utilizadas e já difundidas na literatura, para tais conversores. Propõe-se também a utilização de sensoriamentos já comumente usados nestas topologias para aplicação das estratégias de controle básicas, tensão e corrente de saída, não sendo necessários sensoriamentos adicionais.

## 1.2 OBJETIVOS ESPECÍFICOS

- Determinar os padrões de falhas visíveis na forma de onda de tensão de saída dos conversores modulares, a fim de verificar padrões ou discrepâncias mensuráveis que possam ser utilizados para identificação de uma falha.

- Criação de uma metodologia de medição e filtragem dos sinais de tensão e/ou corrente de saída que possibilitem a extração da informação necessária para determinação da condição de falha e sua origem.

- Implementação de uma estratégia de mitigação da falha com adequação do funcionamento do conversor para completa eliminação desta.

- Verificação da metodologia via simulação e experimentação completa da estratégia.

### 1.3 DELIMITAÇÕES DO TRABALHO

As delimitações do tema de pesquisa desta dissertação são apresentadas abaixo:

- Não é proposta uma nova estratégia de adequação completa da forma de onda de tensão de saída pós-falha, já que a estratégia de eliminação da falha utilizada conta apenas com o *bypass* do módulo danificado. O índice de modulação da estrutura se torna limitado a quantidade de módulos ainda ativos após o evento.

- O conversor utilizado neste trabalho opera em condição de malha aberta, já que uma estratégia de controle rodando em paralelo ao funcionamento da estrutura de identificação de falhas, adicionaria complexidade ao sistema como um todo, sendo necessárias possíveis adequações aos tempo de atuação dos controladores para que não haja interferência destes na leitura dos valores de tensão pós-falha.

- Apesar da operação em malha aberta, considera-se que o sensoriamento utilizado para a estratégia de identificação proposta (tensão de saída), é comumente visto em aplicações de malha fechada, por isso propõe-se este sensoriamento como essencial para o funcionamento do conversor em aplicações finais.

- Optou-se pela utilização de apenas uma estratégia de modulação para comprovação da eficácia do método proposto.

- Por indisponibilidade de módulos ponte completa com acionamento isolado dos quatro interruptores, optou-se pelo teste de falhas apenas dos interruptores superiores dos módulos, já que a falha dos interruptores da parte inferior causaria problemas de modulação gerados pela falta de carga dos capacitores dos circuitos de *bootstrap*, utilizados nos *gate-driver* dos semicondutores do conversor.

### 1.4 ESTRUTURA DO TRABALHO

No capítulo 1, foi apresentada a introdução do trabalho, expondo a relevância do tema proposto, com determinação do objetivo principal e específicos e as delimitações do projeto.

No capítulo 2, é apresentada uma revisão bibliográfica em torno dos métodos já explorados na literatura para identificação de falhas de circuito aberto em conversores modulares. São analisados os principais fundamentos e distinções destas técnicas e feita uma breve análise comparativa.

No capítulo 3, é explicada a metodologia de identificação de falhas proposta, feita por meio de uma análise harmônica da tensão de saída de um conversor CHB, afim de encontrar padrões ou distinções que possam apontar para o módulo danificado. Determinado o sinal de interesse, é também proposta a utilização de um filtro média móvel, capaz de fazer a leitura e condicionamento deste sinal a ser utilizado no método.

No capítulo 4, são apresentados os resultados experimentais e de simulação obtidos, com uma breve apresentação do protótipo e circuito utilizados para tal. São analisadas e comprovadas as condições teóricas propostas, com resultados adicionais para outras situações de funcionamento, como limitação dos barramentos c.c. do conversor, degraus de carga e reposição do módulo danificado.

Por fim, no capítulo 5, são apresentadas as conclusões e os resultados alcançados pelo método de identificação proposto, seguidos por algumas sugestões de trabalhos futuros dentro da linha de pesquisa abordada.

## 1.5 TRABALHO PUBLICADO

O trabalho efetuado durante o curso de mestrado resultou em um artigo técnico-científico, publicado no XXIV Congresso Brasileiro de Automática (CBA). O tema do mesmo é abordado no Apêndice C. A referência do artigo é:

- SOUZA, H. F.; BATSCHAUER, A. L. ; ZIMANN, F. J. . Identificação de Falhas de Semicondutores em Circuito-aberto para Conversores Modulares Utilizando a Operação de Cancelamento por Sinal Atrasado Generalizado. In: XXIV Congresso Brasileiro de Automática, 2022, Fortaleza. XXIV Congresso Brasileiro de Automática, 2022.

## 2 REVISÃO BIBLIOGRÁFICA

Este capítulo apresenta uma análise criteriosa da estrutura de falha de um módulo ponte completa, afim de determinar os padrões de falha de circuito aberto. Em seguida, são revisadas as principais estratégias de identificação de falhas em conversores modulares encontrados na literatura. Para tal, são abordadas as vantagens e desvantagens de cada método, topologias e modulações utilizadas e suas limitações para utilização na aplicação proposta.

A literatura apresenta diversas estratégias distintas quanto a identificação de falhas em conversores modulares e/ou multiníveis (LU; SHARMA, 2009). Um dos principais fatores em comum vistos na maioria das referências é a preferência da indústria pela utilização de duas topologias específicas: o CHB e o MMC. Ambos conversores apresentam pontos positivos e negativos, mas sua facilidade de produção seriada é extremamente atrativa para o mercado, se comparados a outras topologias multiníveis, o que explica seu favoritismo.

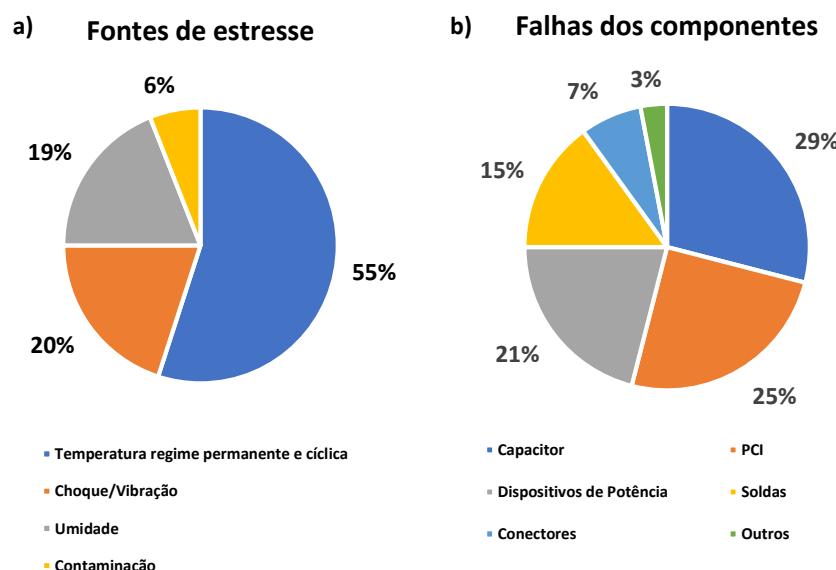

Diversas falhas podem ocorrer em conversores de potência, desencadeadas por um conjunto de fatores. A Figura 10 apresenta um levantamento das taxas de falha de componentes críticos de conversores de potência, com a distribuição das fontes de estresse associadas a estas falhas (RAHIMPOUR et al., 2022), (WANG; LISERRE; BLAABJERG, 2013) (YANG et al., 2011).

Os capacitores apresentam a maior taxa de falhas dentre os componentes analisados, aproximadamente 30 % dos casos. A confiabilidade destes componentes pode ser aumentada pela seleção adequada da tecnologia do capacitor e do monitoramento de parâmetros durante a operação (WANG; BLAABJERG, 2014).

Figura 10 – Levantamentos das taxas de falhas em conversores: (a) Distribuição das fontes de estresses; (b) Distribuição de falhas entre os principais componentes.

Fonte: Próprio autor, 2023.

A Placa de Circuito Impresso (PCI) é o segundo item mais sujeito a falhas, com 26 % de chance. As falhas nas PCIs podem ser divididas em dois grupos: as falhas acumuladas por fadiga; ou falhas repentinas. Estas falhas podem ser causadas por choques mecânicos ou a longo prazo devido a vibração, contaminação, degradação e outros fatores de estresse. Muitos destes defeitos podem ser evitados através do conhecimento prévio da aplicação (vibração, contaminantes etc.) e aplicadas no projeto, afim de adequar o mesmo para estas condições de estresse durante a produção, armazenamento, transporte e utilização final.

Os semicondutores de potência são mais propensos a falhas devido à sua frequente comutação e a influência que sofrem dos esforços térmicos e elétricos. A Figura 10 **(a)** indica a temperatura como o fator de estresse dominante, com 55 % da distribuição total contribuinte para as falhas dos semicondutores. O item **(b)** mostra que dispositivos de potência como IGBTs e MOSFETS, muitas vezes em módulos, respondem por cerca de 21 % das falhas dos conversores. Diversas medidas podem ser tomadas para minimizar a chance de falhas destes componentes, ainda assim, uma estratégia de identificação/correção das falhas destes conversores é necessária, já que uma falha desses componentes é capaz de levar a uma falha catastrófica de todo sistema.

As falhas dos semicondutores são divididas, simplificadamente, em dois tipos: falhas de curto-círcuito e falhas de circuito aberto. As falhas de curto-círcuito possuem certa facilidade de identificação (LU; SHARMA, 2009). Como os módulos utilizados em ambos conversores previamente mencionados se tratam de células em ponte completa, sabe-se que a comutação dos interruptores do mesmo braço possui comando complementar. Esta ação é necessária para impedir o curto franco dos capacitores do barramento, fator altamente destrutivo para os interruptores, assim como para o próprio capacitor. Para impedir esta situação, a indústria de *gate-drivers* adota a medição da tensão coletor-emissor (VCE), para interruptores do tipo IGBT, ou dreno-fonte, para interruptores do tipo MOSFET (SUPPLIER, S.I.). Esta medição possibilita uma limitação da queda de tensão máxima sobre o semicondutor, causada por uma grande circulação de corrente, característica de um curto-círcuito. A partir desta medição, é possível desabilitar o comando do interruptor em questão e enviar um sinal para o controlador/modulador, afim de adequar o conversor para as novas condições de trabalho.

Com metade dos problemas já resolvidos, a literatura se voltou para a segunda condição de falha de interruptores: a falha em circuito-aberto. Nesta situação de falha, o interruptor não é capaz de circular corrente no sentido coletor-emissor. Para a situação inversa de circulação de corrente, entretanto, dois cenários podem ocorrer. Naturalmente este sentido de circulação de corrente se utiliza do diodo em antiparalelo do próprio semicondutor. Nos casos em que este diodo também é danificado pela falha do IGBT, há uma completa perda da circulação da corrente pelo braço. Isto reflete em uma falha grave, que exige uma parada completa do conversor e uma análise dos danos gerados, com possível substituição de múltiplos componentes/módulos.

Quando a corrente mantém sua característica de circulação no sentido emissor-coletor, através do diodo em antiparalelo, contudo, uma situação incomum aparece: o conversor continua operando com dois níveis da tensão de saída faltantes. Esta situação possibilita que as topologias

consigam manter a carga ativa sob falha, já que não há um completo impedimento de circulação de corrente pelo módulo, apenas parcial. Este último cenário apresentado é o principal cenário de interesse para a literatura e também para este trabalho. Sendo assim, todas as abordagens futuras apresentadas relacionadas as falhas de circuito-aberto considerarão esta como a condição de falha do semicondutor.

## 2.1 OPERAÇÃO DO MÓDULO PONTE COMPLETA EM FALHA

Para compreender melhor as estratégias adotadas pela literatura, é preciso revisar as etapas de funcionamento de uma topologia ponte completa, utilizada em ambos conversores previamente mencionados, verificando as etapas eliminadas ou adicionadas quando um dos interruptores é danificado.

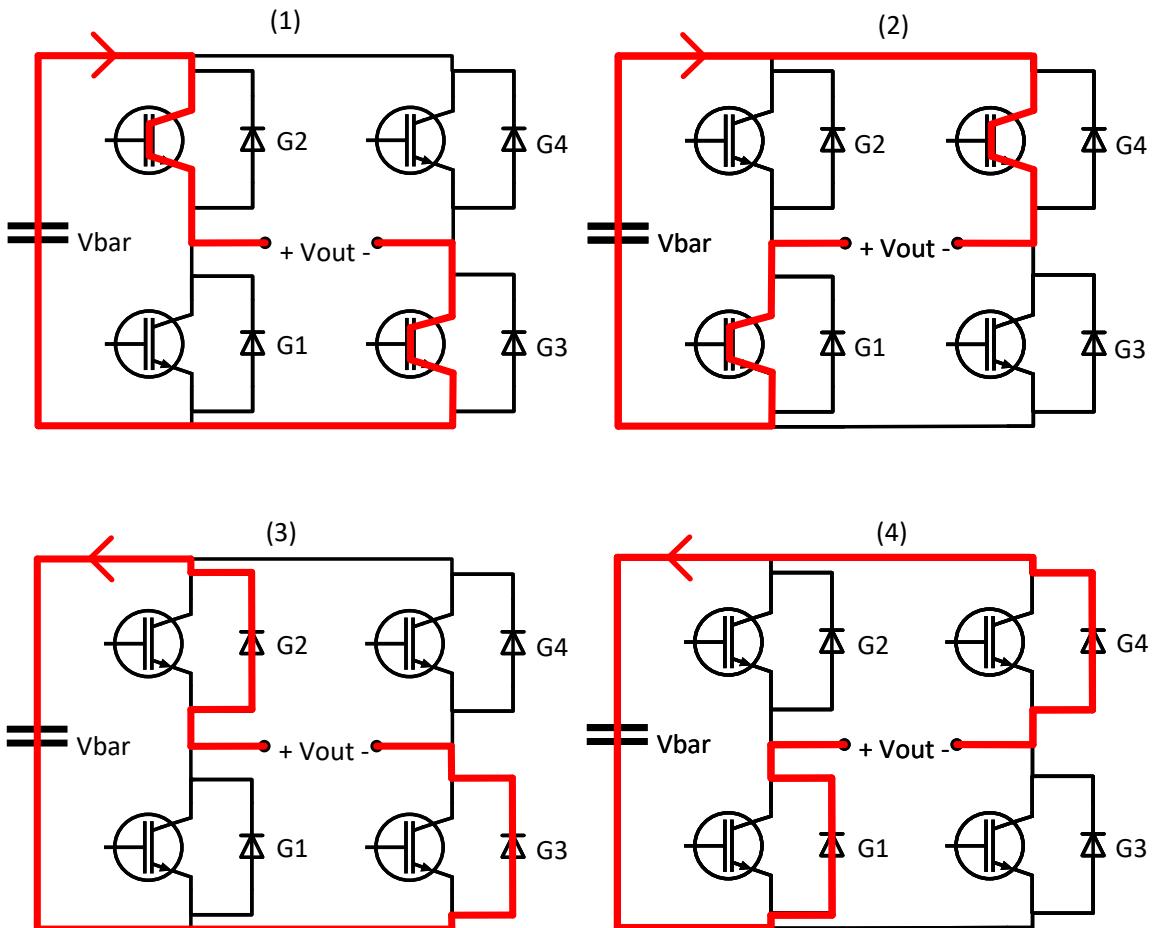

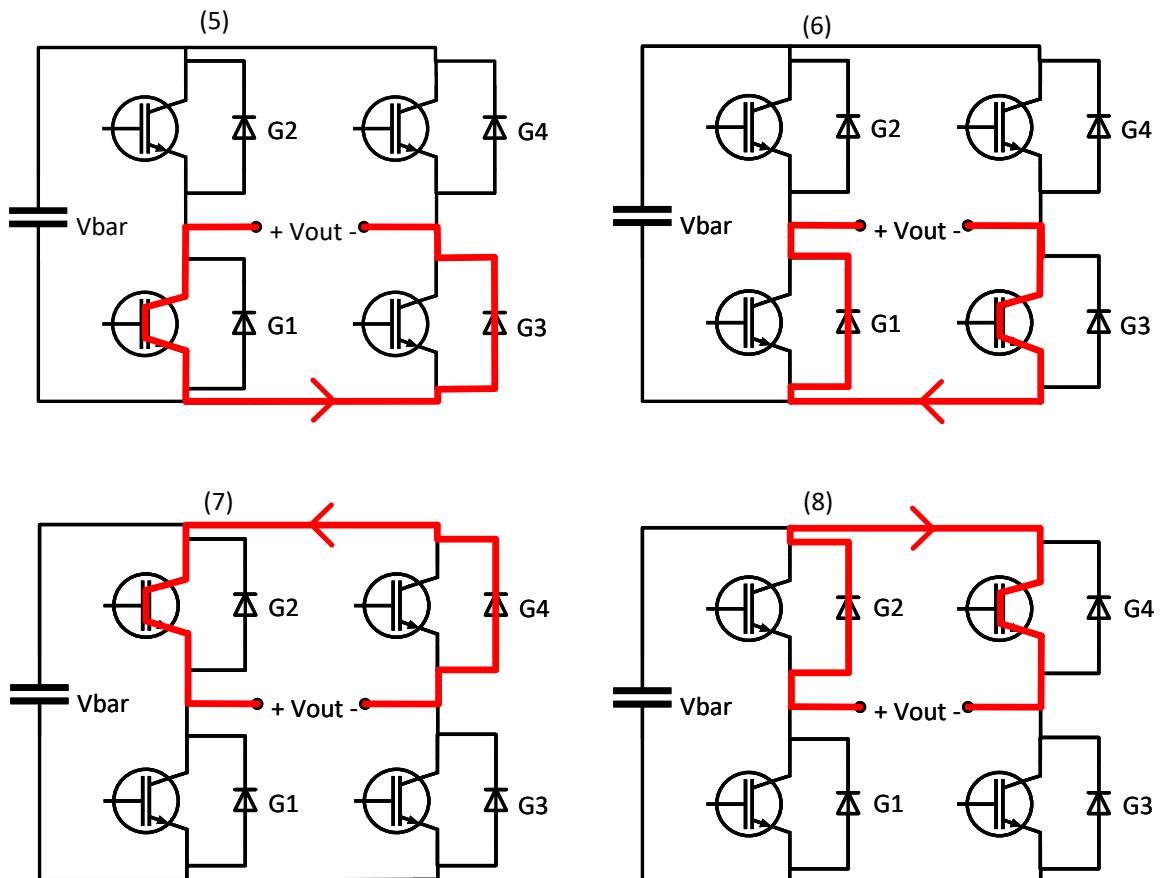

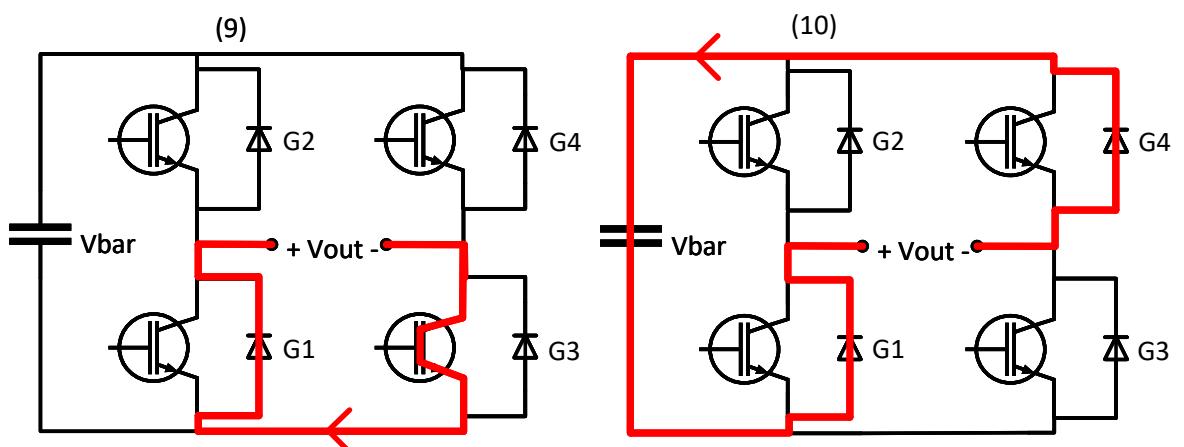

A Figura 11 apresenta as etapas de operação em que há circulação de corrente pelo barramento capacitivo do módulo. Nas duas primeiras etapas, os interruptores em diagonal são comutados e a corrente flui pelos IGBTs, fornecendo corrente para a carga e impondo tensão direta (**1**) ou inversa (**2**) sobre esta. Nas etapas seguintes, o acionamento dos interruptores se mantém o mesmo, mas a corrente flui pelos diodos dos interruptores, fazendo com que a carga forneça corrente para o barramento capacitivo, com a tensão de saída direta (**3**) ou inversa (**4**).

As demais etapas tradicionais de funcionamento da topologia são apresentadas na Figura 12. Nestas etapas a tensão de saída do módulo é nula, não havendo circulação de corrente pelo barramento capacitivo. Nas etapas (**5**) e (**6**), os interruptores inferiores são acionados simultaneamente, sendo a distinção destas etapas a circulação da corrente de saída em sentidos opostos, sempre forçando a atuação do IGBT de um dos interruptores e o diodo do interruptor adjacente. Para as etapas (**7**) e (**8**) os interruptores superiores são acionados simultaneamente, forçando a mesma estratégia de grampeamento da tensão de saída das etapas anteriores.

Para exemplificação de uma situação de falha, supõe-se uma falha em circuito aberto do interruptor superior do braço esquerdo (G2). Nesta circunstância, as etapas de operação (**1**) e (**7**) são as únicas afetadas, já que apenas nestas há circulação de corrente pelo IGBT do interruptor em questão. Estas etapas são substituídas pelas novas etapas (**9**) e (**10**), mostradas na Figura 13.

Nota-se que a etapa (**9**) é idêntica a etapa (**6**) e a etapa (**10**) é idêntica a etapa (**2**), previamente apresentadas, no que diz respeito a circulação da corrente pelo módulo. Apesar disto, estas novas etapas geradas pela situação de falha, não possuem o comando dos interruptores que representem a forma de onda de tensão de saída esperada pelo modulador.

De maneira simplificada, em condição de falha do interruptor G2, caso:

- Modulador solicite que o módulo trabalhe na etapa (**1**): o módulo ao invés disto opera na etapa (**9**), vide a falha do interruptor, e a tensão de saída é nula, ao invés de positiva.

- Modulador solicite que o módulo trabalhe na etapa (**7**): o módulo ao, invés disto, opera na etapa (**10**), com a tensão de saída sendo negativa ao invés de nula.

Figura 11 – Etapas tradicionais de funcionamento da topologia ponte completa com circulação de corrente pelo banco capacitivo.

Fonte: Próprio autor, 2023.

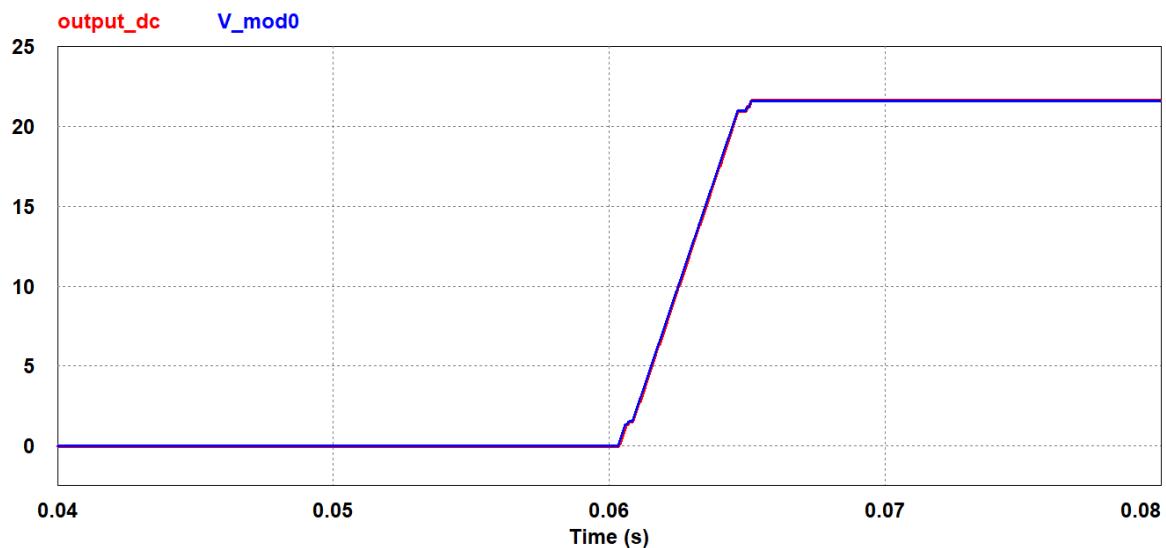

Pelas formas de onda apresentadas na Figura 14 é possível compreender melhor este processo. A forma de onda azul mostra o sinal de tensão, enquanto a forma de onda ciano mostra o sinal de corrente para um módulo ponte completa. A frequência de saída e de comutação é de 40 Hz, com modulação unipolar. Utilizou-se uma carga em característica de fonte de corrente puramente senoidal, também em 40 Hz, sem fator de deslocamento. No instante 0,05 s aplicou-se a falha do interruptor G2.

Nota-se que, previamente a aplicação da falhas, ocorre a alternância entre todas as etapas de operação regulares, com exceção das etapas (3) e (4), que apenas operam em situações de carga regenerativa. Após a aplicação da falha, as etapas (7) e (1) são substituídas pelas etapas (10) e (9), respectivamente.

Dois fatores influenciam a forma de onda de tensão de saída pós-falha:

- Fator de deslocamento: pode limitar ou completamente excluir alguma etapa de operação, já que o sentido da corrente pode forçar a condução dos diodos ao invés do IGBT danificado.

Figura 12 – Etapas tradicionais de funcionamento da topologia ponte completa sem circulação de corrente pelo banco capacitivo.

Fonte: Próprio autor, 2023.

Figura 13 – Etapas adicionais de funcionamento da topologia ponte completa com falha em circuito aberto do interruptor G2.

Fonte: Próprio autor, 2023.

Figura 14 – Formas de onda de tensão (Azul) e corrente (Ciano) pré e pós-falha do interruptor G2.

Fonte: Próprio autor, 2023.

- Modulação: isoladamente, um módulo ponte completa possui apenas as estratégias de modulação bipolar e unipolar, que possibilitam a presença de dois ou três níveis de tensão de saída, respectivamente. Dentre elas, a modulação unipolar é amplamente preferida (SINGH et al., 2012), vide a facilidade de implementação e considerável redução da THD da tensão de saída, se comparada a bipolar, optou-se por foco apenas nesta. Para tal estratégia de modulação, a alternância das etapas ditas "roda livre", na qual se aplica tensão nula na carga, é intrínseca. Com isso, inevitavelmente, a etapa (7) é substituída pela etapa (10), se esta já existia em condição normal de operação. Esta situação não é replicada, entretanto, quando aplicadas algumas estratégias de modulação exclusivas aos conversores multiníveis. Este tópico é melhor explorado no Capítulo 3.

## 2.2 ESTRATÉGIAS DE IDENTIFICAÇÃO DE FALHAS

Considerando que não é simples a implementação via *gate-driver* de uma estrutura de detecção de falhas de circuito aberto dos interruptores, diversas estratégias são estudadas na literatura para fazer esta identificação. Entre as principais estratégias apresentadas a seguir, algum fator limitante está presente, seja pela modulação necessária, pela necessidade específica de uma topologia ou pela inclusão de um sensoriamento de elevado custo.

### 2.2.1 Variação da tensão no barramento c.c.

Uma das principais diferenças da topologia MMC para a CHB, é a utilização de uma alimentação única, ao invés de múltiplos barramentos c.c. isolados, acoplados a cada módulo. Do ponto de vista de custo e volume, a topologia é atrativa se comparada ao seu concorrente direto.

Em contrapartida, o sensoriamento e a complexidade do controle destes conversores precisam ser avaliados, para determinar a viabilidade de sua utilização.

Para manter um valor estável e balanceado entre os níveis médios dos barramentos capacitivos de cada módulo, uma medição de tensão contínua é instalada no barramento dos módulos do MMC. A partir desta medição, uma estratégia de balanceamento de tensão entre os módulos é implementada. O balanceamento é necessário pela diferença de processamento de potência efetuada pelos módulos, imposta pela modulação adotada, assim como pelas não idealidades do sistema, como diferentes tempos de comutação, diferentes impedâncias dos módulos ou cargas desbalanceadas, em aplicações trifásicas.

Aproveitando-se deste sensoriamento extra, muitas estratégias utilizam a medição do nível c.c. dos barramentos para determinar uma situação de falha (Ghazanfari e Mohamed (2016); Qu et al. (2018); Kiranyaz et al. (2019); Yang, Tang e Wang (2018)). Algumas destas estratégias usam algoritmos, como redes neurais, para determinar o padrão de falha dos módulos e determinar quando esta situação ocorre, se baseando na medição do sinal do barramento c.c. em adição a tensão e/ou corrente de saída dos braços.

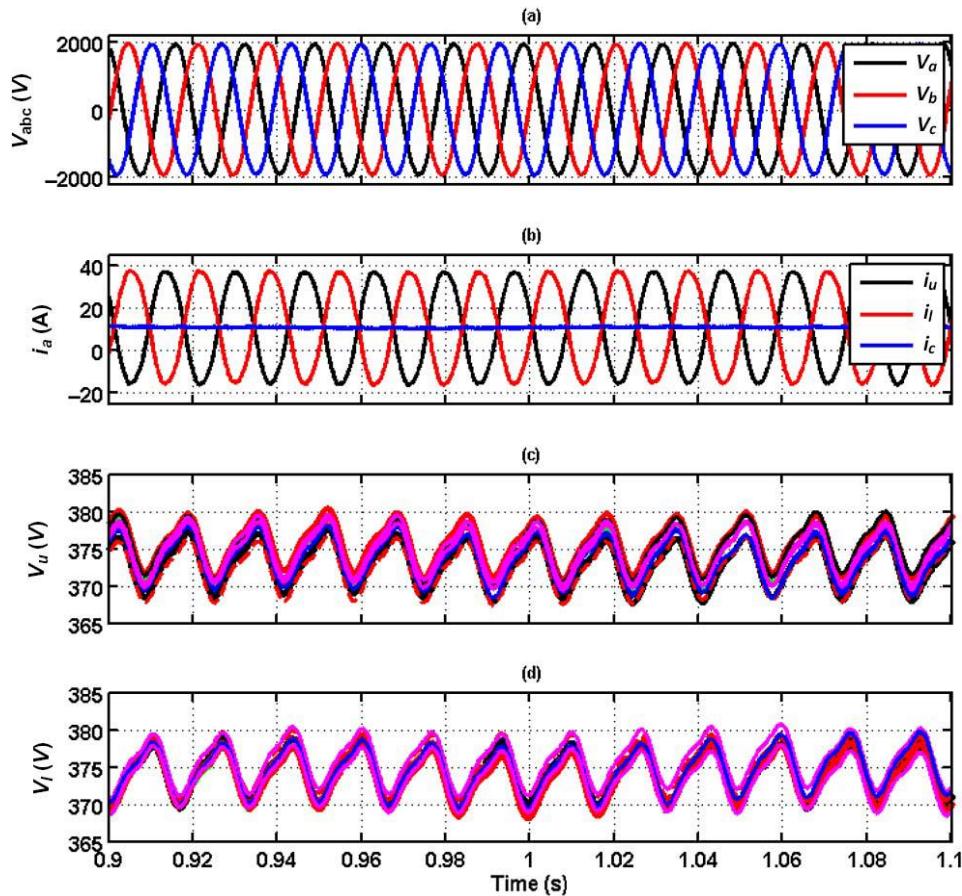

A metodologia criada por Ghazanfari e Mohamed (2016) tem, possivelmente a estrutura mais simples dentre as citadas. Para explicação deste método, o autor se utilizou de um conversor com os parâmetros apresentados na Tabela 1. Em situações regulares de funcionamento do conversor, a Figura 15 mostra as formas de onda dos sinais utilizados para identificação da falha.

Tabela 1 – Parâmetros utilizados por Ghazanfari e Mohamed (2016).

| Parâmetro                 | Dado             |

|---------------------------|------------------|

| Topologia                 | 3ph MMC          |

| Número de módulos (braço) | 10               |

| Níveis de tensão          | 21 (linha)       |

| Tensão do barramento      | 3750 V (entrada) |

| Modulação                 | PS-PWM           |

| Frequência de saída       | 60 Hz            |

| Frequência de comutação   | 1980 Hz          |

Fonte: Próprio Autor, baseado em Ghazanfari e Mohamed (2016).

Salienta-se que na Figura 15 (a) e (b), uma técnica de controle da tensão e da corrente de saída está ativa, e que a corrente diferencial ( $ic$ ) é nula, sob estas condições. Na Figura 15 (c) e (d), nota-se também um balanceamento das tensões dos barramentos c.c. entre os módulos, mantendo uma ondulação máxima de 5 % do valor médio de 375 V.

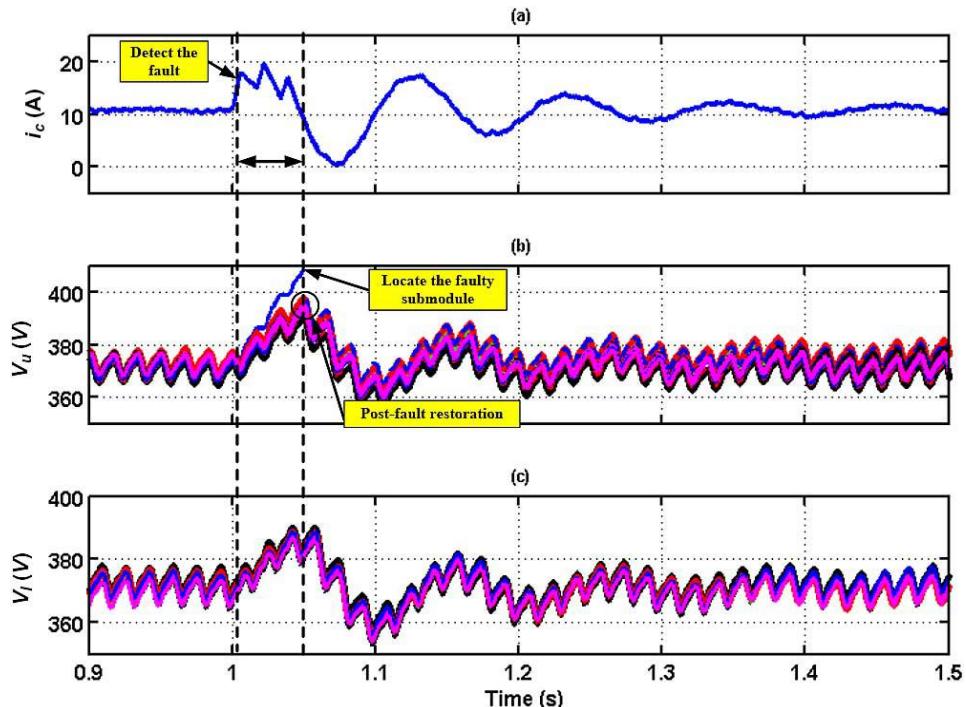

A Figura 16 mostra as formas de onda sobre a influência da falha de um dos interruptores de um módulo da fase  $a$ . A falha ocorre no instante 1,0 s. A tensão do barramento c.c. do módulo danificado se torna maior que a tensão dos demais módulos do mesmo braço (Figura 16 (b)), já que este possui agora menos etapas de descarga. Um reflexo desta falha também é visto nos demais módulos (Figura 16 (b) e (c)), causados pela interação da lógica de平衡amento de

Figura 15 – Formas de onda simuladas sob operação normal. **(a)** Tensões de saída. **(b)** Correntes do braço e corrente diferencial. **(c)** Tensões dos capacitores da parte superior do braço da fase  $a$ . **(d)** Tensões dos capacitores da parte inferior do braço da fase  $a$ .

Fonte: Retirado de Ghazanfari e Mohamed (2016).

tensão dos barramentos c.c. e de controle da tensão de saída atuando.

O método de detecção utiliza o sinal de corrente diferencial (Figura 16 **(a)**) como ponto de partida para determinação da condição de falha. A partir desta informação, o controle de balanceamento de tensão do barramento c.c. dos módulos é mitigado, e é possível determinar o módulo que tem maior derivada de tensão, reflexo de um dos interruptores danificados. Após identificado o módulo danificado, o módulo redundante em paralelo a este é acionado, paralelamente a desabilitação do módulo danificado.

O método apresenta diversas vantagens, principalmente pela utilização exclusiva de sensoriamentos nativos da topologia. É possível, através do mesmo método, também, distinguir entre as falhas de interruptores para falhas externas, causados pela carga ou até mesmo pelo sensoriamento não operando devidamente. O tempo médio, segundo o autor, para detecção, identificação e correção da falha é de 100 ms. Como mostram Kiranyaz et al. (2019) e Yang, Tang e Wang (2018), através de Redes Neurais Convolucionais (*Convolutional Neural Network - CNN*), teorias com base na mesma metodologia de identificação, propostas por Ghazanfari e Mohamed (2016), são capazes de diminuir o tempo de detecção para tempos médios inferiores a

Figura 16 – Formas de onda simuladas sob falha de circuito aberto na fase *a*. (a) Corrente diferencial. (b) Tensões dos capacitores da parte superior do braço da fase *a*. (c) Tensões dos capacitores da parte inferior do braço da fase *a*.

Fonte: Retirado de Ghazanfari e Mohamed (2016).

3 ms, apesar de possuir taxas de acerto menores, dependentes das dinâmicas de carga e ruídos de medição, o que pode tornar o método mais atrativo.

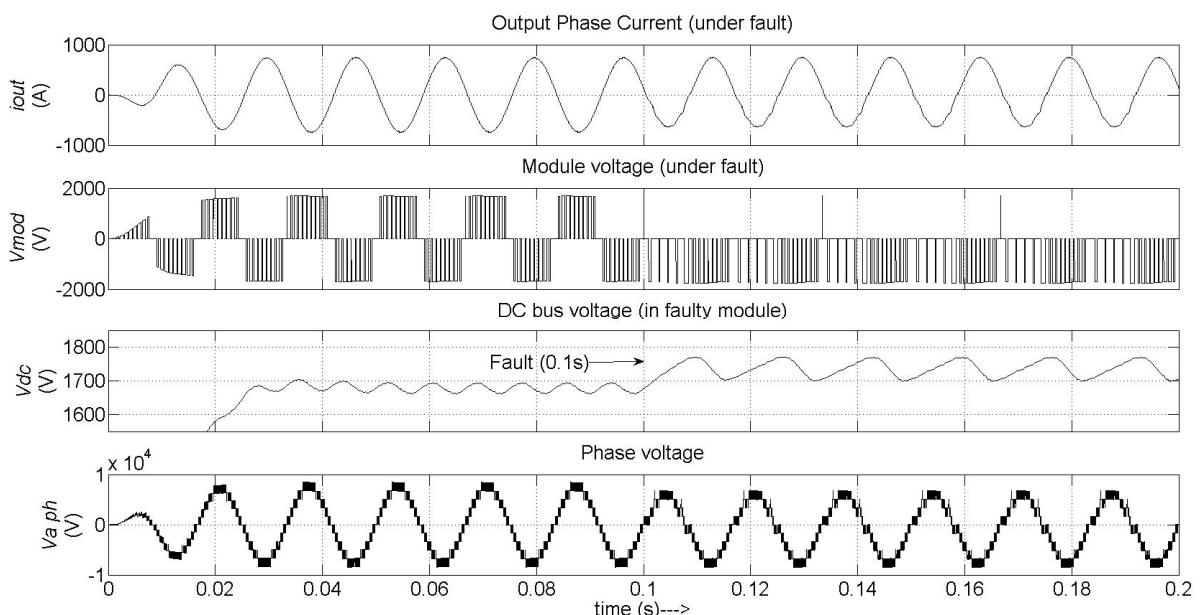

### 2.2.2 Leitura individual da tensão de saída dos módulos

A Figura 14, apresentada no capítulo 2.1, mostrou o reflexo da tensão de saída de um módulo ponte completa, operando de forma isolada, mediante a uma falha em circuito aberto de um de seus interruptores. Nas topologias multiníveis, esta característica é replicada, já que os módulos continuam operando com o processamento da mesma parcela de potência em ambos semiciclos da tensão de saída de fase/linha. A partir desta característica, conclui-se que a tensão média de saída de cada módulo é, idealmente, nula, sobre regime regular de trabalho.