DISSERTAÇÃO DE MESTRADO

**ESTUDO DE RETIFICADOR BOOST

MONOFÁSICO COM ELEVADO

FATOR DE POTÊNCIA E

COMUTAÇÃO SUAVE OPERANDO

NO MODO DCM**

RODRIGO HEINRICH

JOINVILLE, 2020

**RODRIGO HEINRICH**

**ESTUDO DE RETIFICADOR BOOST MONOFÁSICO COM

ELEVADO FATOR DE POTÊNCIA E COMUTAÇÃO SUAVE

OPERANDO NO MODO DCM**

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica do Centro de Ciências Tecnológicas da Universidade do Estado de Santa Catarina, como requisito parcial para a obtenção do grau de Mestre em Engenharia Elétrica.

Orientador: Yales Rômulo de Novaes

**Joinville**

**2020**

**Ficha catalográfica elaborada pelo programa de geração automática da

Biblioteca Setorial do CCT/UDESC,

com os dados fornecidos pelo(a) autor(a)**

Heinrich, Rodrigo

Estudo de retificador Boost monofásico com elevado fator de

potência e comutação suave operando no modo DCM / Rodrigo

Heinrich. -- 2020.

191 p.

Orientador: Yales Rômulo de Novaes

Dissertação (mestrado) -- Universidade do Estado de Santa

Catarina, Centro de Ciências Tecnológicas, Programa de

Pós-Graduação em Engenharia Elétrica, Joinville, 2020.

1. Conversor Taipei. 2. Boost interleaved. 3. Modo de condução

descontínua. 4. Comutação suave. 5. Modulação em frequência. I.

Novaes, Yales Rômulo de. II. Universidade do Estado de Santa

Catarina, Centro de Ciências Tecnológicas, Programa de

Pós-Graduação em Engenharia Elétrica. III. Título.

# RODRIGO HEINRICH

## ESTUDO DE RETIFICADOR BOOST MONOFÁSICO COM ELEVADO FATOR DE POTÊNCIA E COMUTAÇÃO SUAVE OPERANDO NO MODO DCM

Dissertação apresentada ao Programa de Pós-Graduação em Engenharia Elétrica do Centro de Ciências Tecnológicas da Universidade do Estado de Santa Catarina, como requisito parcial para a obtenção do grau de Mestre em Engenharia Elétrica.

### Banca Examinadora:

#### Orientador:

---

**Prof. Yales Rômulo de Novaes, Dr.**

UDESC

#### Membros:

---

**Prof. Joselito Anastacio Heerdt, Dr.**

UDESC

---

**Prof. Carlos Henrique Illa Font, Dr.**

UTFPR

---

**Prof. Sérgio Vidal Garcia Oliveira, Dr.**

UDESC

Joinville, 22 de dezembro de 2020

*Este trabalho é dedicado às crianças adultas que,

quando pequenas, sonharam em se tornar cientistas.*

## AGRADECIMENTOS

Agradeço primeiramente a Deus, que guiou os meus passos nessa longa caminhada.

Agradeço aos meus pais Arlindo Heinrich e Catia Arlene Hoeller Heinrich por todo o suporte, amor e incentivo durante minha trajetória na universidade e pela vida.

Agradeço ao meu irmão Tiago Heinrich pela amizade e companheirismo.

Agradeço aos professores do Programa de Pós-Graduação em Engenharia Elétrica da UDESC, por todos os ensinamentos repassados durante as disciplinas e trabalhos realizados, que contribuíram de forma significativa para minha formação acadêmica. Em especial agradeço ao meu orientador Dr. Yales Rômulo de Novaes pela orientação e dedicação ao longo desse trabalho.

Agradeço aos engenheiros Me. Gustavo Ceretta Flore, Me. Douglas Pereira da Silva e ao professor Dr. Sérgio Vidal Garcia de Oliveira por proporcionar a oportunidade de trabalho conjunto entre a UDESC e Embraco, pelas orientações e conselhos que contribuíram para o fortalecimento dessa pesquisa.

Agradeço aos meus colegas do Núcleo de Processamento de Energia Elétrica - NPEE, pelas discussões e trocas de conhecimentos, em especial aos engenheiros Me. Eduardo Falchetti Sovrani, Me. Fabiano Mendes Ribeiro e Me. Rafael Felipe Van Kan.

Agradeço ao NPEE pela infraestrutura, suporte e equipamentos disponibilizados para a realização desse trabalho.

Agradeço a FAPESC e à Embraco pela bolsa de estudos e pelo recurso financeiro disponibilizado para a compra de materiais.

*“The best thing in life is to go ahead with all your plans and your dreams, to embrace life and to live everyday with passion, to lose and still keep the faith and to win while being grateful. All of this because the world belongs to those who dare to go after what they want. And because life is really too short to be insignificant”.*

*(Charlie Chaplin)*

## RESUMO

Nesse trabalho é apresentado o estudo de uma topologia de conversor CA-CC monofásico, derivada do Retificador Trifásico Taipei, proposto por Milan M. Jovanovic. A topologia é bem similar a um Boost *Interleaved* com ponto central, com vantagens em relação a baixas perdas de comutação, controle simples e elevada imunidade a ruídos de modo comum. O propósito da pesquisa é analisar o potencial desse retificador em uma versão monofásica, levando em consideração a eficiência e os custos. A topologia deve ser capaz de cumprir as normas internacionais IEC 61000-3-2 e CISPR 14. São apresentados os métodos de projetos dos semicondutores e elementos magnéticos de modo a amenizar volume e custo, levando sempre em consideração a eficiência. A topologia uma vez projetada é comparada com o conversor Boost em modo de condução contínua. É feito um estudo de emissão eletromagnética conduzida do retificador, também como de estruturas de filtros capazes de suprir essa interferência de forma eficaz e econômica.

**Palavras-chave:** Conversor Taipei, Comutação suave, modulação em frequência, modo de condução descontínua.

## ABSTRACT

This work introduce the study of a AC-DC single phase topology, that emerged from Three-Phase Taipei Rectifier, introduced by Milan M. Jovanovic. The topology is very similar to a interleaved boost with central point, with advantages to commutation losses, simple control and high immunity to common mode noise. The propose of this research is to analyze the potential of this rectifier in a single-phase version, taking in consideration the efficiency and cost. This topology must be capable of meeting in IEC 61000-3-2 and CISPR 14 international standards. It is introduced the methods to design the semiconductors and magnetics components in a way to decrease size and cost, always taking into account the efficiency. The topology was compared with a Boost Converter in continuous conduction mode. Also it was studied the converter's electromagnetic interference capability, and further some filters capable of improving this interference.

**Keywords:** Taipei Rectifier, soft commutation, frequency modulation, discontinuous conduction mode.

## LISTA DE ILUSTRAÇÕES

|                                                                                                                            |    |

|----------------------------------------------------------------------------------------------------------------------------|----|

| Figura 1 – Retificador Boost para Correção de Fator de Potência . . . . .                                                  | 35 |

| Figura 2 – Retificador Boost Interleaved Clássico com Duas Células Paralelas . . . . .                                     | 36 |

| Figura 3 – Retificador Nabae . . . . .                                                                                     | 37 |

| Figura 4 – Retificador Nabae com capacitores eletrolíticos no filtro de entrada . . . . .                                  | 38 |

| Figura 5 – Retificador Nabae com tensão reduzida nos interruptores . . . . .                                               | 38 |

| Figura 6 – Topologia do Retificador Taipei . . . . .                                                                       | 40 |

| Figura 7 – Topologia do Taipei Monofásico Proposta . . . . .                                                               | 42 |

| Figura 8 – Resultados da Comparaçāo entre os Componentes de Cada Conversor .                                               | 44 |

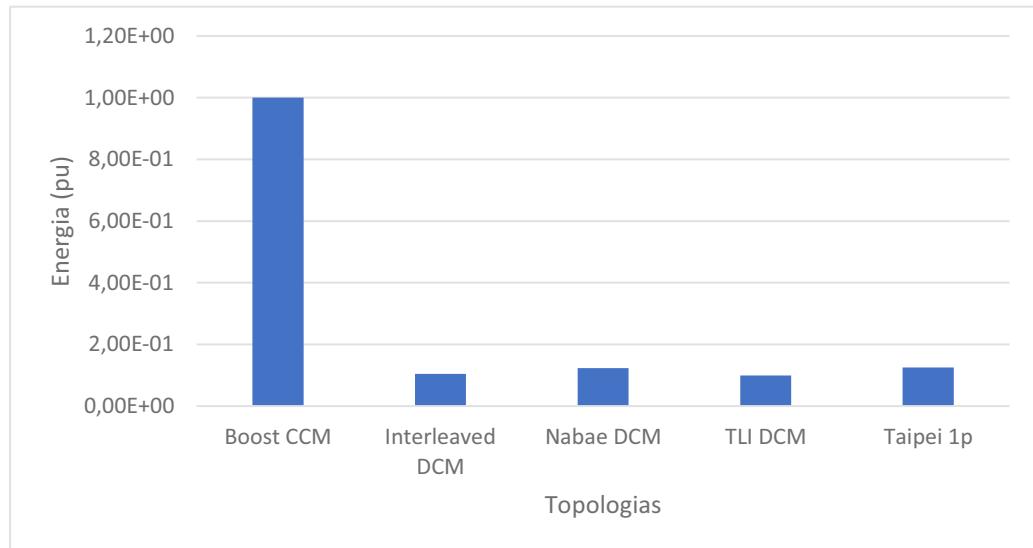

| Figura 9 – Comparaçāo da Energia Total dos Indutores Boost . . . . .                                                       | 45 |

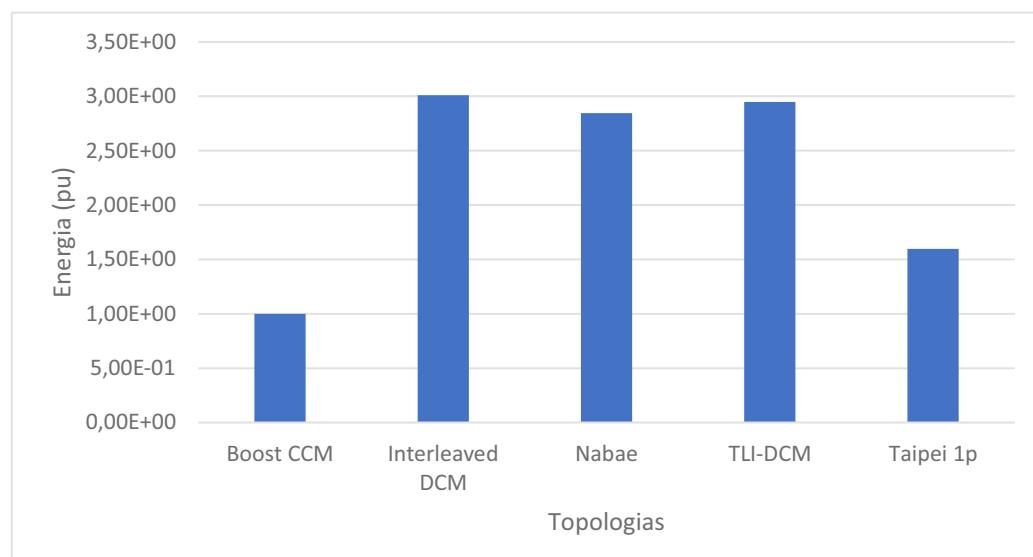

| Figura 10 – Comparaçāo da Energia Total dos Indutores de Filtro . . . . .                                                  | 45 |

| Figura 11 – Comparaçāo entre os Capacitores de Barramento . . . . .                                                        | 46 |

| Figura 12 – Comparaçāo entre os Capacitores de Barramento . . . . .                                                        | 46 |

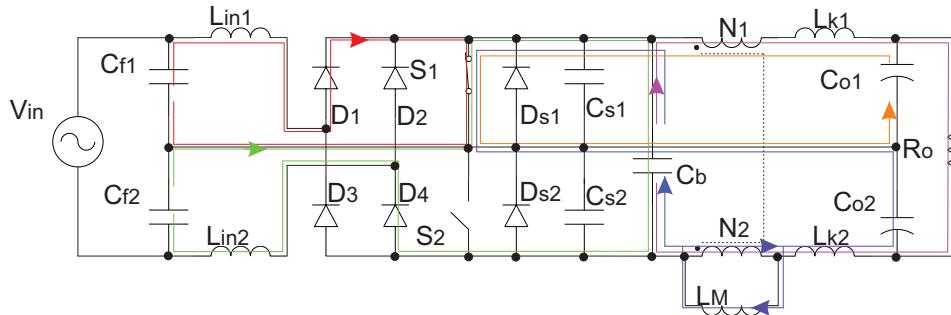

| Figura 13 – Primeira Etapa de Operação . . . . .                                                                           | 49 |

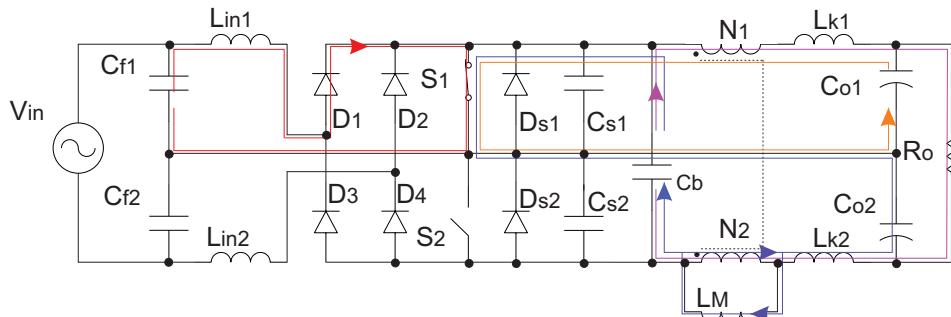

| Figura 14 – Segunda Etapa de Operação . . . . .                                                                            | 50 |

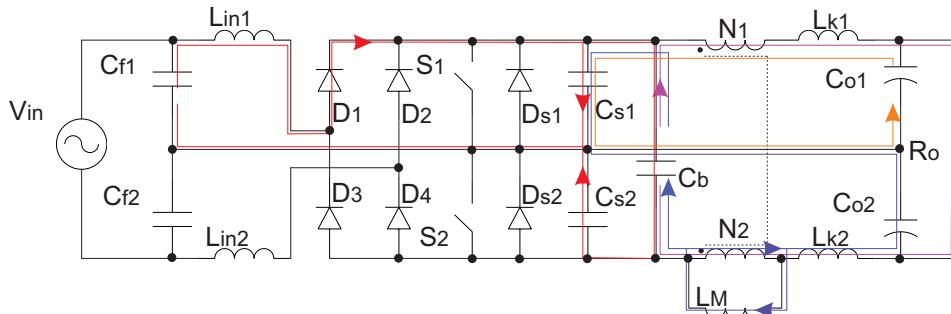

| Figura 15 – Terceira Etapa de Operação . . . . .                                                                           | 50 |

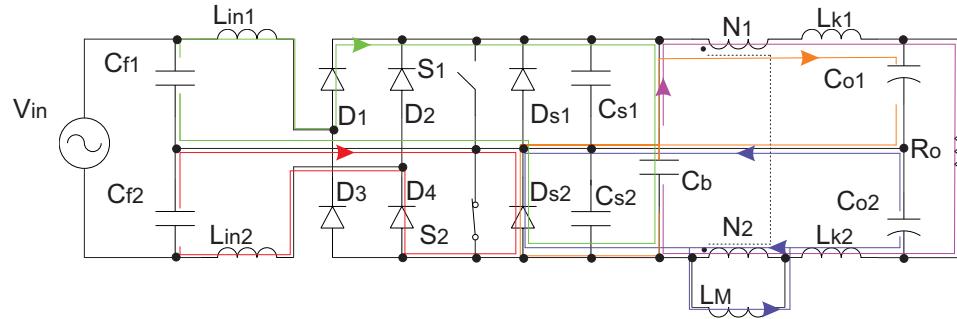

| Figura 16 – Quarta Etapa de Operação . . . . .                                                                             | 50 |

| Figura 17 – Quinta Etapa de Operação . . . . .                                                                             | 51 |

| Figura 18 – Sexta Etapa de Operação . . . . .                                                                              | 51 |

| Figura 19 – Sétima Etapa de Operação . . . . .                                                                             | 52 |

| Figura 20 – Oitava Etapa de Operação . . . . .                                                                             | 52 |

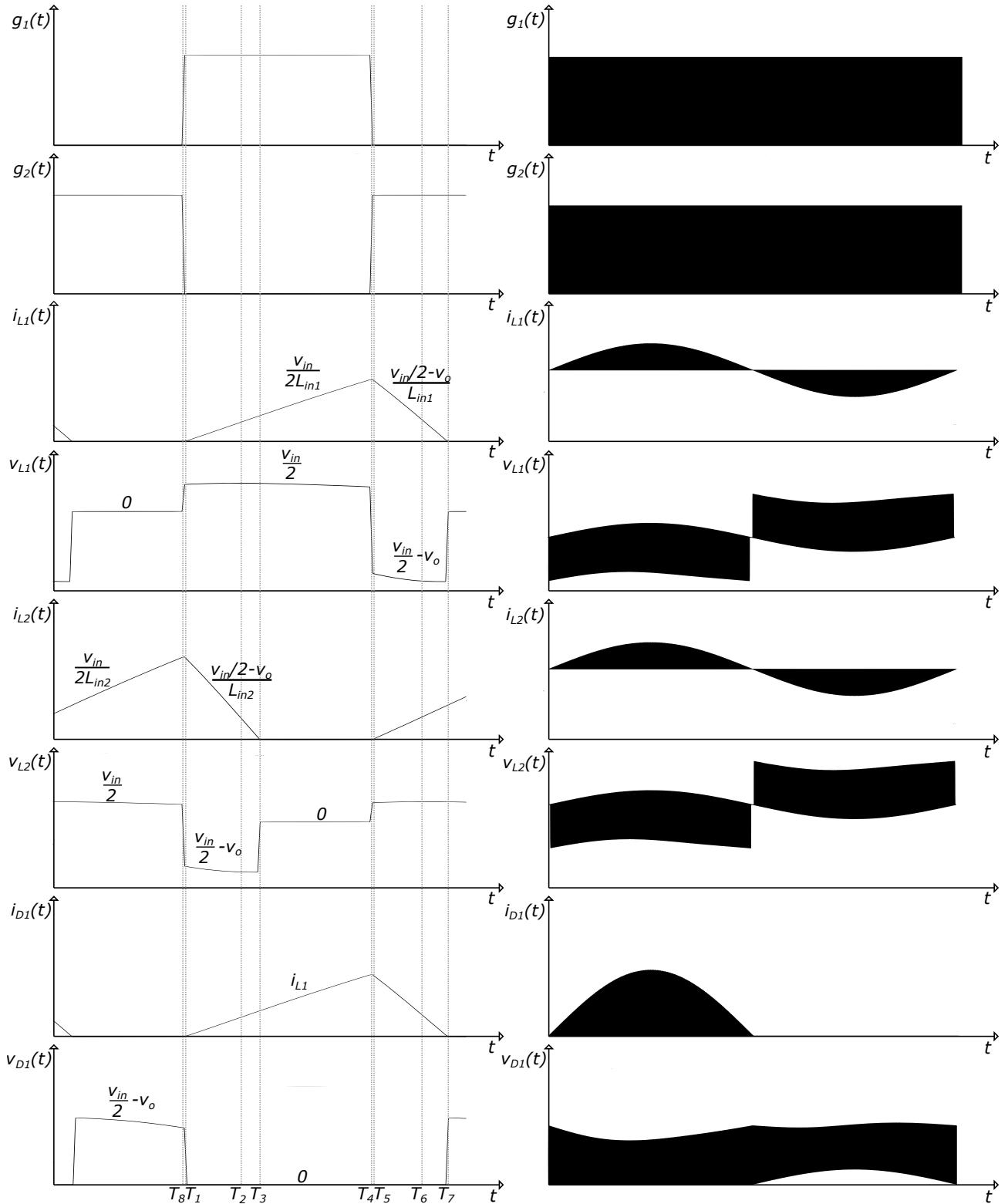

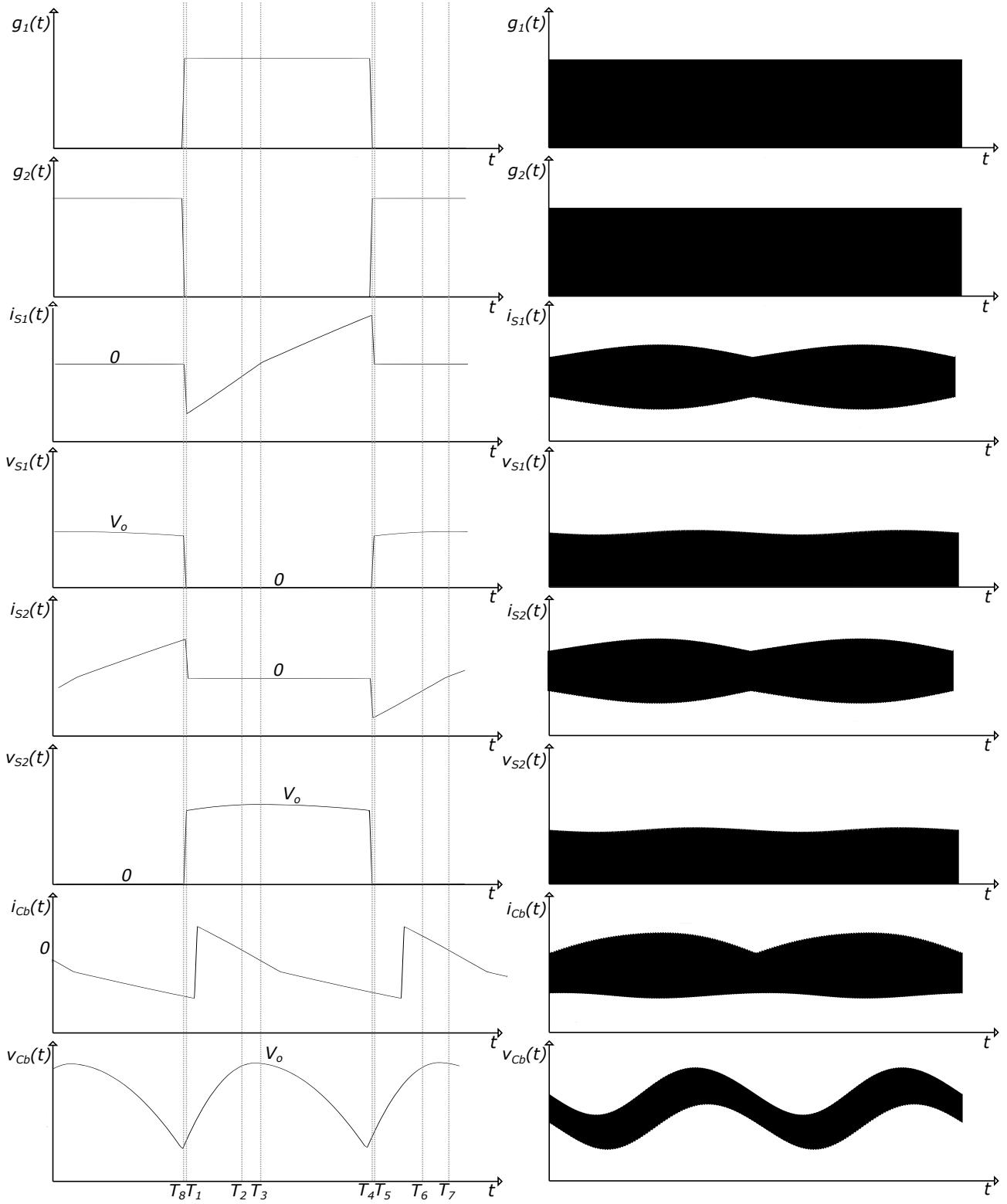

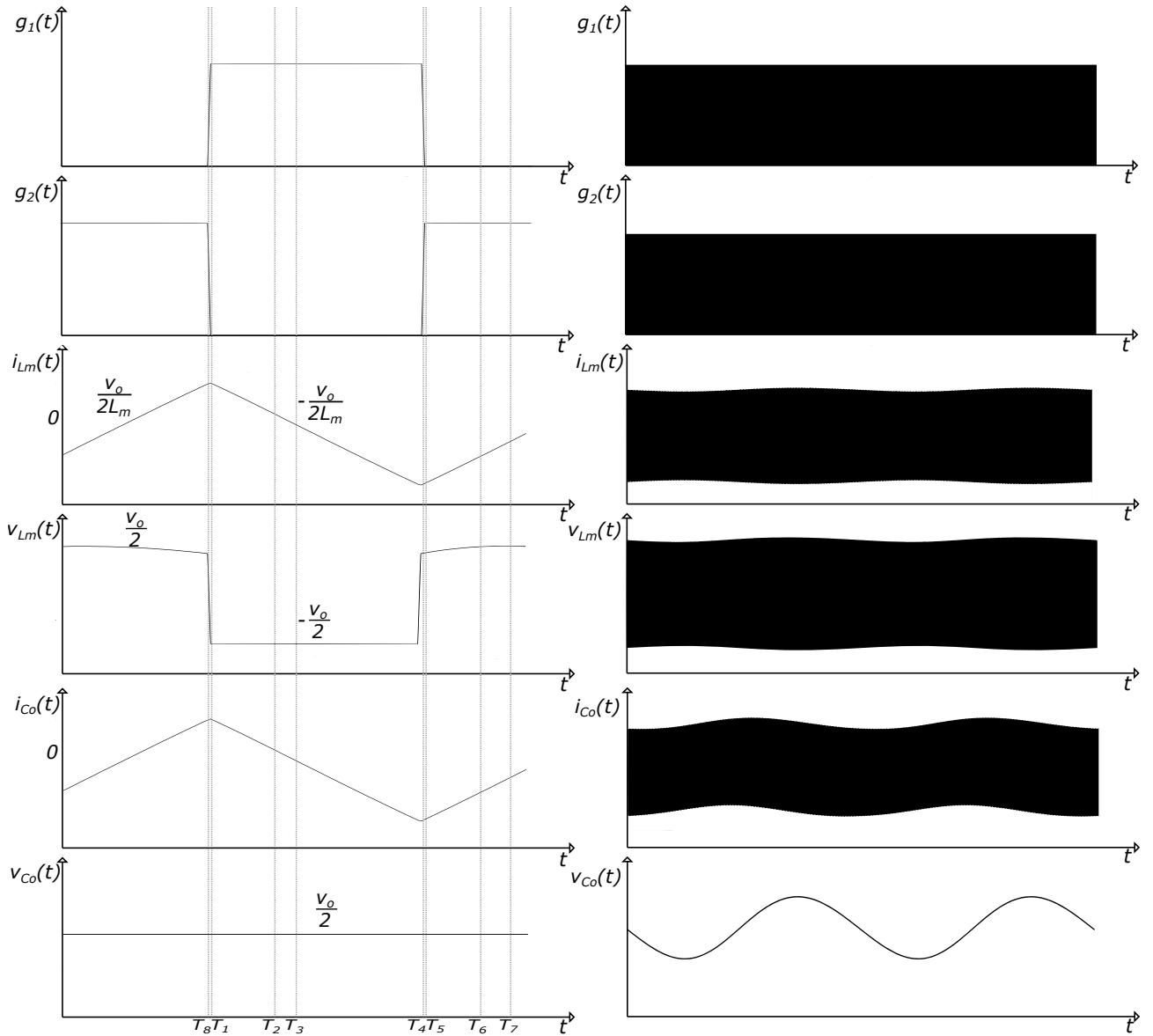

| Figura 21 – Formas de Onda dos Sinais de Gatilho, $L_{in}$ e $D_1$ para um Ciclo de Comutação e da Rede Elétrica . . . . . | 53 |

| Figura 22 – Formas de Onda dos Sinais de Gatilho, $S$ e $C_b$ para um Ciclo de Comutação e da Rede Elétrica . . . . .      | 54 |

| Figura 23 – Formas de Onda dos Sinais de Gatilho, $L_M$ e $C_o$ para um Ciclo de Comutação e da Rede Elétrica . . . . .    | 55 |

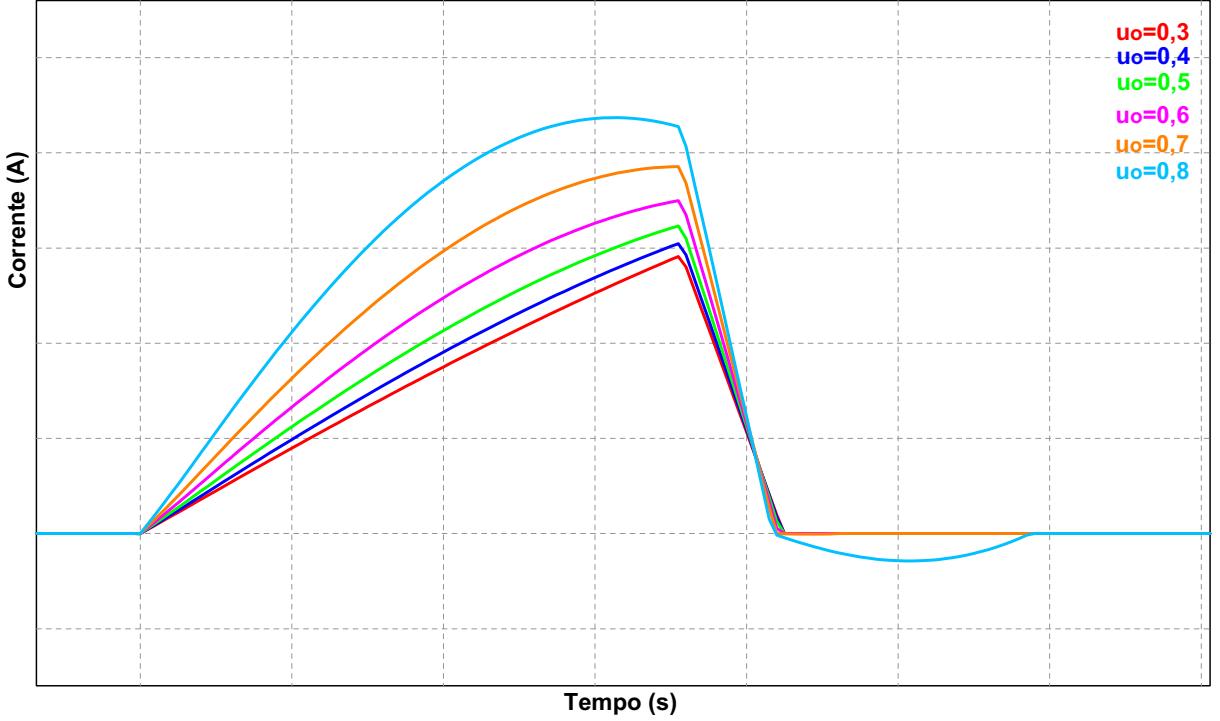

| Figura 24 – Corrente em $L_{in}$ para diferentes $\mu_o$ . . . . .                                                         | 57 |

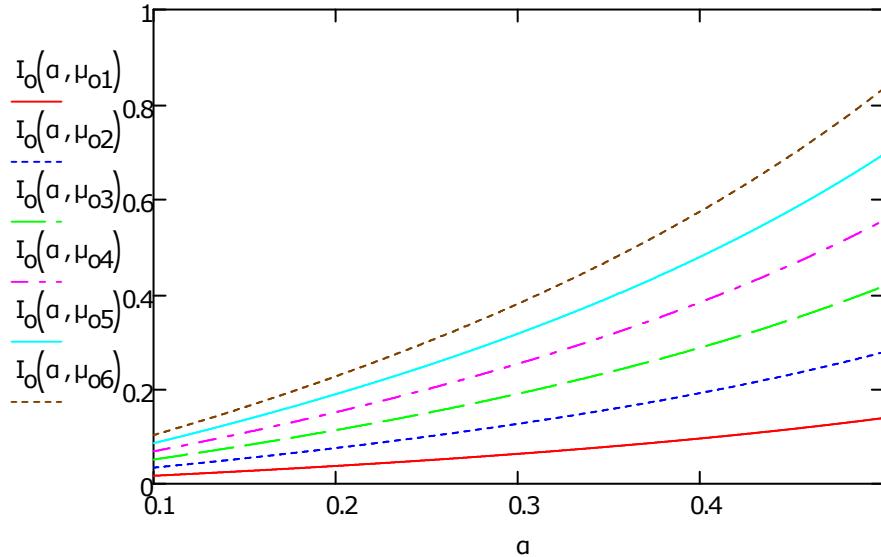

| Figura 25 – Corrente de carga normalizada em função de $\alpha$ para diversos $\mu_o$ . . . . .                            | 62 |

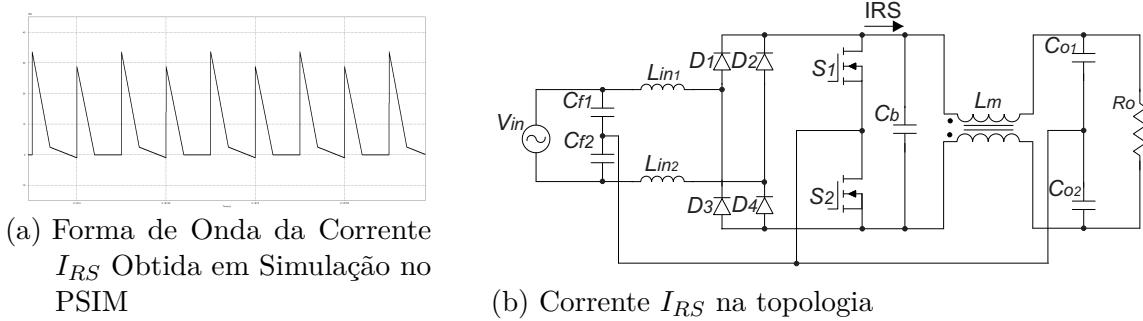

| Figura 26 – Corrente $I_{RS}$ . . . . .                                                                                    | 62 |

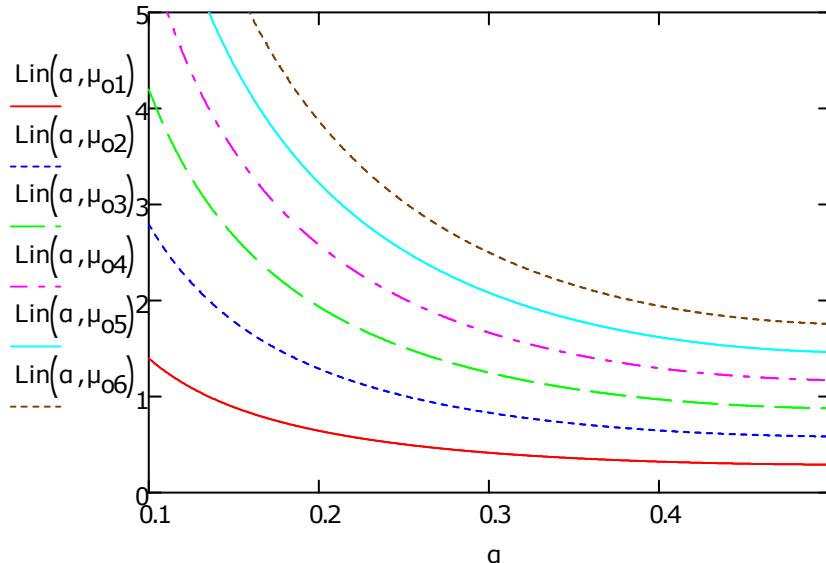

| Figura 27 – Indutância normalizada em função de $\alpha$ para diversos $\mu_o$ . . . . .                                   | 63 |

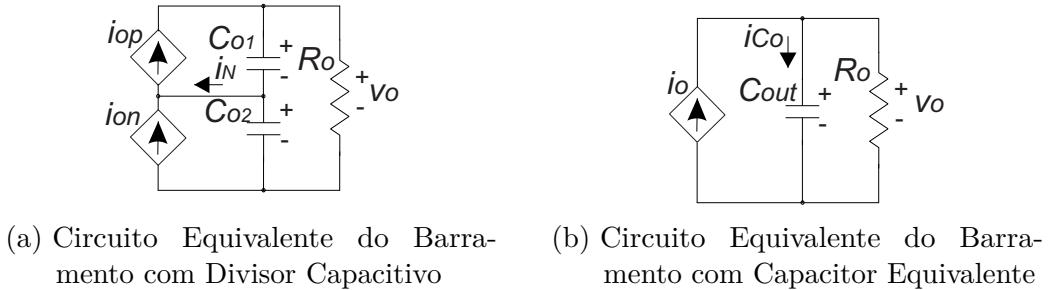

| Figura 28 – Circuitos Equivalentes Vistos a Partir do Barramento . . . . .                                                 | 66 |

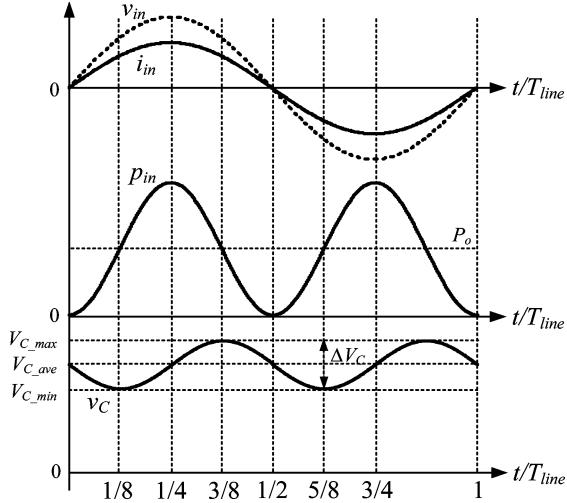

| Figura 29 – Tensão no barramento CC para fator de potência unitário . . . . .                                              | 67 |

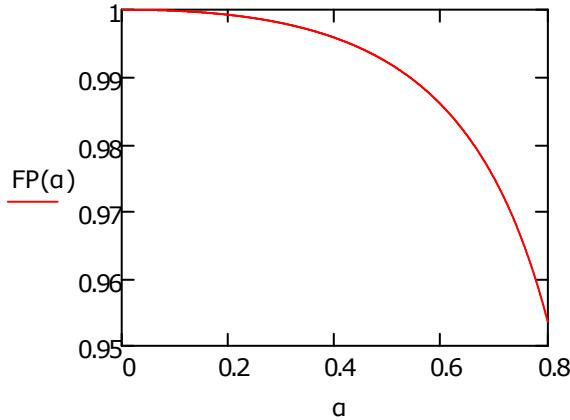

| Figura 30 – Fator de Potência para diversos valores de $\alpha$ . . . . .                                                  | 69 |

| Figura 31 – THD para diversos valores de $\alpha$ . . . . .                                                                | 69 |

| Figura 32 – Tipos de Comutação . . . . .                                                                                   | 73 |

| Figura 33 – Corrente de recuperação reversa no diodo . . . . .                                                             | 76 |

| Figura 34 – Comutação dos interruptores na Quarta Etapa de Operação . . . . .                                              | 77 |

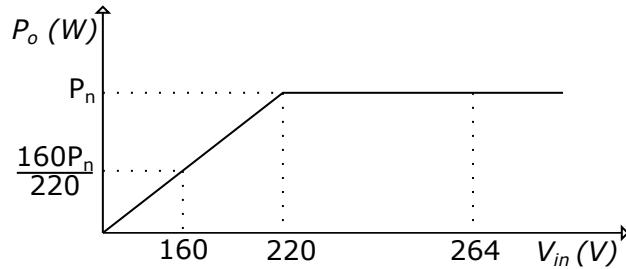

| Figura 35 – Variação da potência de saída em função da tensão de entrada . . . . .                                         | 82 |

|                                                                                                                                                                                           |     |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

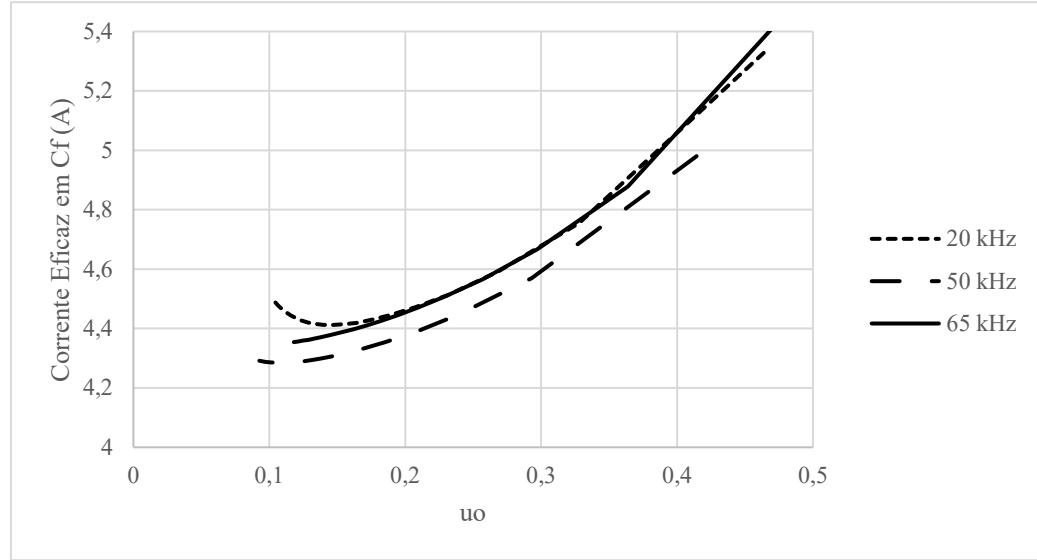

| Figura 36 – Corrente eficaz em $C_f$ para diferentes valores de $\mu_o$ em retificadores de 1 kW . . . . .                                                                                | 83  |

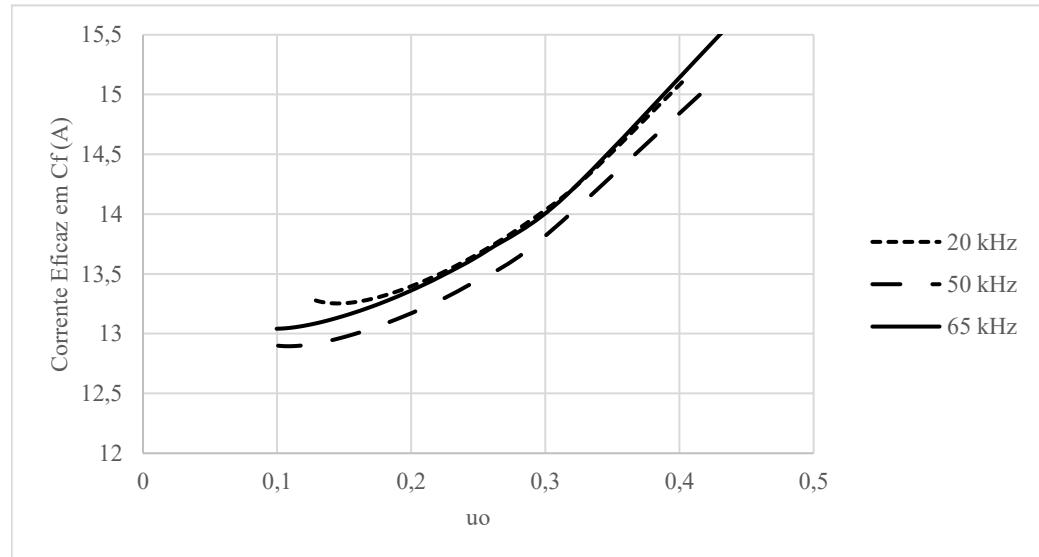

| Figura 37 – Corrente eficaz em $C_f$ para diferentes valores de $\mu_o$ em retificadores de 3 kW . . . . .                                                                                | 83  |

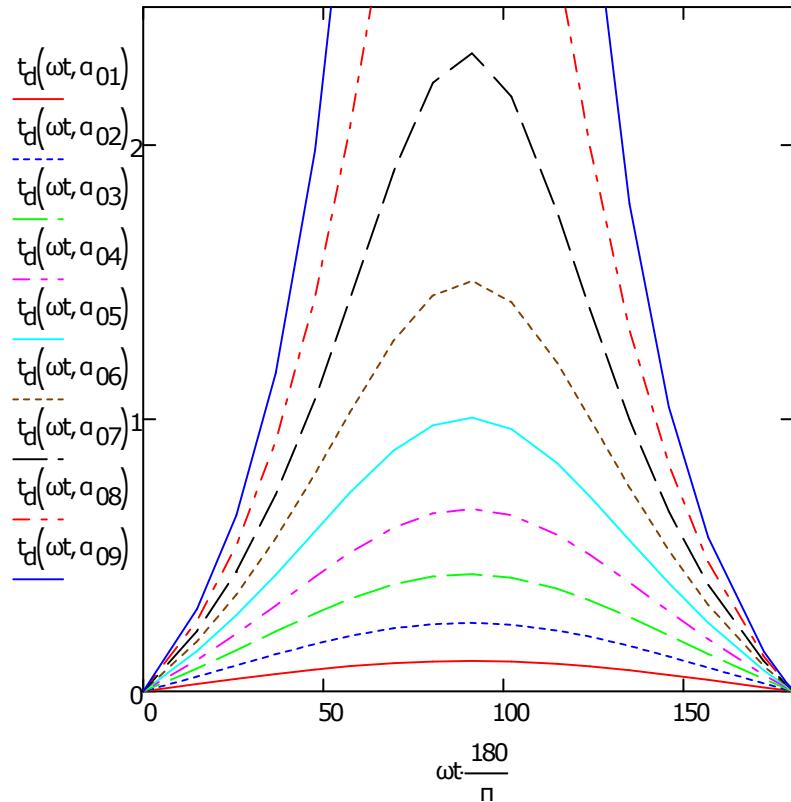

| Figura 38 – Tempo de desmagnetização normalizado . . . . .                                                                                                                                | 84  |

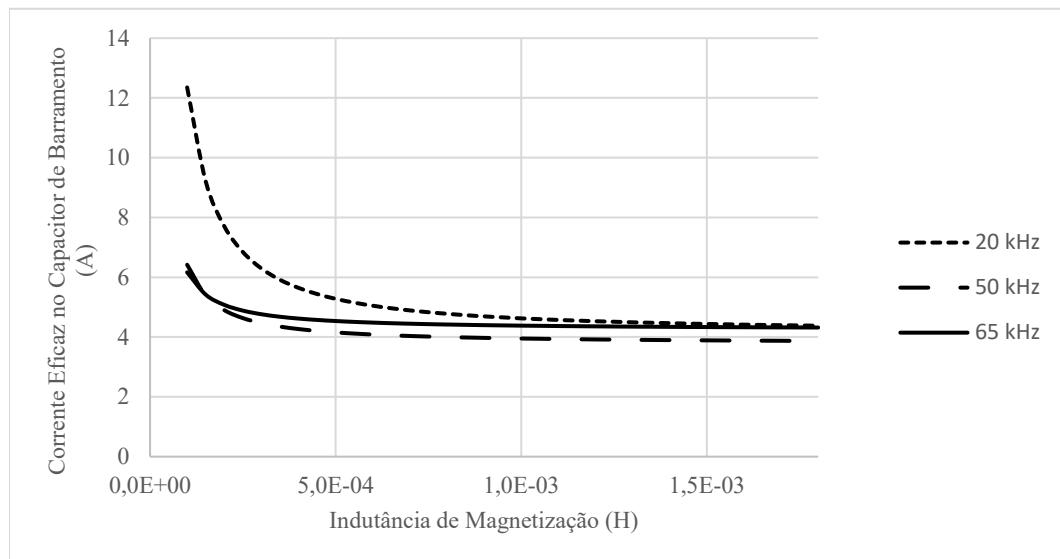

| Figura 39 – Corrente eficaz em $C_o$ para diferentes $L_c$ nas topologias de 1 kW . . . . .                                                                                               | 85  |

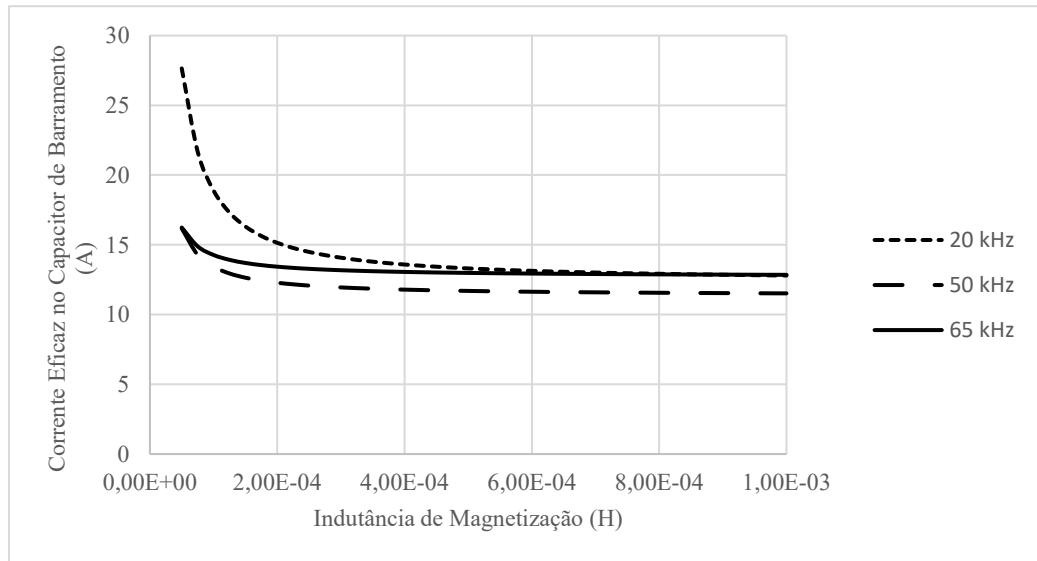

| Figura 40 – Corrente eficaz em $C_o$ para diferentes $L_c$ nas topologias de 3 kW . . . . .                                                                                               | 86  |

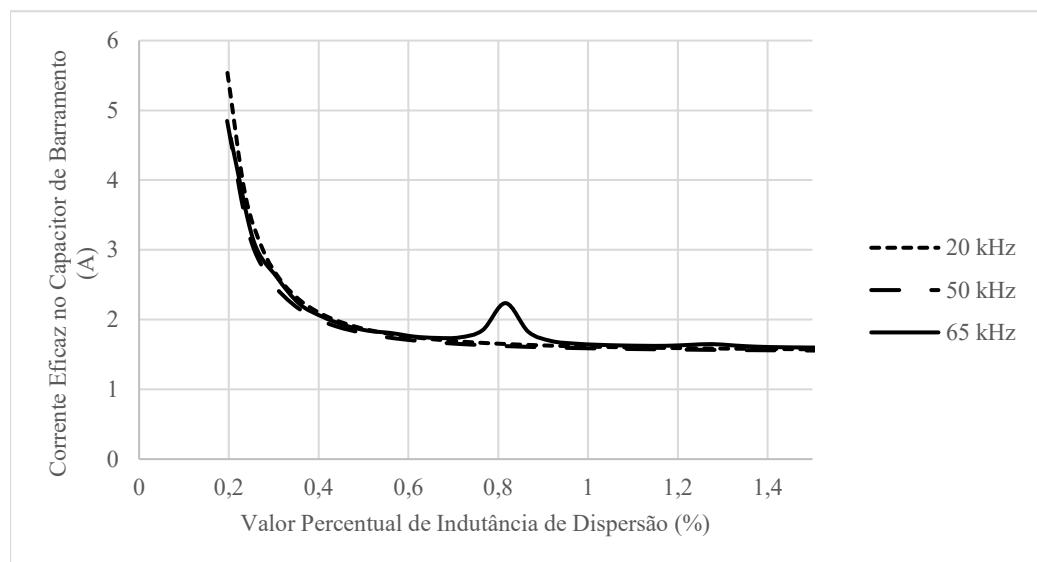

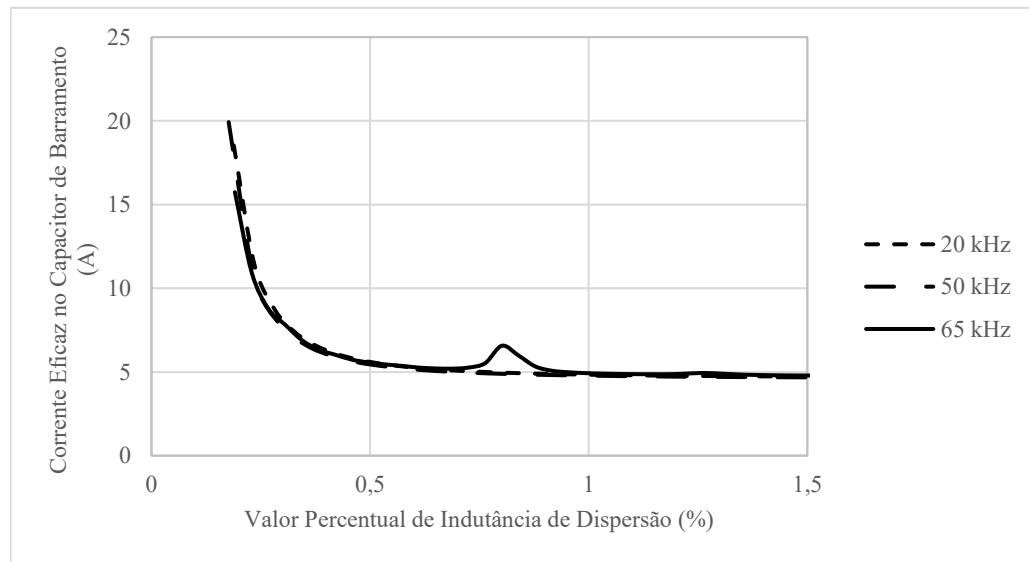

| Figura 41 – Variação do valor de corrente eficaz nos capacitores de barramento em função de diferentes $L_{c,lk}$ para os projetos de 1 kW . . . . .                                      | 86  |

| Figura 42 – Variação do valor de corrente eficaz nos capacitores de barramento em função de diferentes $L_{c,lk}$ para os projetos de 3 kW . . . . .                                      | 87  |

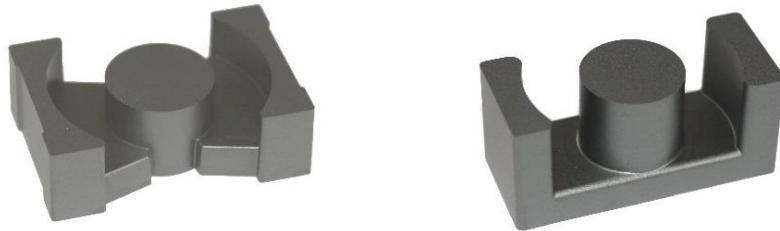

| Figura 43 – Formato dos Núcleos Utilizados no Trabalho . . . . .                                                                                                                          | 88  |

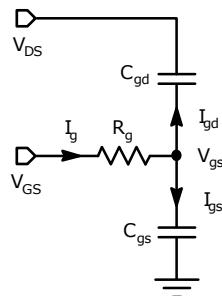

| Figura 44 – Modelo interno do mosfet . . . . .                                                                                                                                            | 104 |

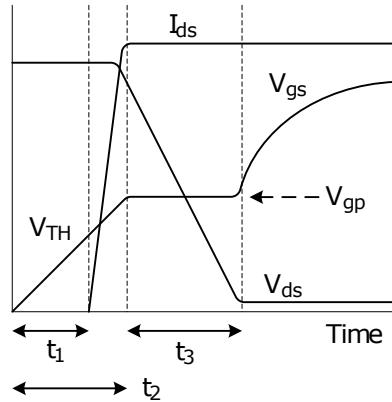

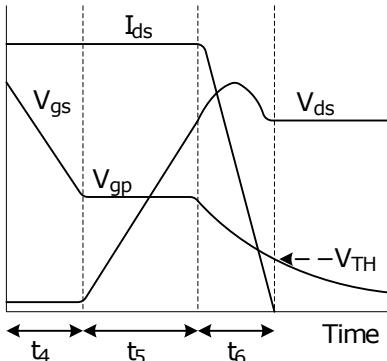

| Figura 45 – Formas de onda para entrada em condução do mosfet . . . . .                                                                                                                   | 105 |

| Figura 46 – Circuito Equivalente do Mosfet para Cálculo de Perdas de Comutação .                                                                                                          | 106 |

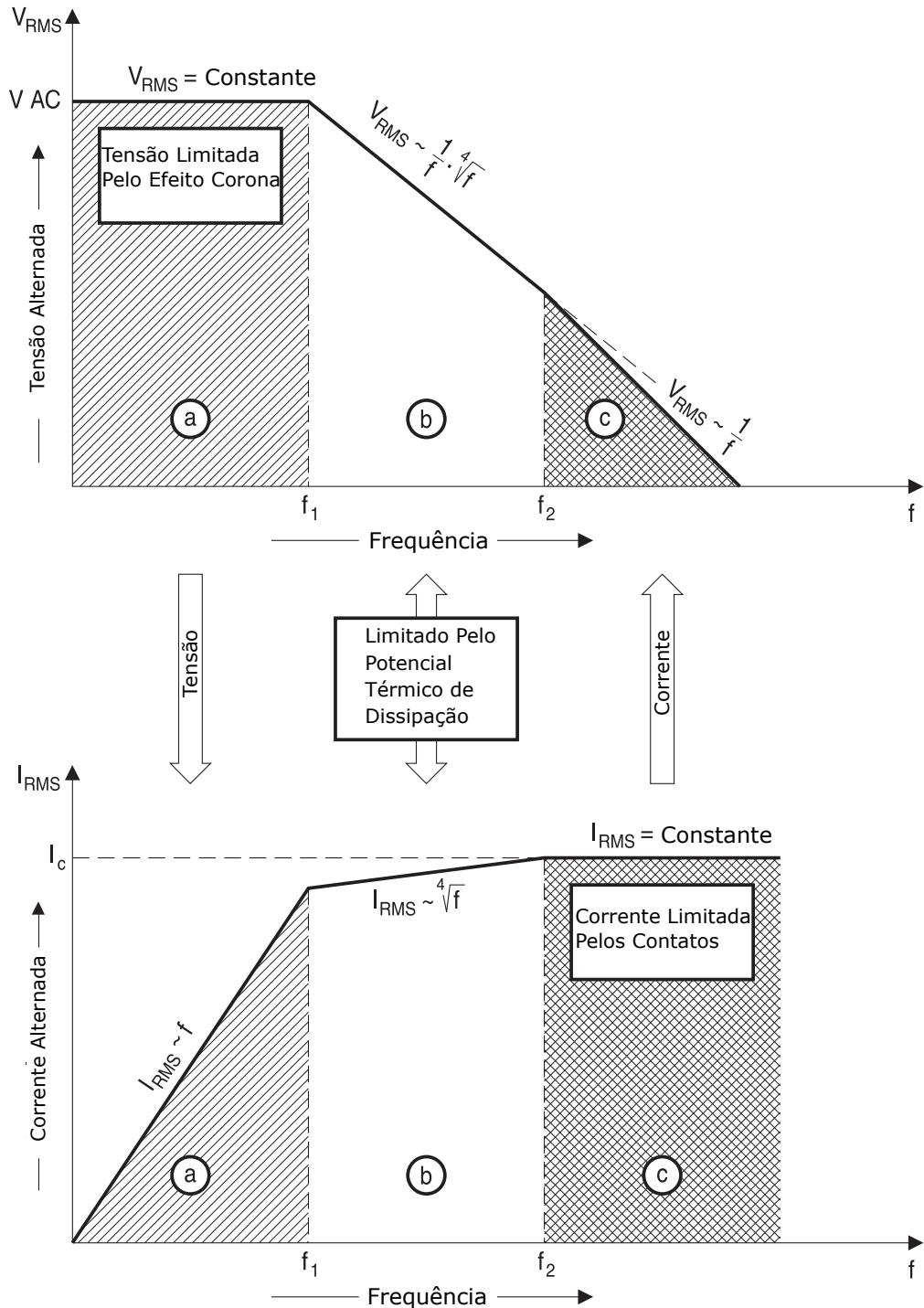

| Figura 47 – Tensão e Corrente Eficaz em Capacitores de Filme em Função da Frequência . . . . .                                                                                            | 112 |

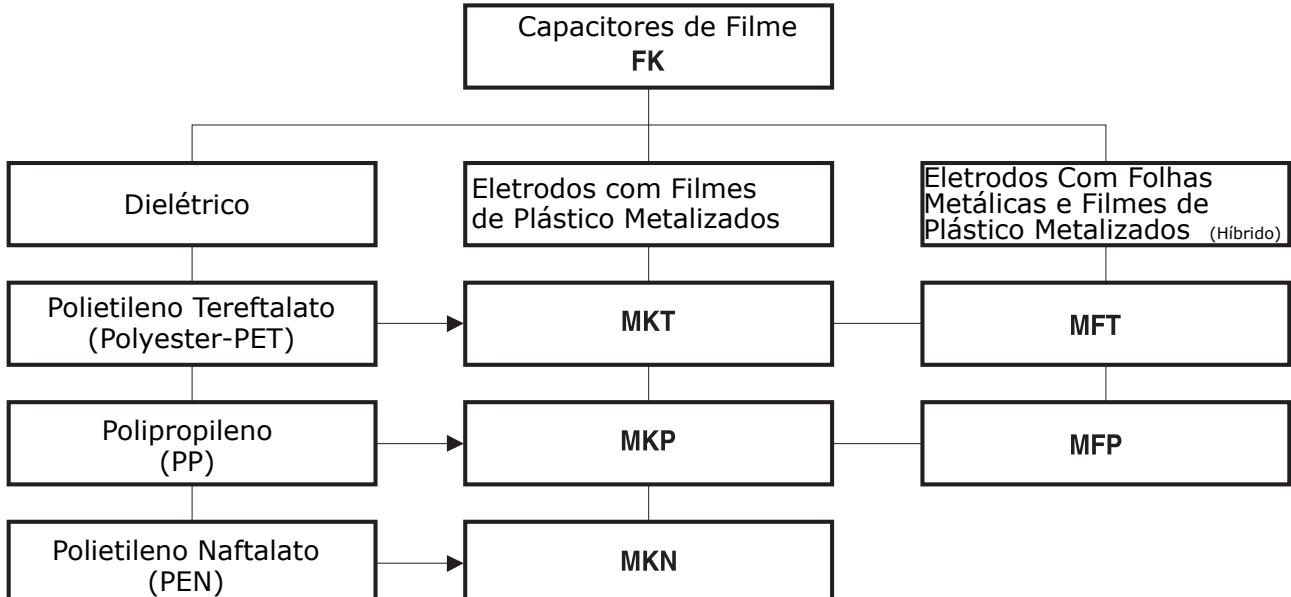

| Figura 48 – Tipos de Capacitores de Filme da TDK . . . . .                                                                                                                                | 113 |

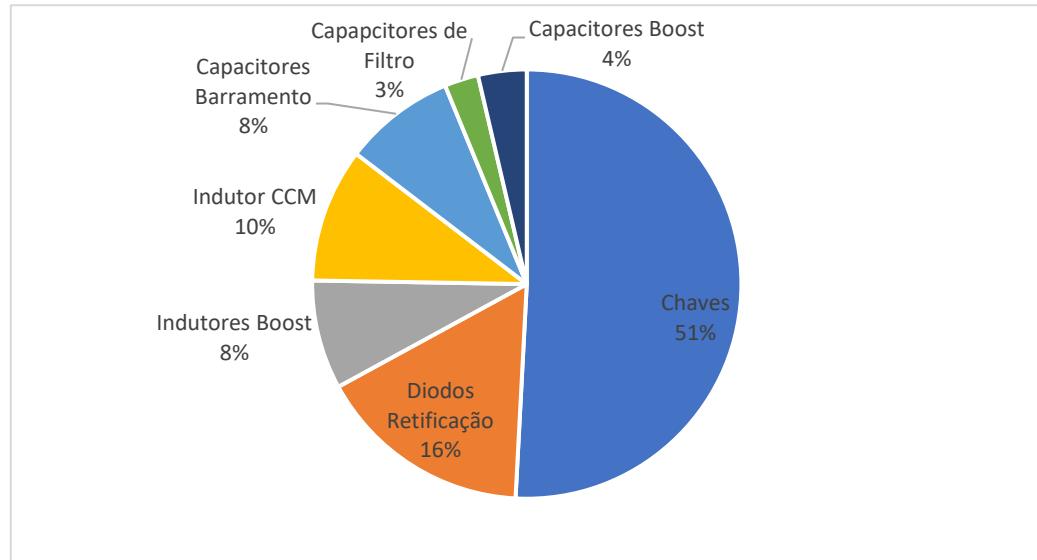

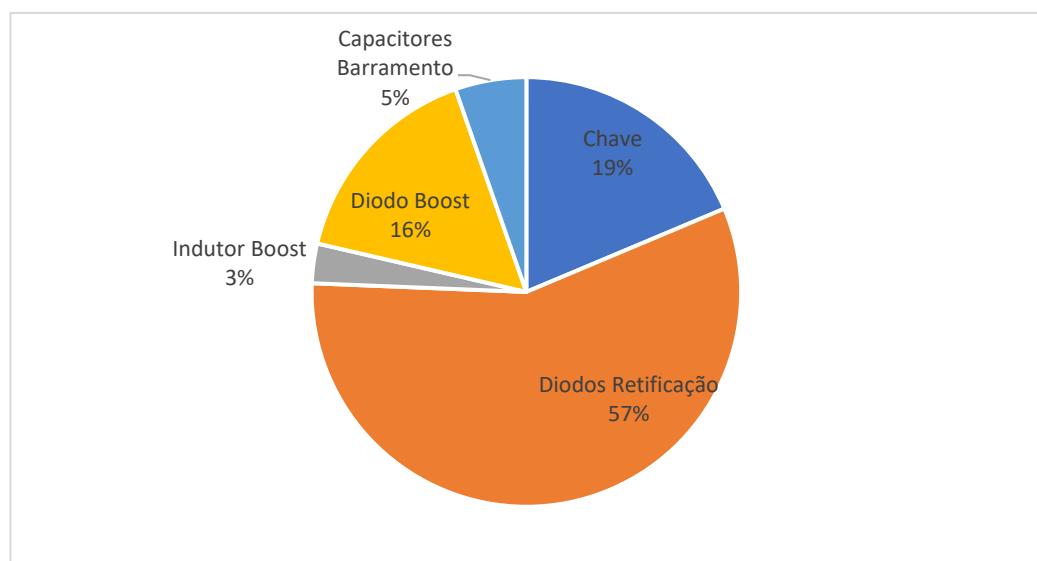

| Figura 49 – Distribuição de perdas em condição nominal de operação no SPT . . . . .                                                                                                       | 129 |

| Figura 50 – Distribuição de perdas em condição nominal de operação no BCCM . . . . .                                                                                                      | 129 |

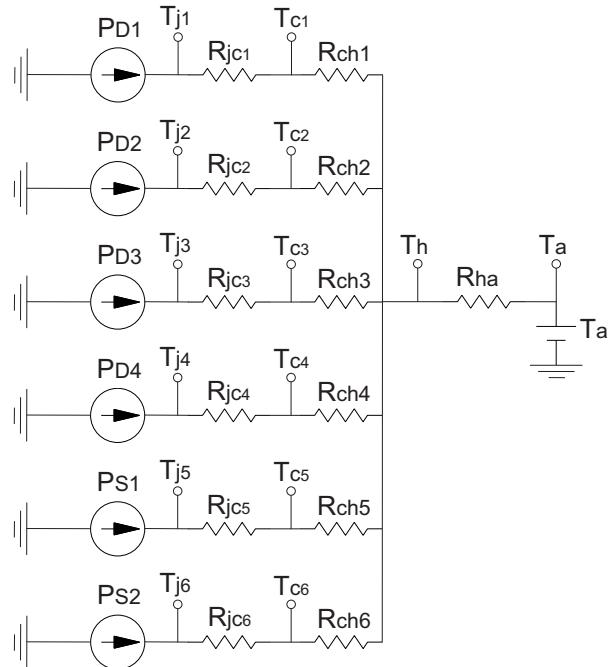

| Figura 51 – Modelo térmico . . . . .                                                                                                                                                      | 131 |

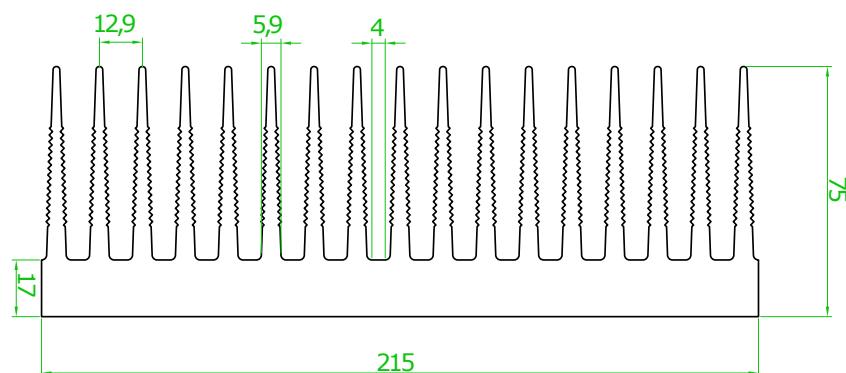

| Figura 52 – Imagem Ilustrativa do Dissipador HS 21575 . . . . .                                                                                                                           | 133 |

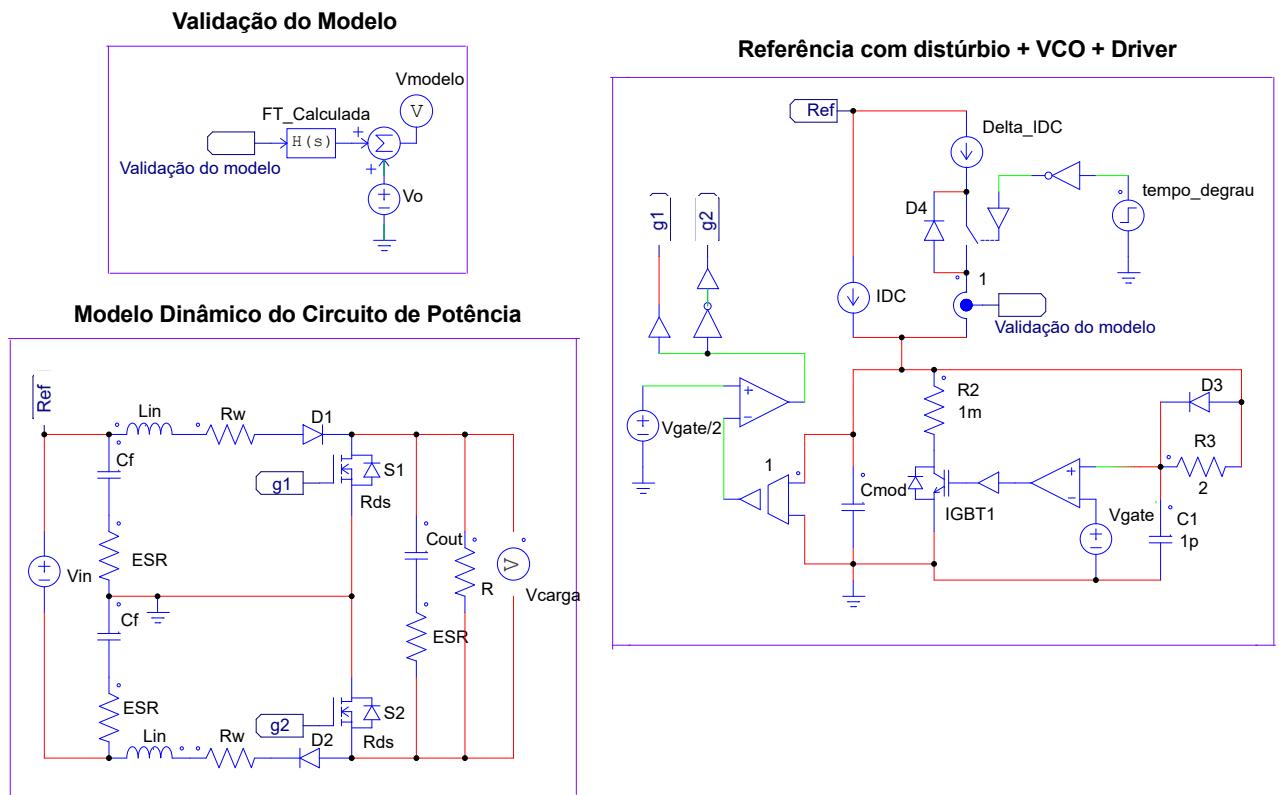

| Figura 53 – Sistema simulado no PSIM para obter e validar a função de transferência                                                                                                       | 135 |

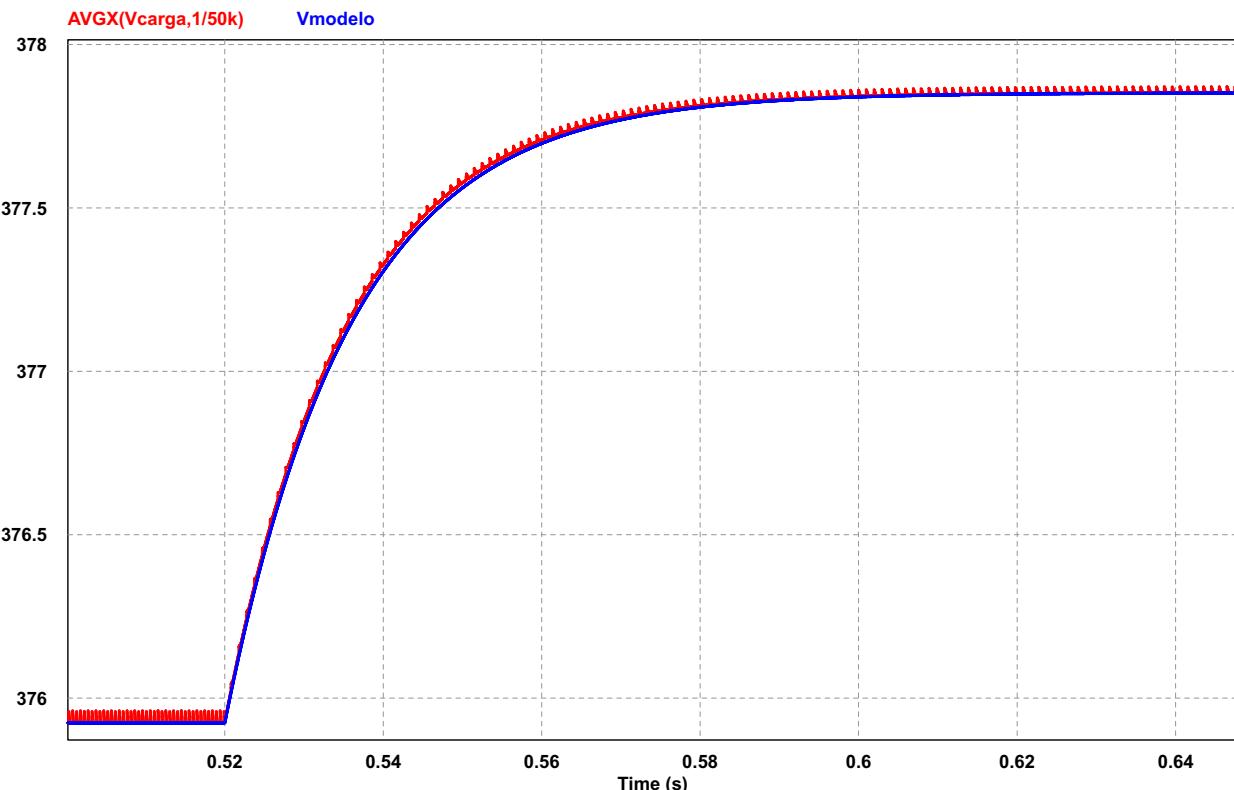

| Figura 54 – Simulação no PSIM da Resposta ao Degrau do Circuito de Potência e do Modelo Estimado. É feito a média instantânea da tensão $V_{carga}$ para facilitar a comparação . . . . . | 136 |

| Figura 55 – Principais Topologias de Amplificadores Operacionais . . . . .                                                                                                                | 137 |

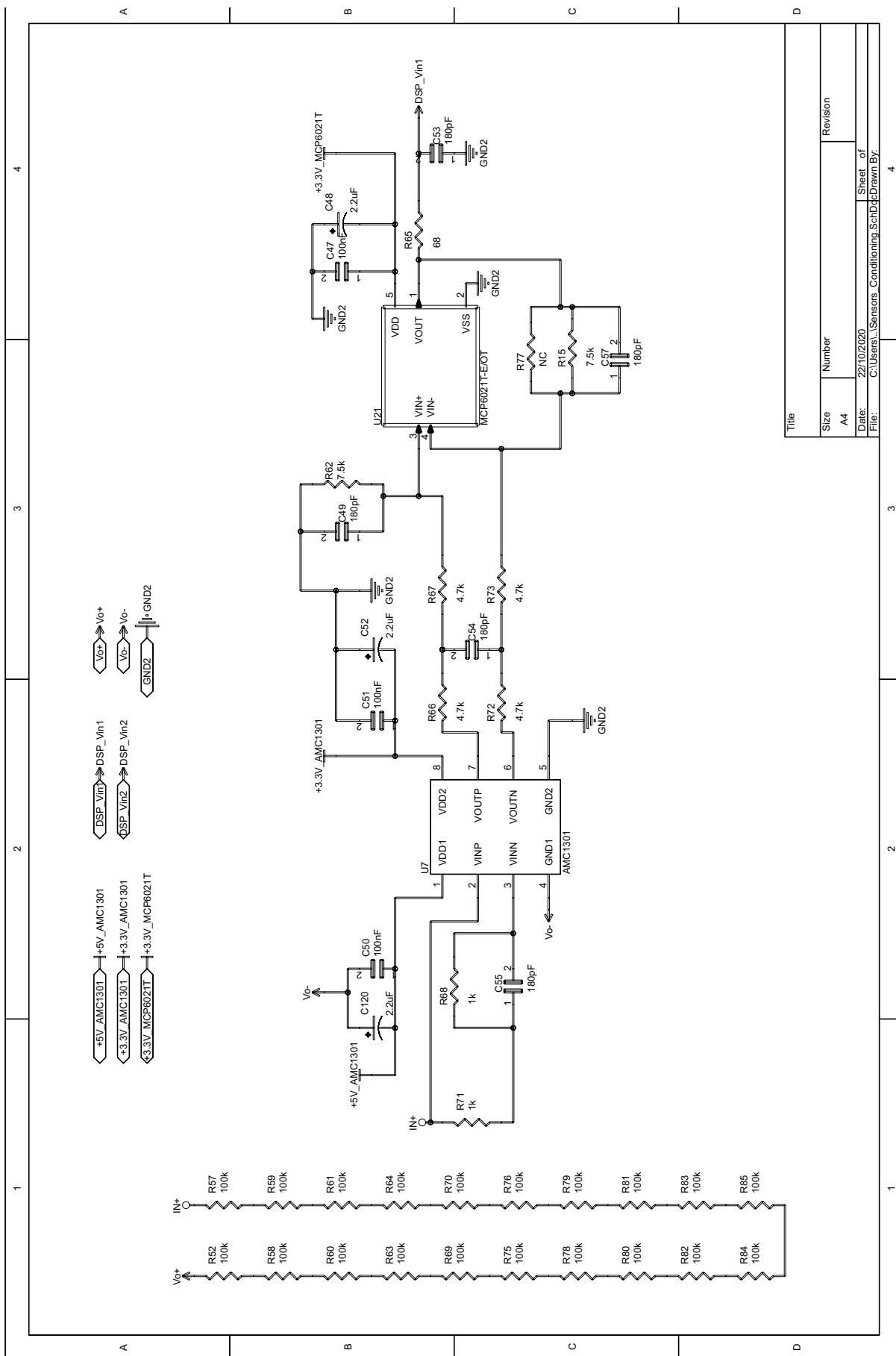

| Figura 56 – Circuito de Condicionamento de Sinal . . . . .                                                                                                                                | 139 |

| Figura 57 – Circuito de <i>Driver</i> para um Interruptor . . . . .                                                                                                                       | 140 |

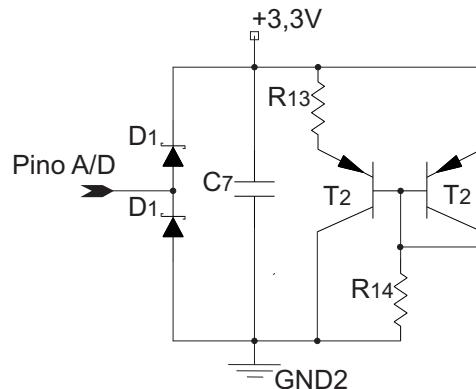

| Figura 58 – Circuito de Proteção das Entradas A/D . . . . .                                                                                                                               | 142 |

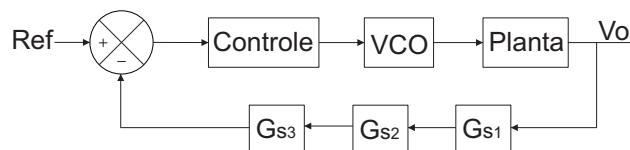

| Figura 59 – Diagrama de Blocos do Sistema de Controle . . . . .                                                                                                                           | 142 |

| Figura 60 – Diagrama de Blocos do Sistema de Controle . . . . .                                                                                                                           | 143 |

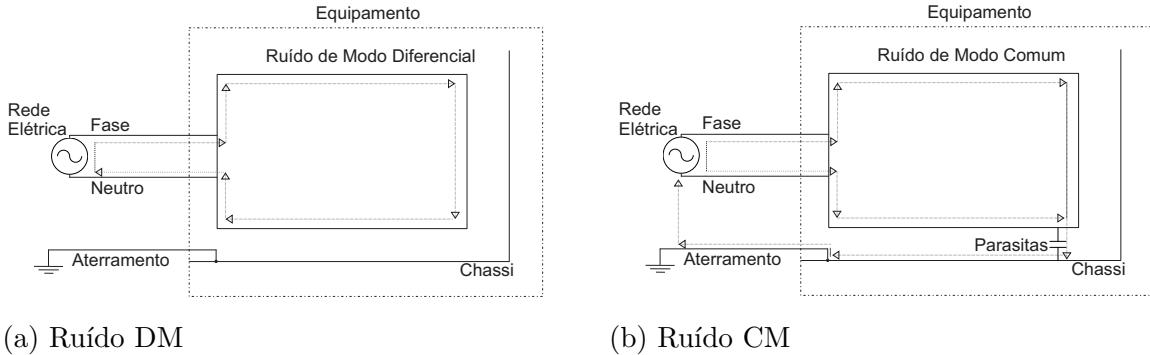

| Figura 61 – Tipos de ruídos de EMI conduzidos . . . . .                                                                                                                                   | 145 |

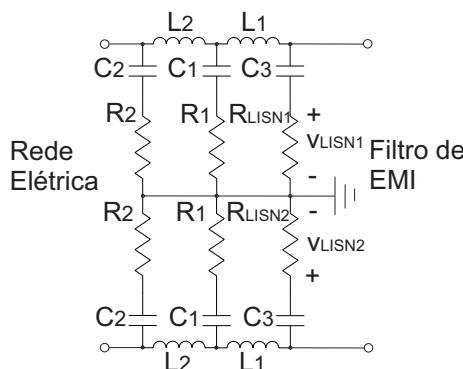

| Figura 62 – Circuito de Medição de EMI . . . . .                                                                                                                                          | 146 |

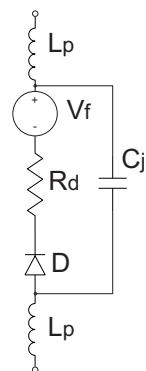

| Figura 63 – Modelo de alta frequência do diodo . . . . .                                                                                                                                  | 147 |

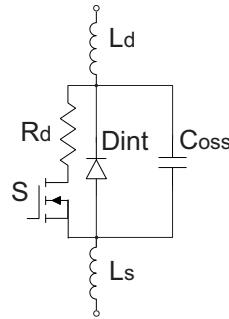

| Figura 64 – Modelo de alta frequência do mosfet . . . . .                                                                                                                                 | 148 |

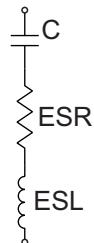

| Figura 65 – Modelo de alta frequência do capacitor . . . . .                                                                                                                              | 149 |

| Figura 66 – Modelo de alta frequência do indutor de único enrolamento . . . . .                                                                                                           | 149 |

| Figura 67 – Modelo de alta frequência do indutor de único enrolamento . . . . .                                                                                                           | 150 |

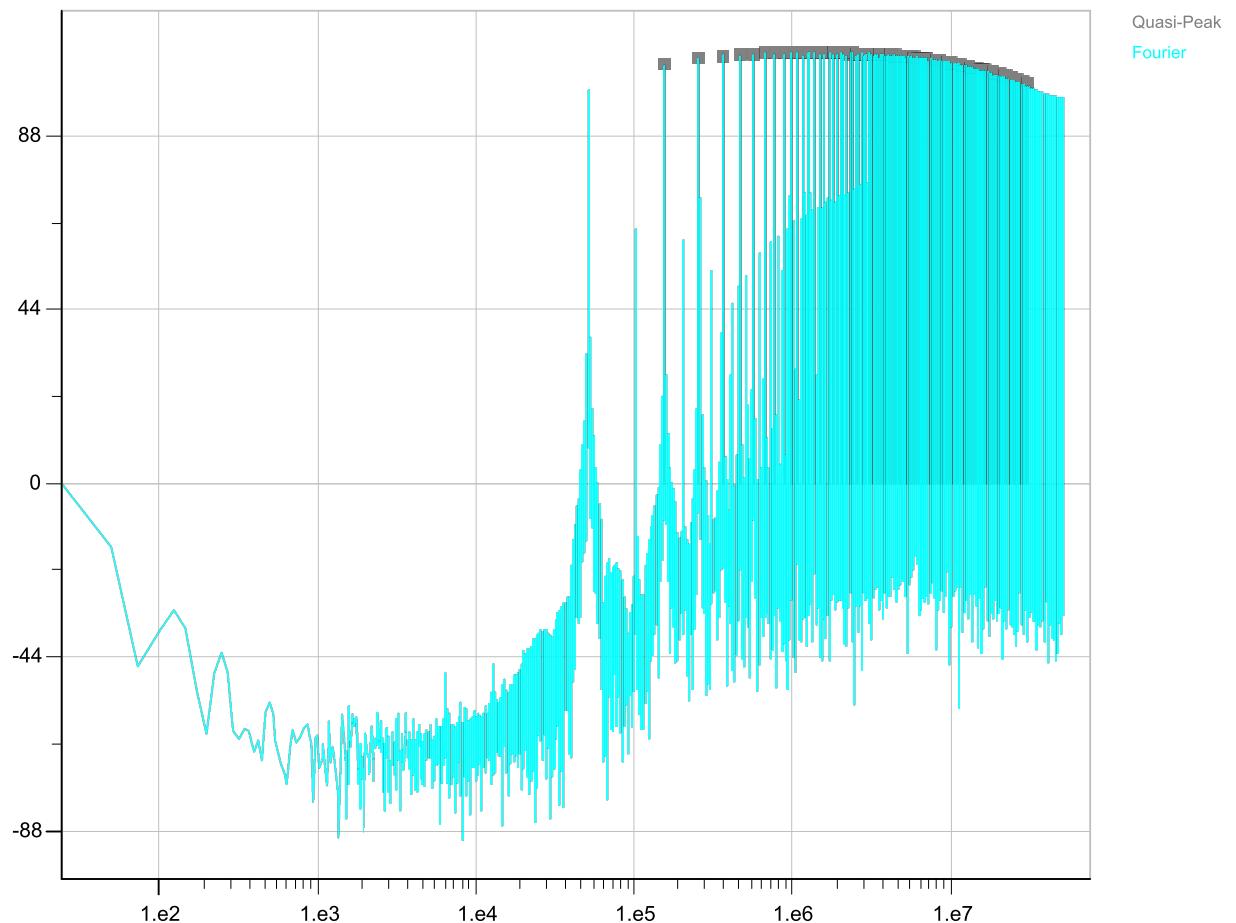

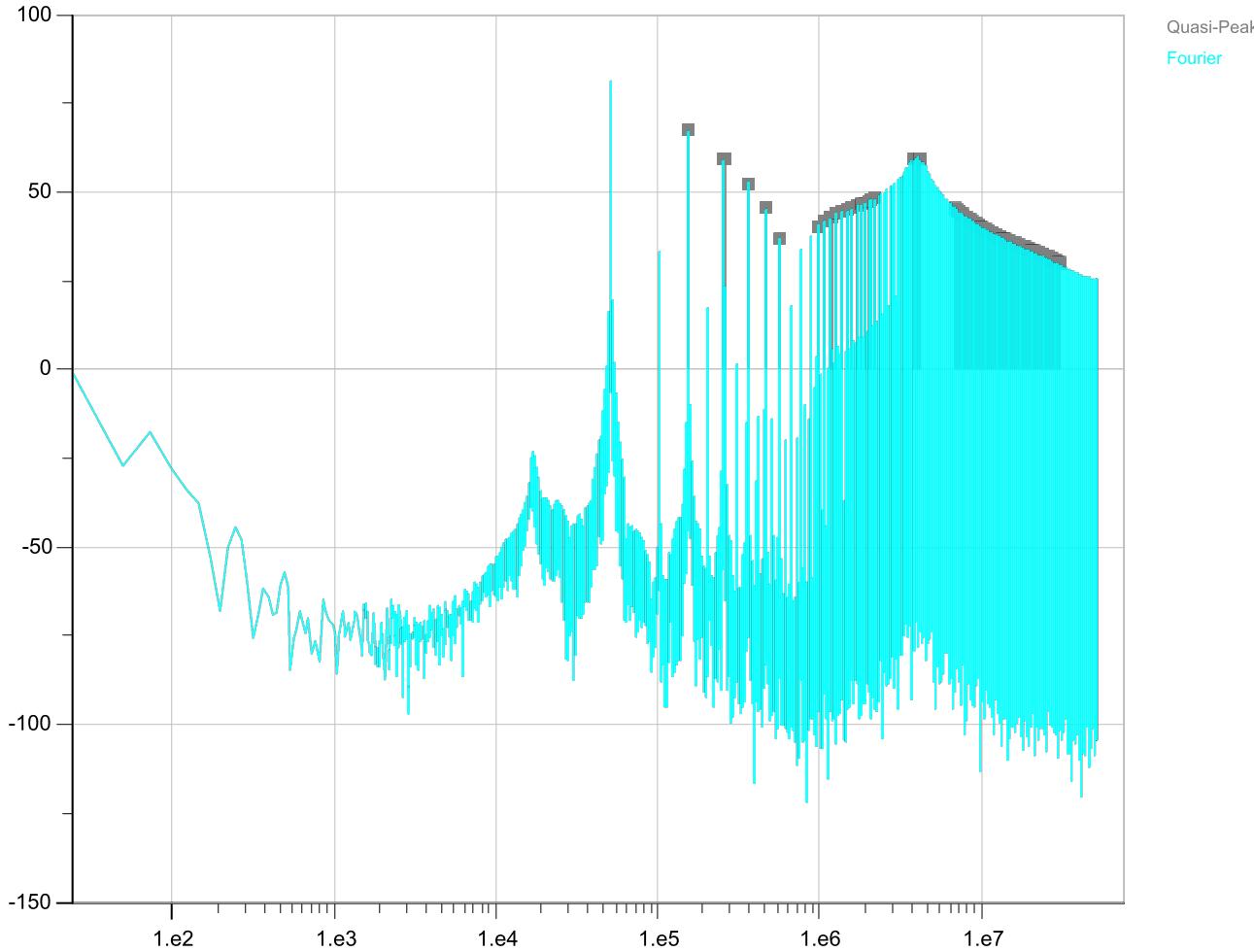

| Figura 68 – Ruído DM simulado nos Terminais de Entrada . . . . .                                                                                                                          | 151 |

|                                                                                                      |     |

|------------------------------------------------------------------------------------------------------|-----|

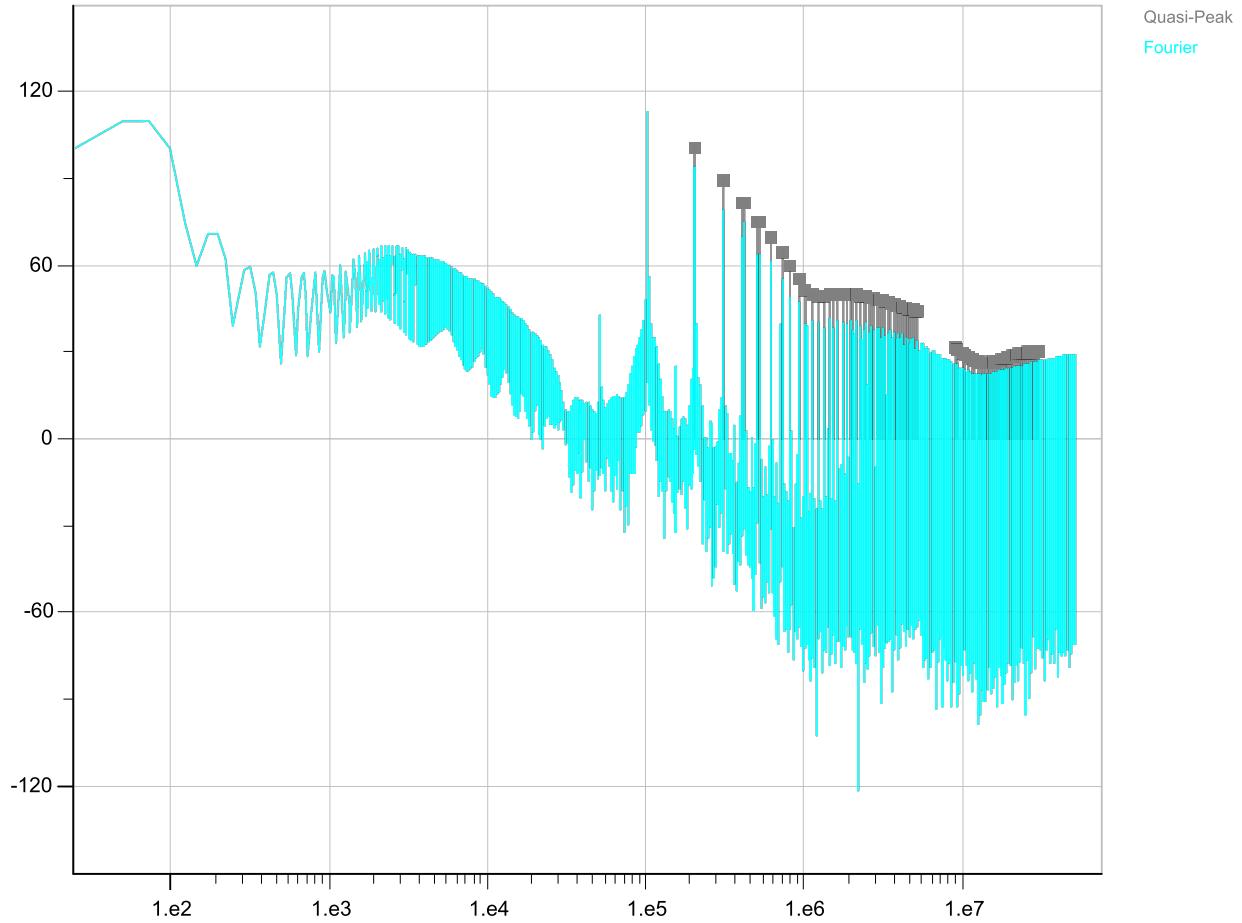

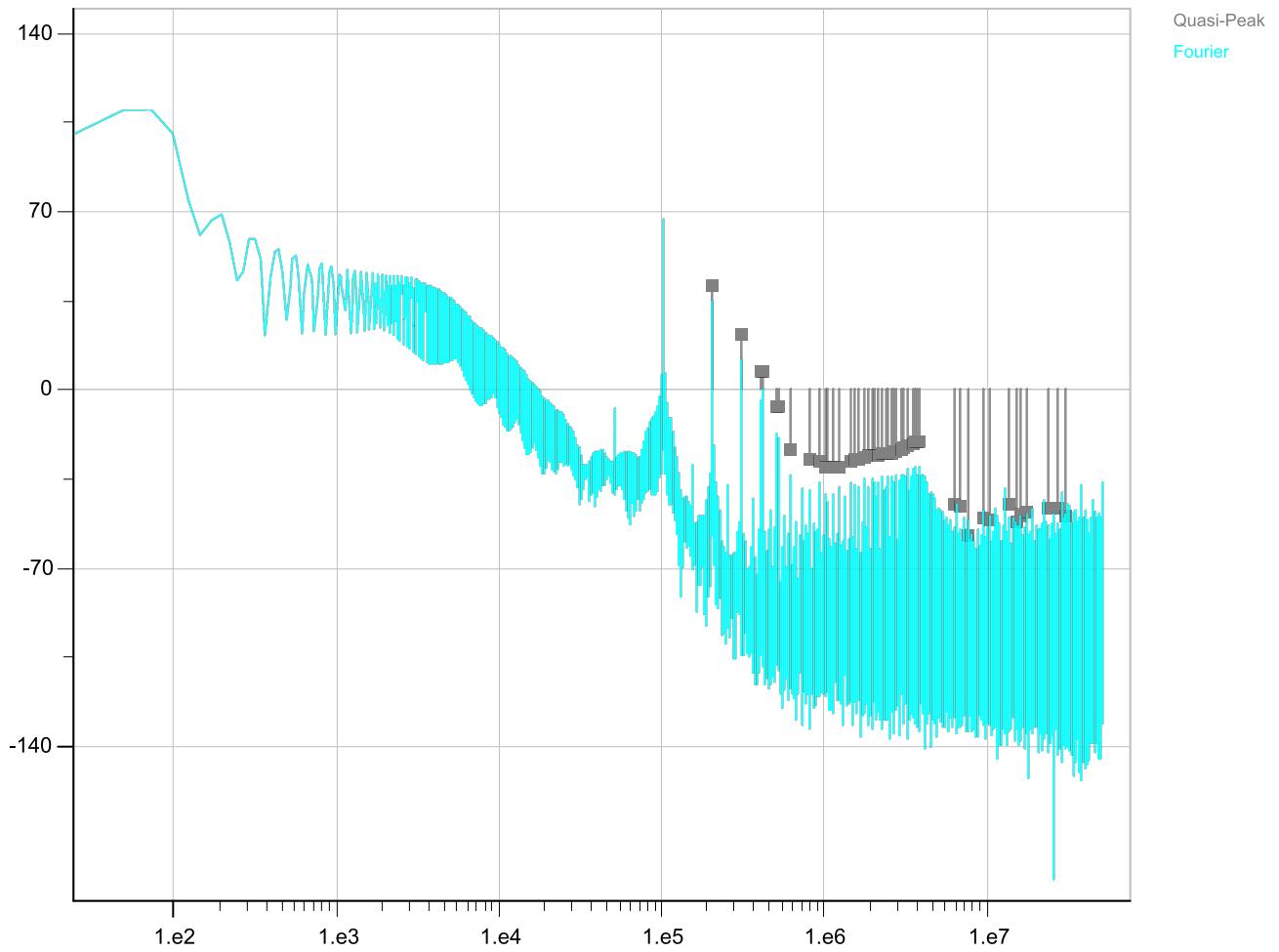

| Figura 69 – Ruído CM simulado nos Terminais de Entrada . . . . .                                     | 152 |

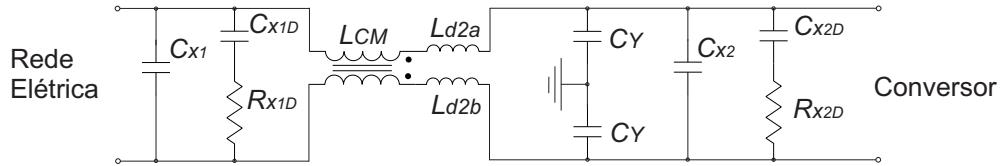

| Figura 70 – Filtro de EMI com dois estágios de modo diferencial e um estágio de modo comum . . . . . | 153 |

| Figura 71 – Filtro de EMI com dois estágios de modo diferencial e um estágio de modo comum . . . . . | 157 |

| Figura 72 – Filtro de EMI com dois estágios de modo diferencial e um estágio de modo comum . . . . . | 158 |

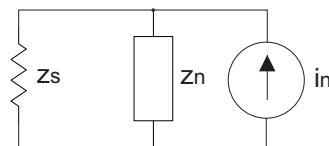

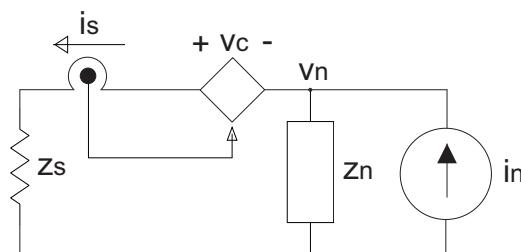

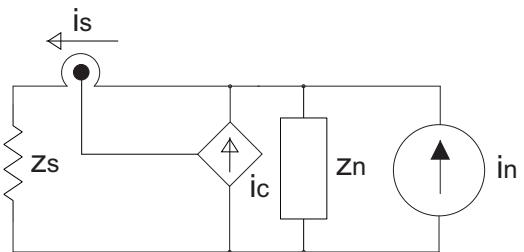

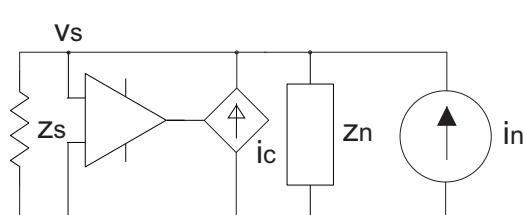

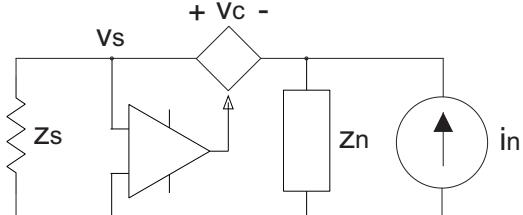

| Figura 73 – Circuito Equivalente de Alta Frequência de Conversores AC-CC . . . . .                   | 158 |

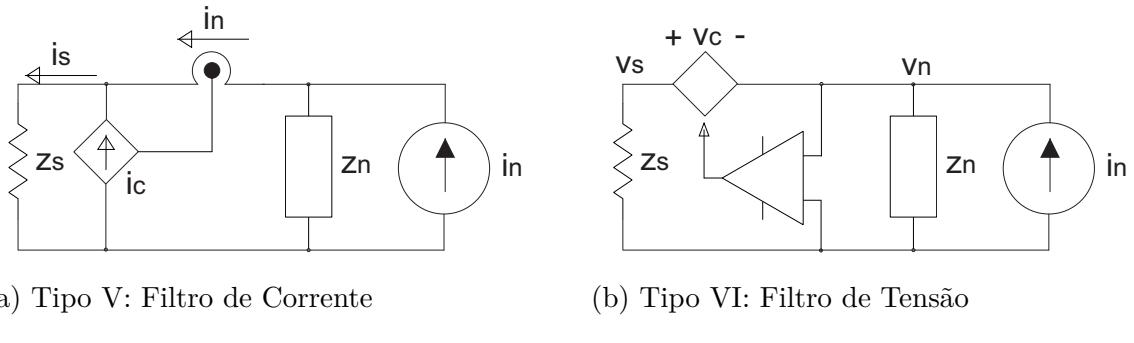

| Figura 74 – Tipos de Correção para topologias <i>feedback</i> . . . . .                              | 159 |

| Figura 75 – Tipos de Correção para topologias <i>feedforward</i> . . . . .                           | 161 |

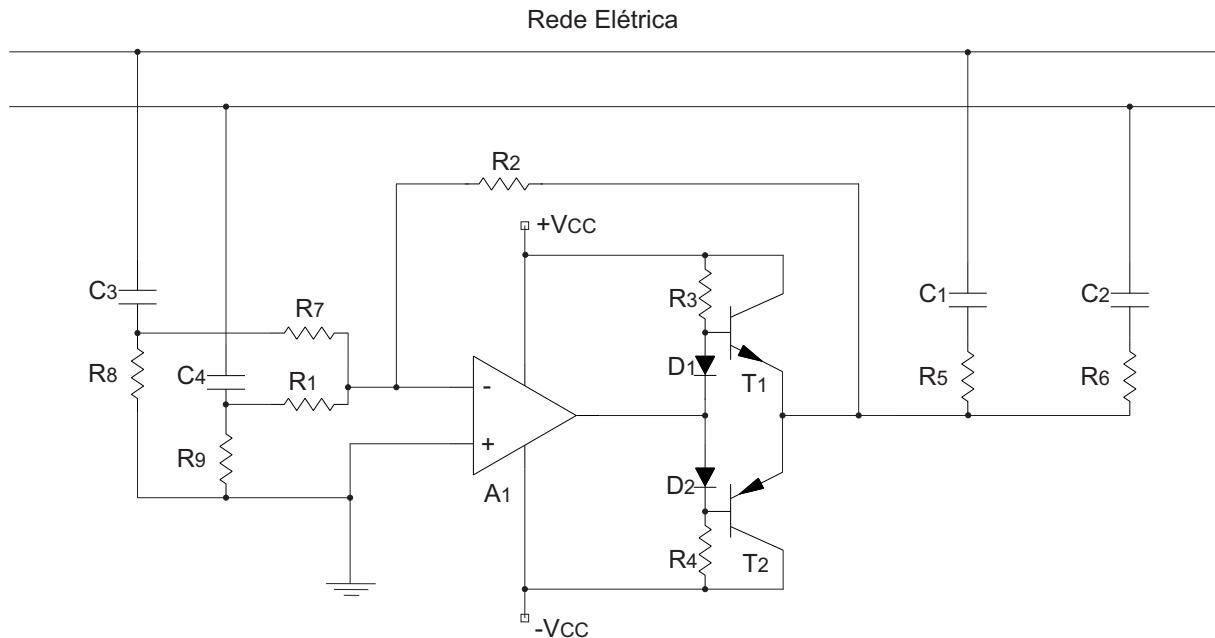

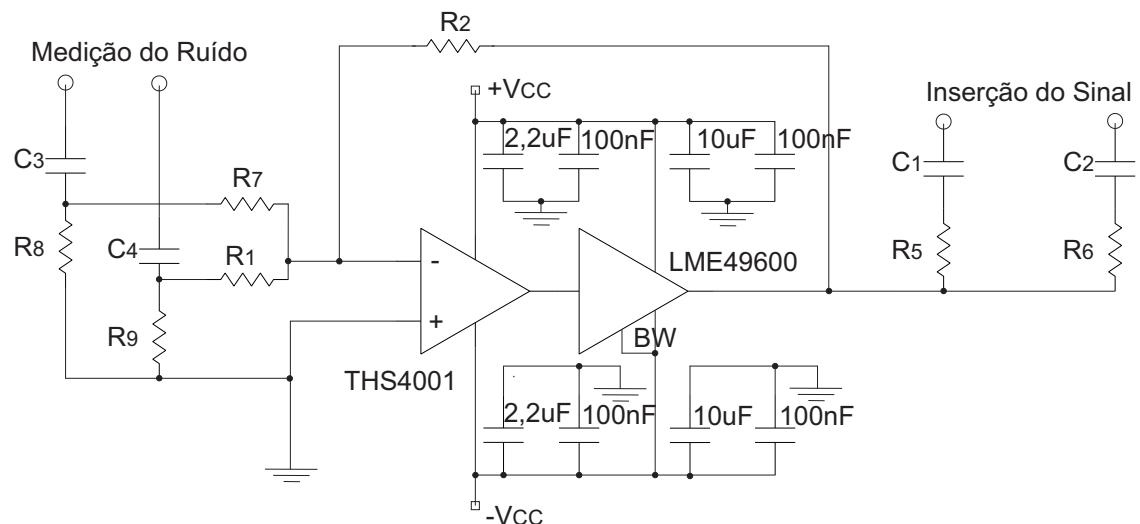

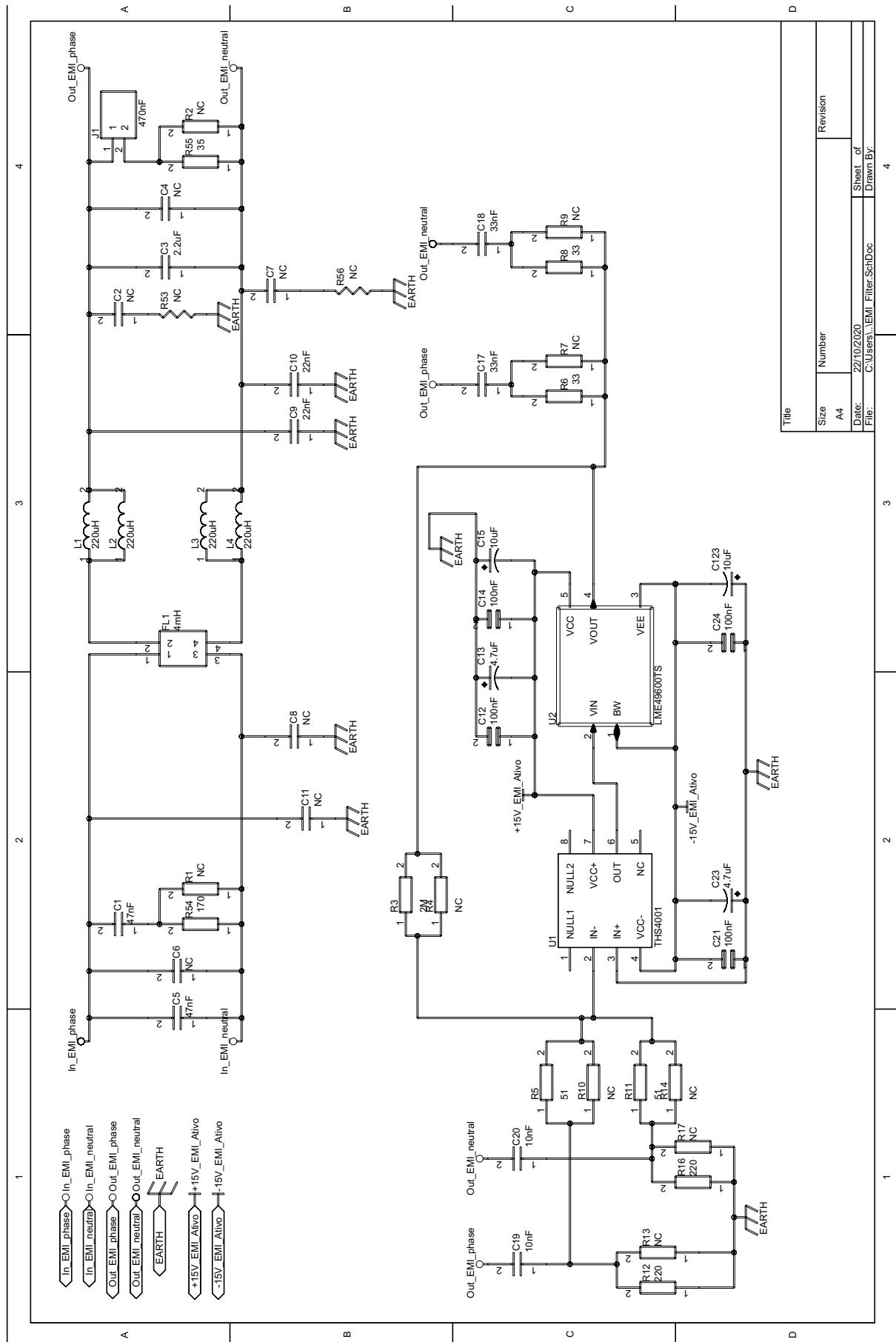

| Figura 76 – Circuito Genérico do Filtro Ativo <i>Feedback</i> Tipo II . . . . .                      | 164 |

| Figura 77 – Circuito do Filtro Ativo Implementado . . . . .                                          | 166 |

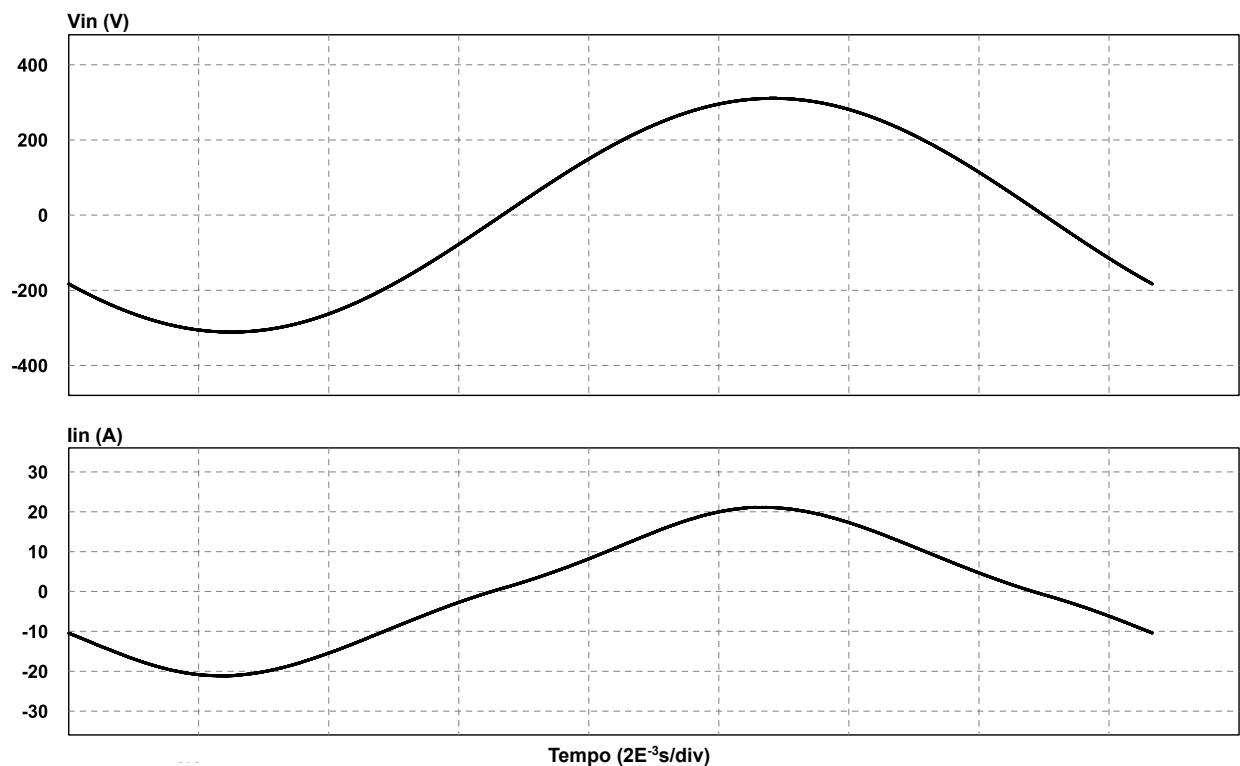

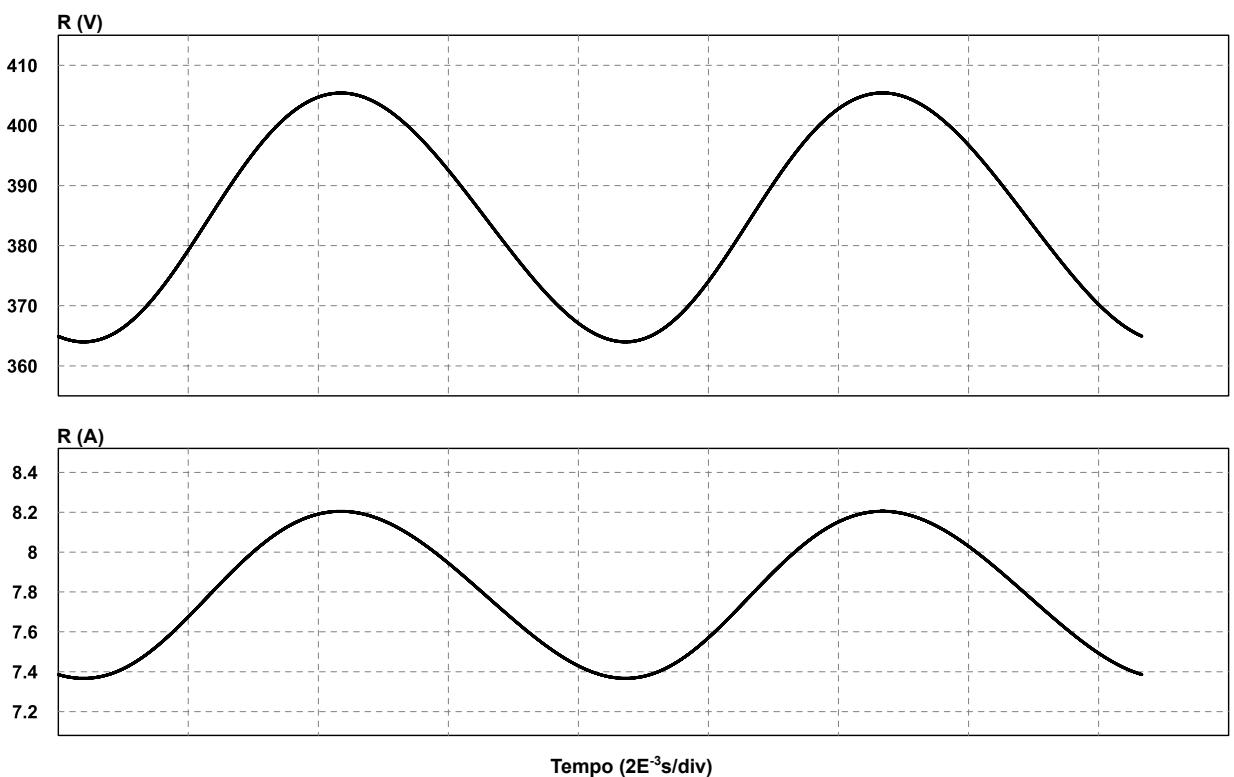

| Figura 78 – Formas de Onda Simuladas para Entrada . . . . .                                          | 168 |

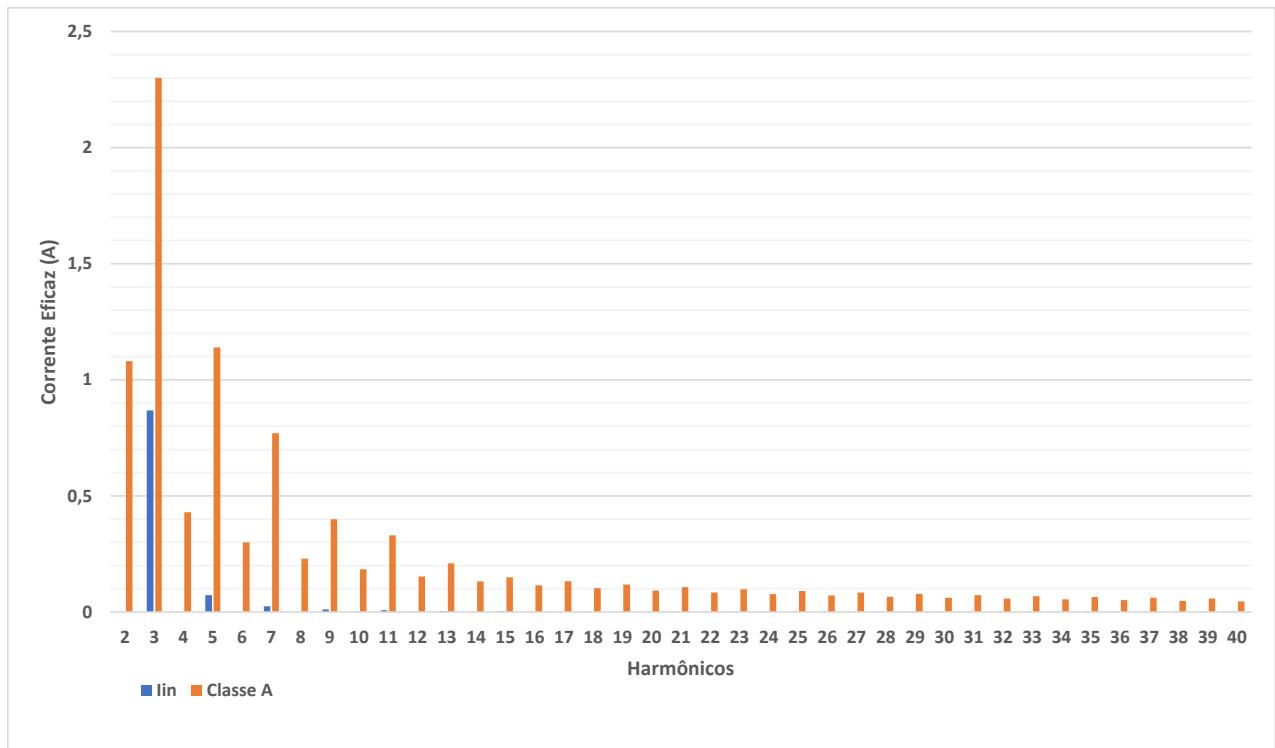

| Figura 79 – Harmônicos da Corrente de Entrada com componente fundamental de 13,72 A . . . . .        | 168 |

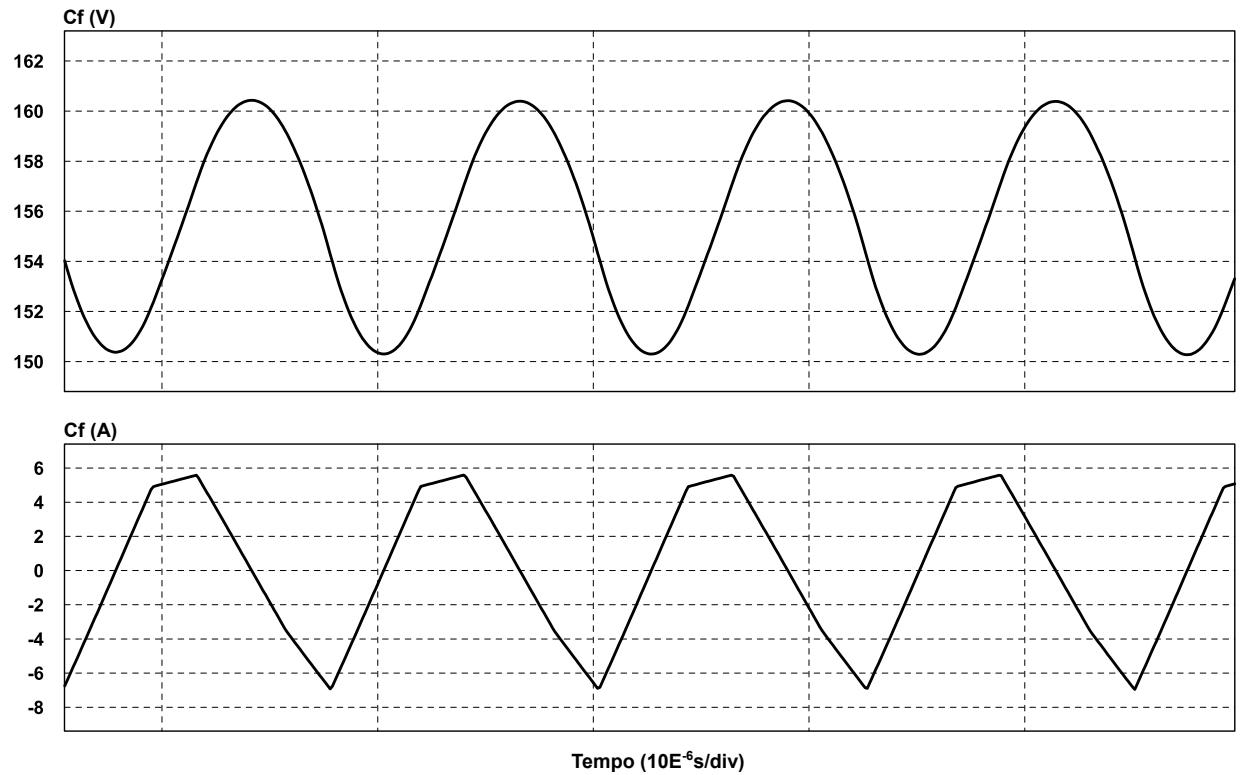

| Figura 80 – Formas de Onda Simuladas para $C_f$ . . . . .                                            | 169 |

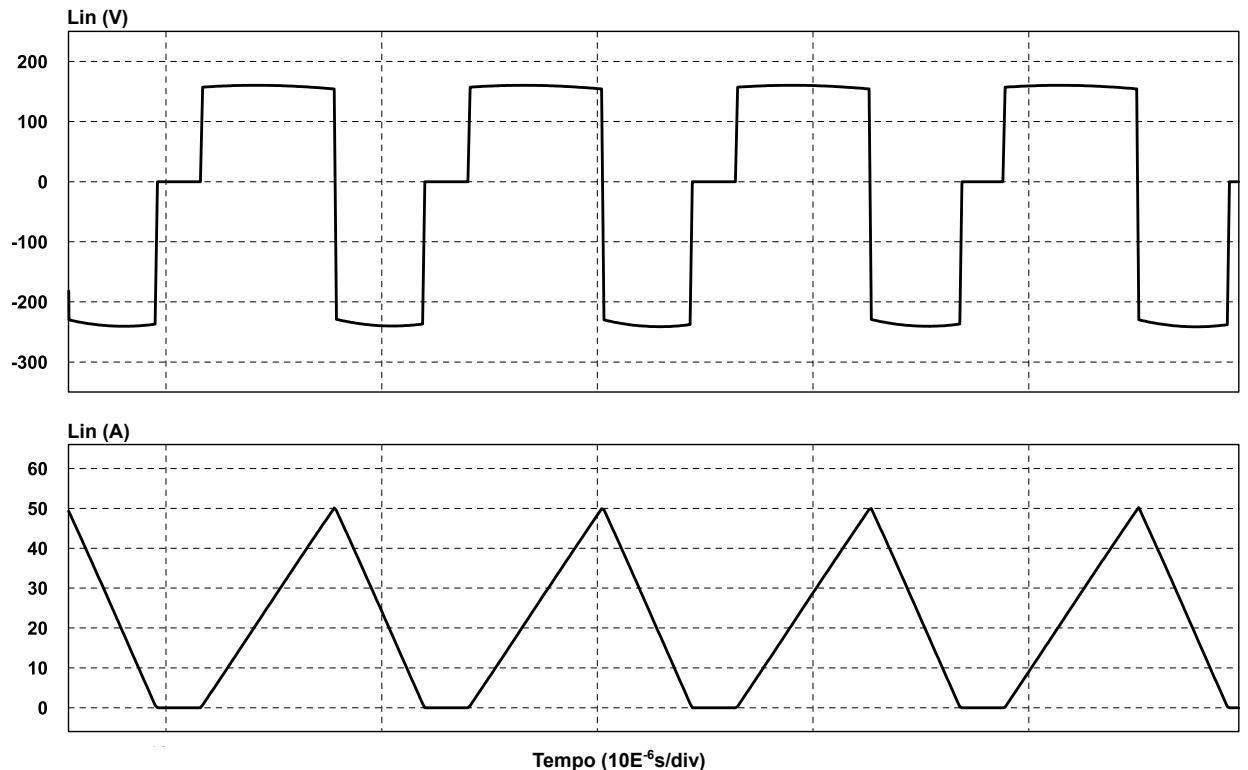

| Figura 81 – Formas de Onda Simuladas para $L_{in}$ . . . . .                                         | 169 |

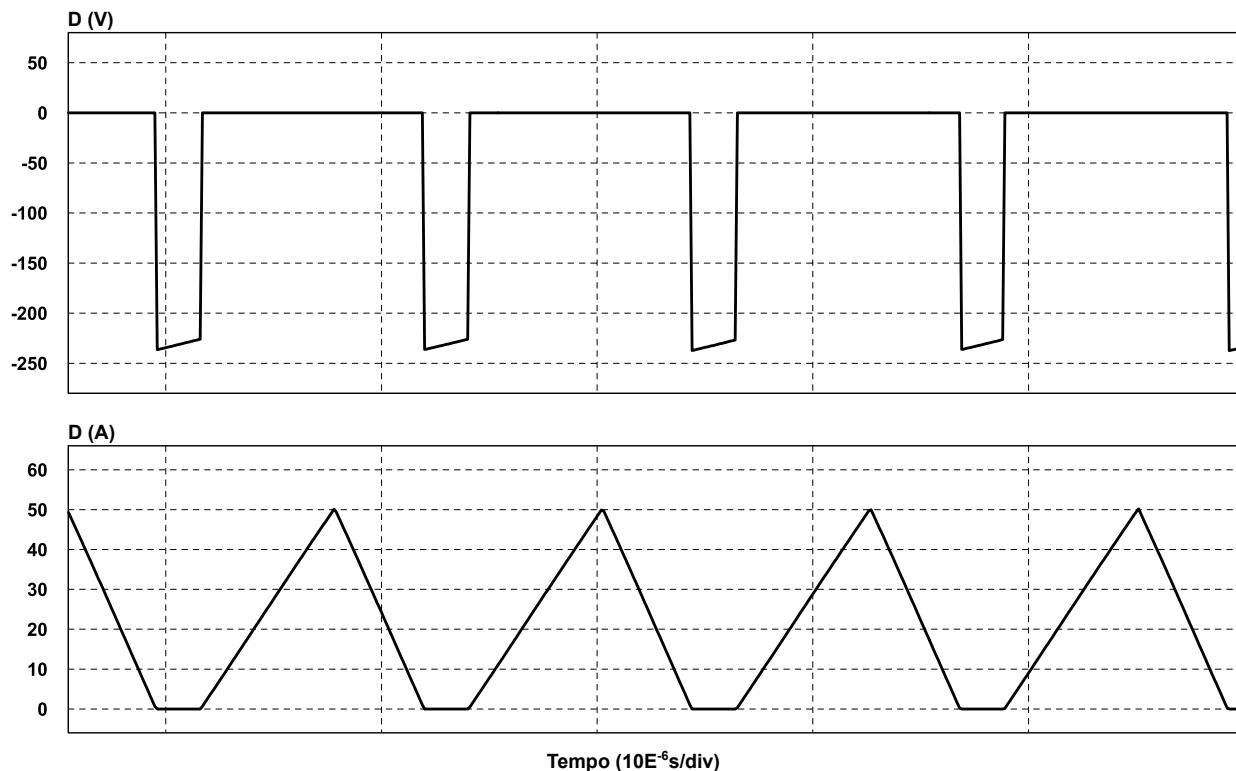

| Figura 82 – Formas de Onda Simuladas para $D$ . . . . .                                              | 170 |

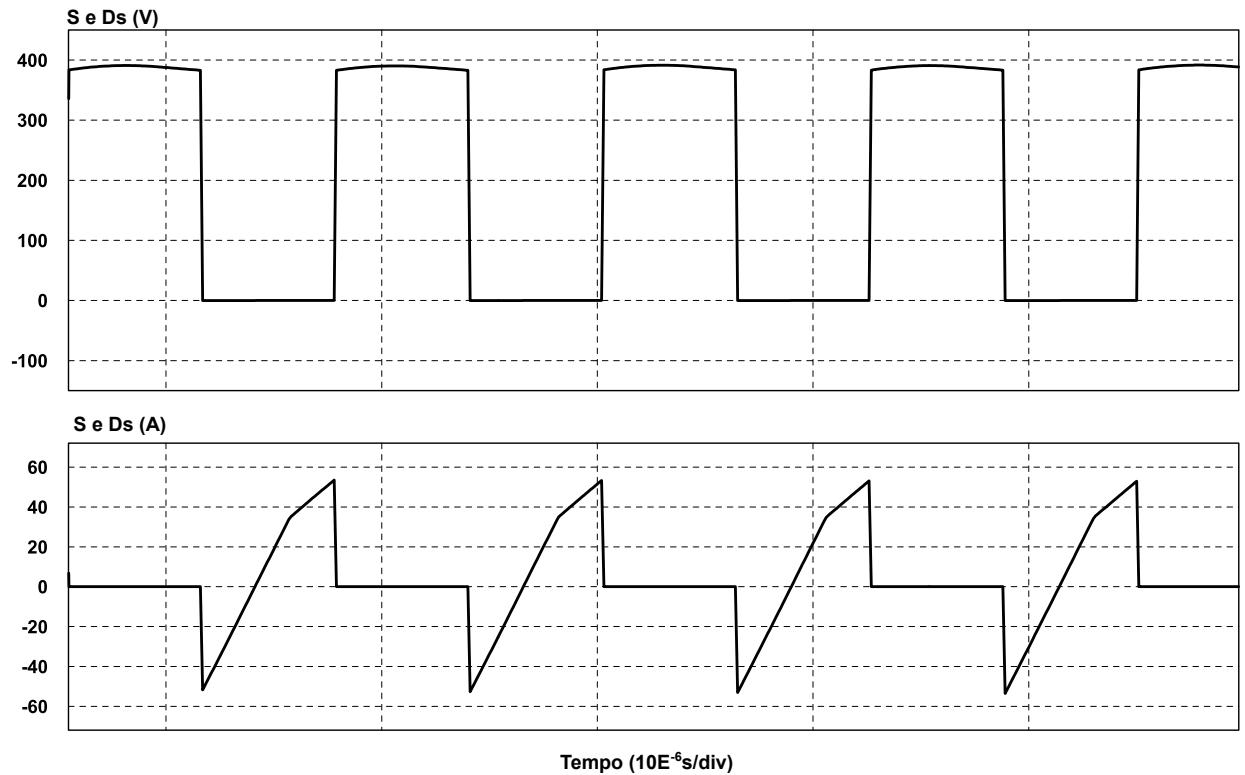

| Figura 83 – Formas de Onda Simuladas para $S$ e $D_s$ . . . . .                                      | 171 |

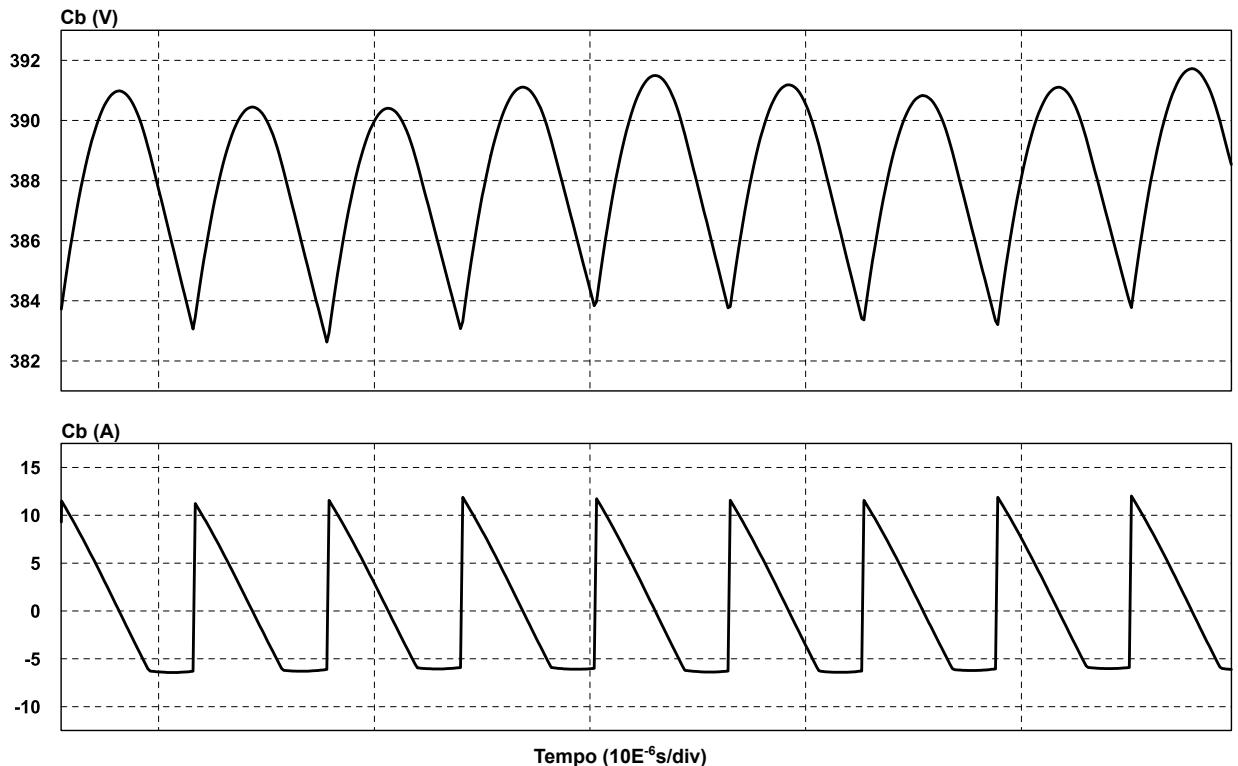

| Figura 84 – Formas de Onda Simuladas para $C_b$ . . . . .                                            | 171 |

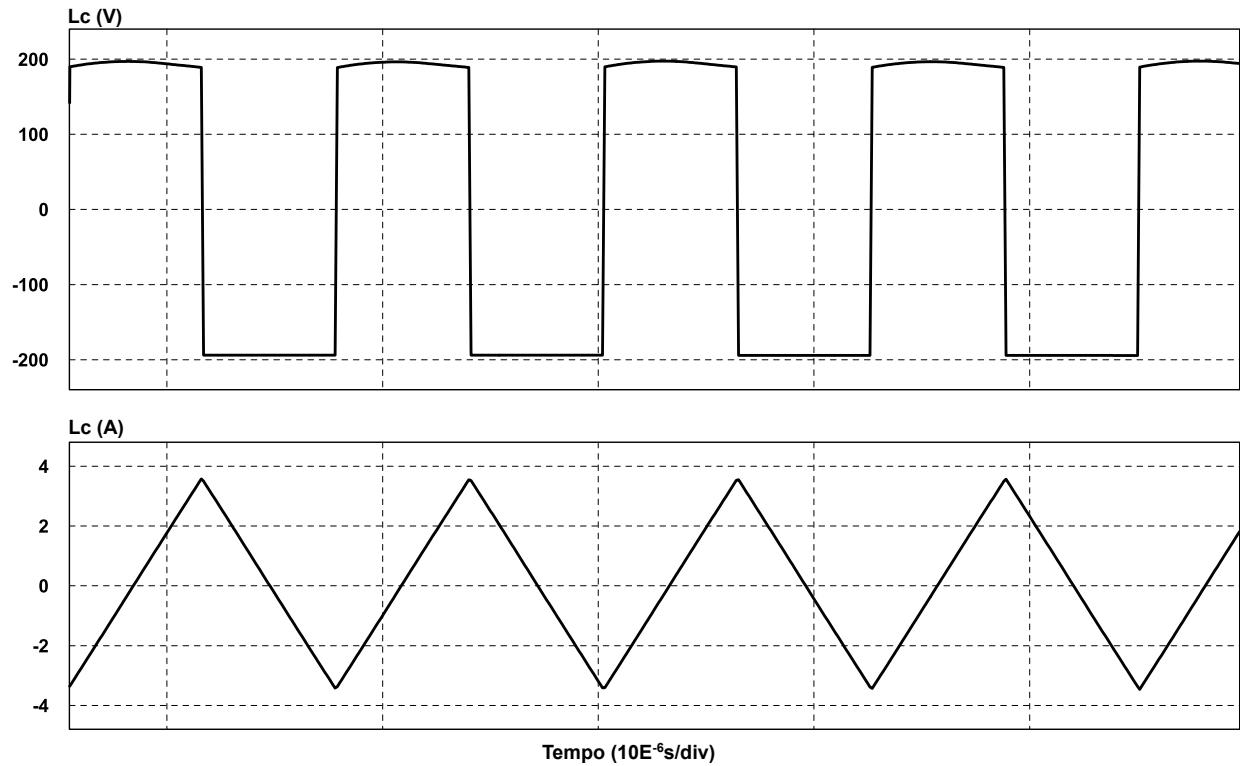

| Figura 85 – Formas de Onda Simuladas para $L_c$ . . . . .                                            | 172 |

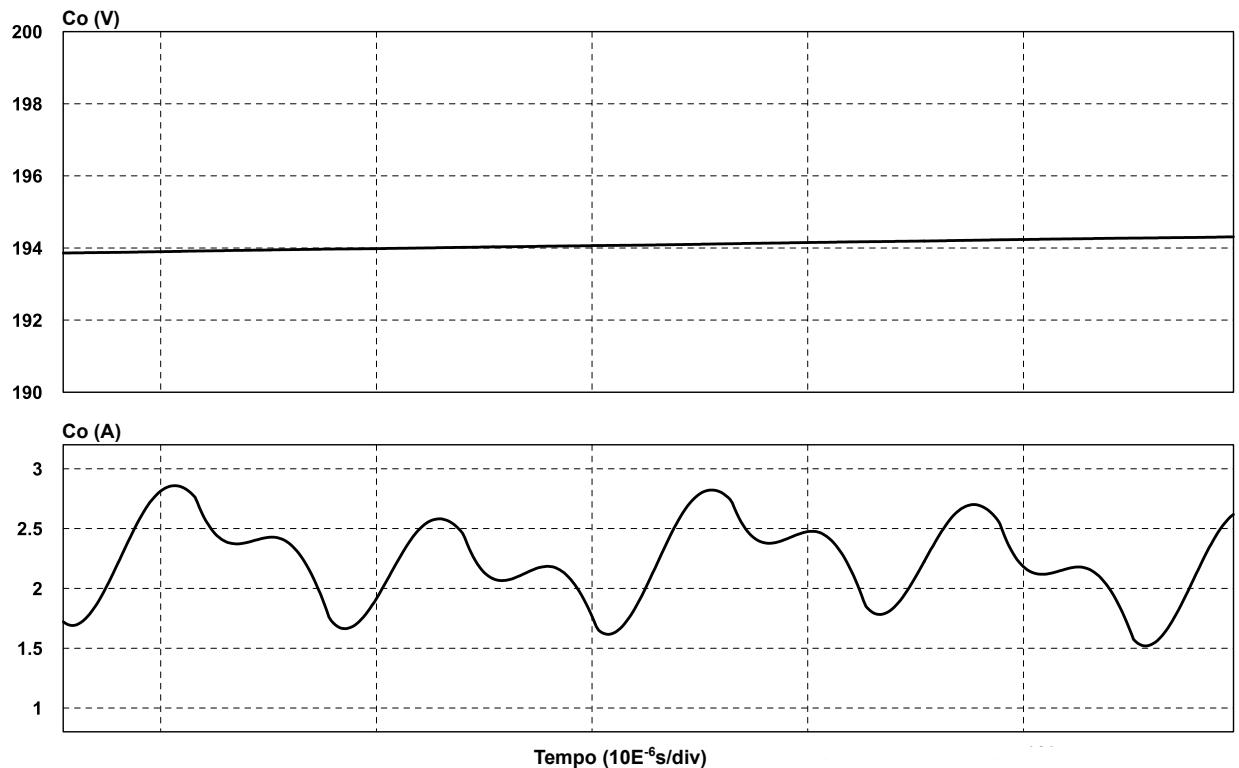

| Figura 86 – Formas de Onda Simuladas para $C_o$ . . . . .                                            | 173 |

| Figura 87 – Formas de Onda Simuladas para $R$ . . . . .                                              | 173 |

| Figura 88 – <i>Layout</i> . . . . .                                                                  | 175 |

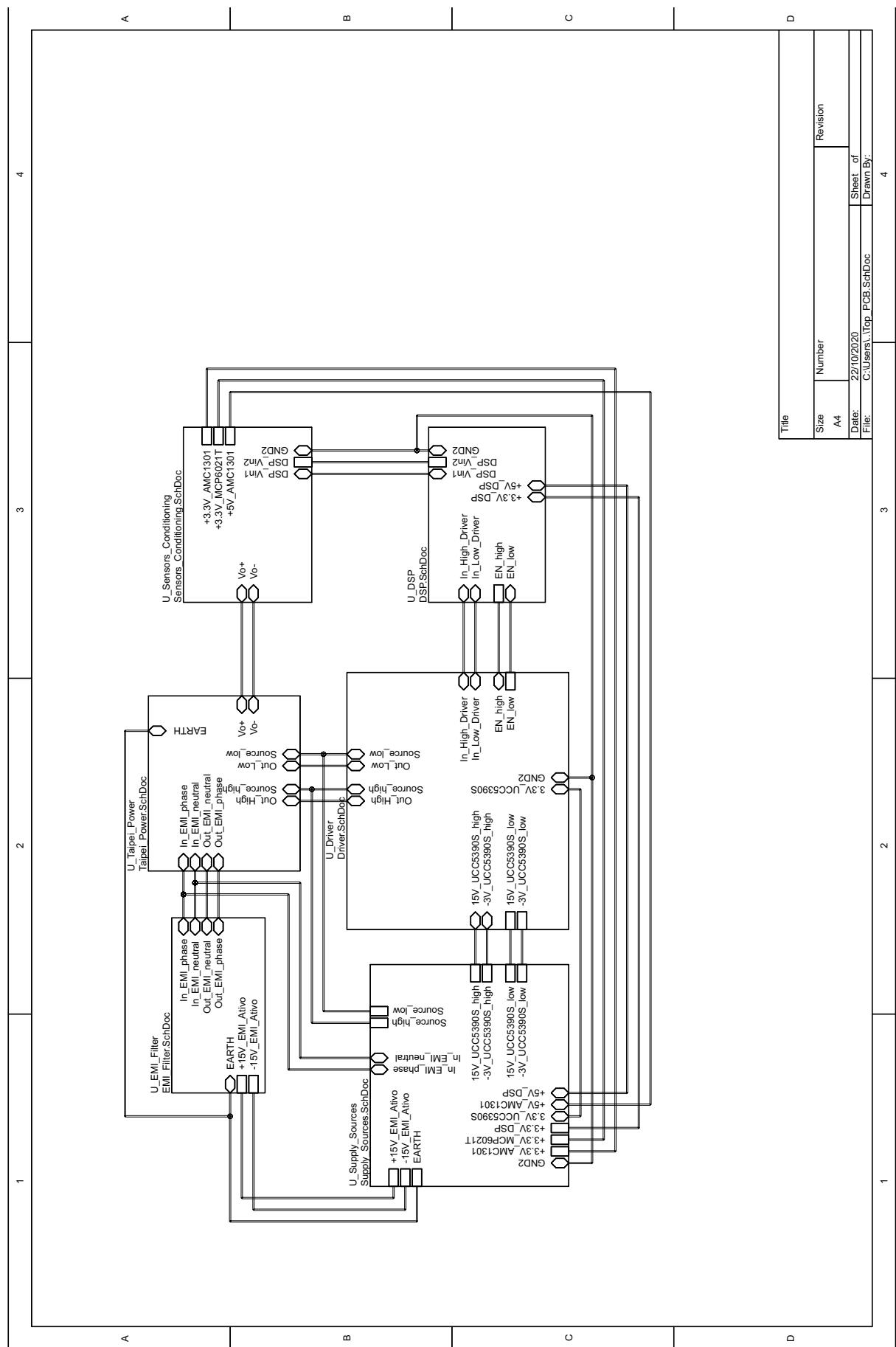

| Figura 89 – Diagrama Geral do Conversor . . . . .                                                    | 185 |

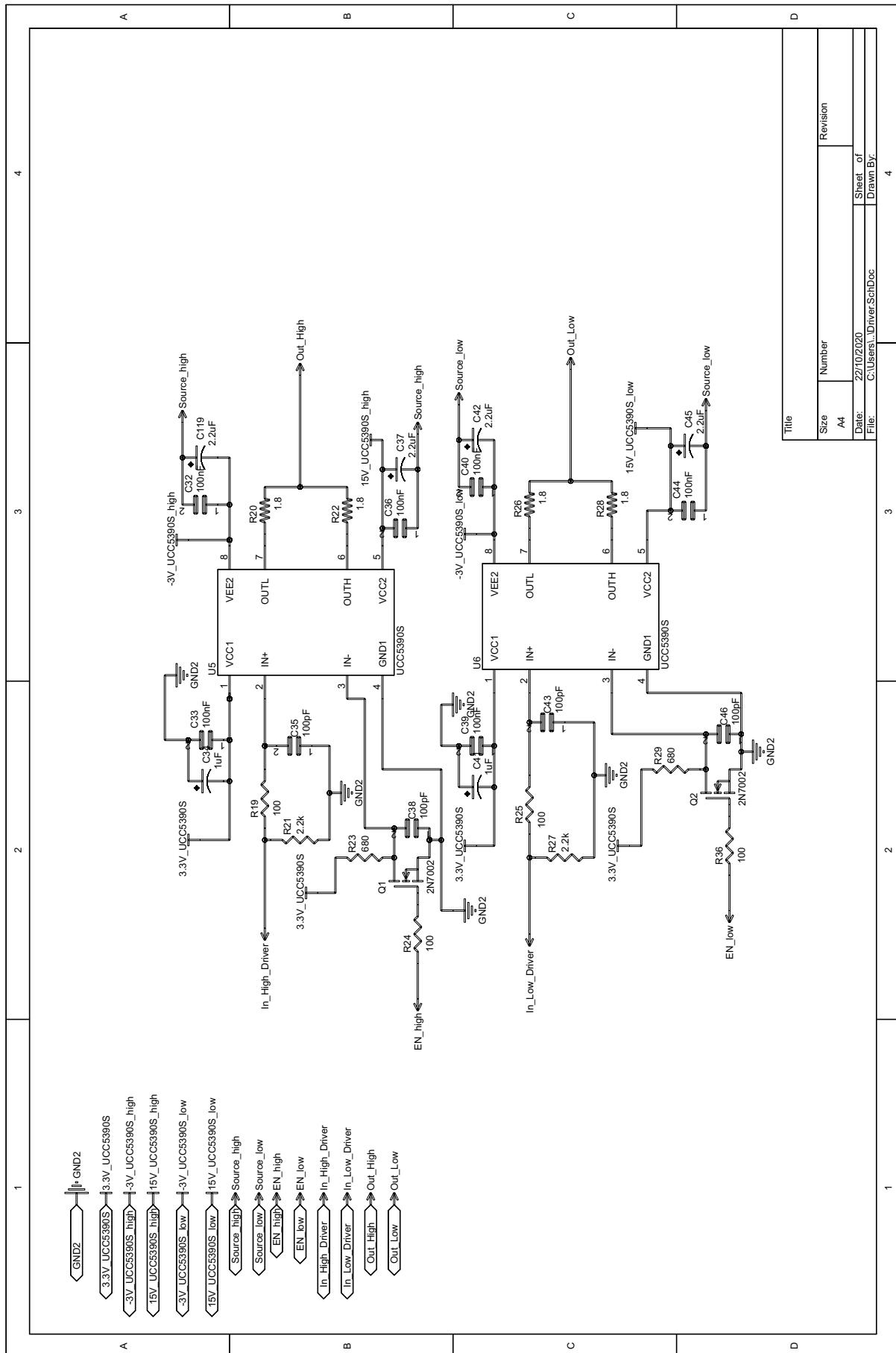

| Figura 90 – Circuito de <i>Driver</i> . . . . .                                                      | 186 |

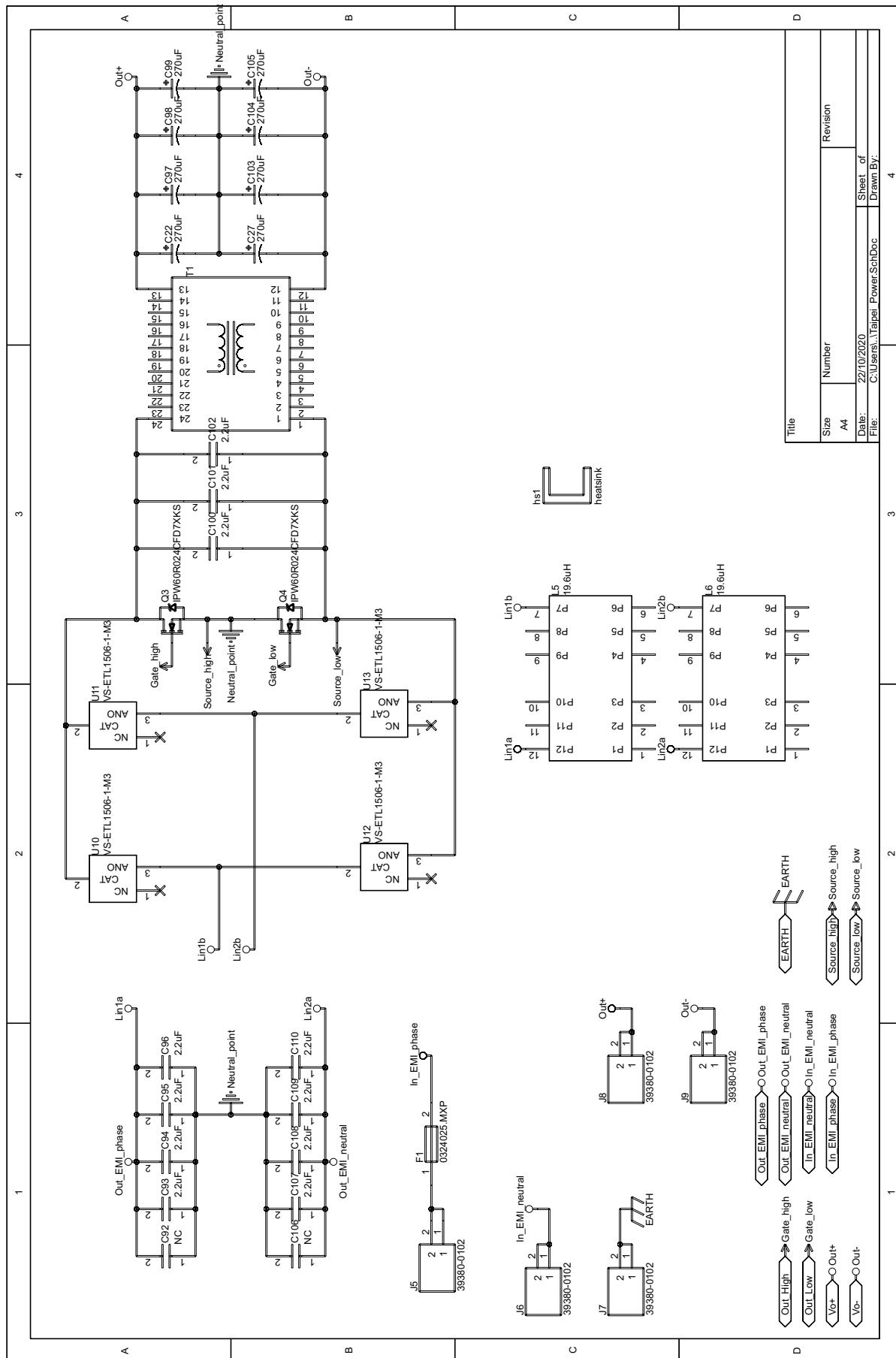

| Figura 91 – Circuito de Potência . . . . .                                                           | 187 |

| Figura 92 – Circuito de Condicionamento de Sinal . . . . .                                           | 188 |

| Figura 93 – Circuito do Filtro de EMI Passivo e Ativo . . . . .                                      | 189 |

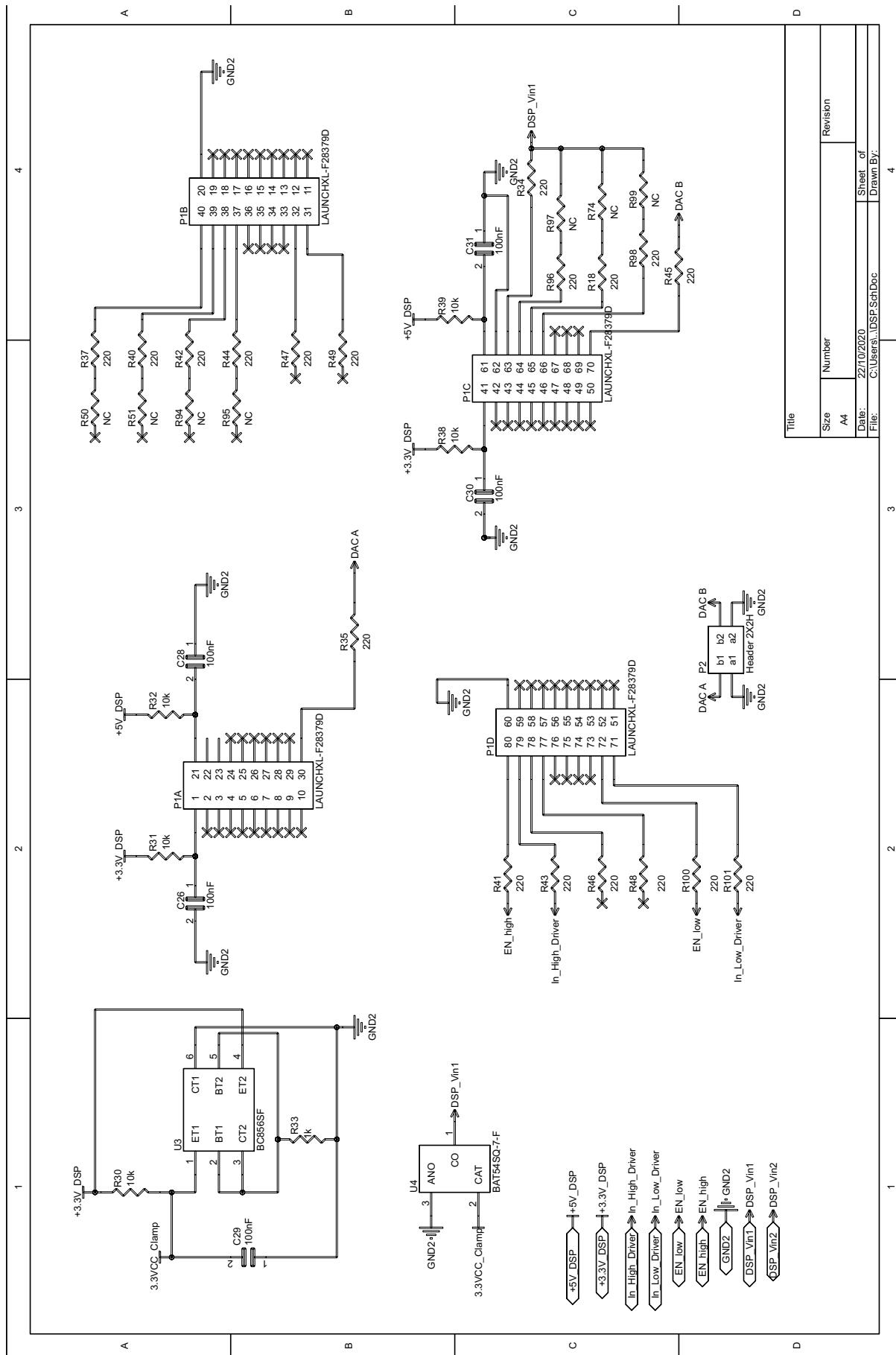

| Figura 94 – Interface com o DSP . . . . .                                                            | 190 |

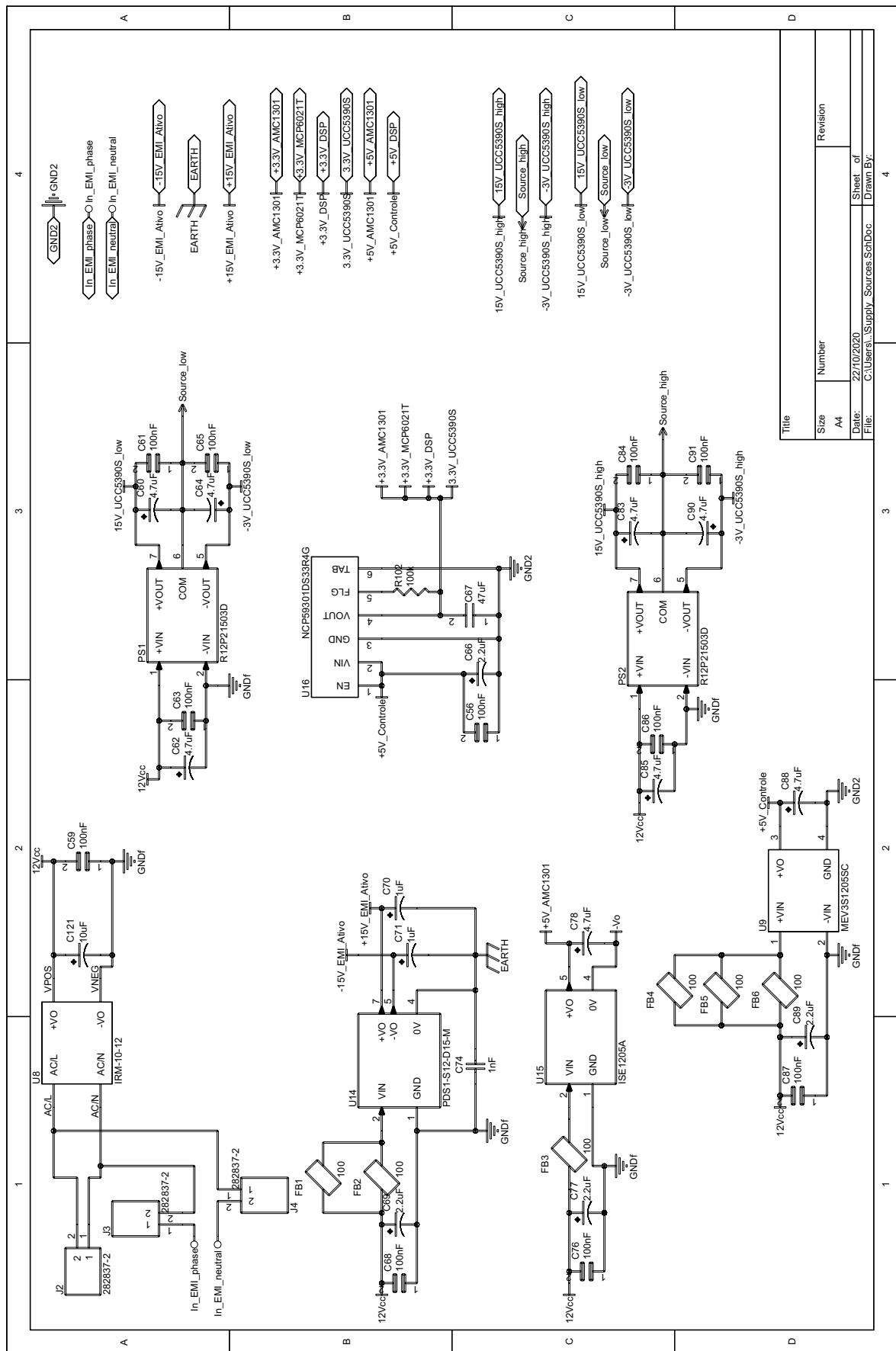

| Figura 95 – Fontes Auxiliares . . . . .                                                              | 191 |

## LISTA DE TABELAS

|                                                                                                                   |     |

|-------------------------------------------------------------------------------------------------------------------|-----|

| Tabela 1 – Parâmetros de Projeto . . . . .                                                                        | 43  |

| Tabela 2 – Comparação das Características das Topologias, Desconsiderando Filtro de EMI . . . . .                 | 48  |

| Tabela 3 – Corrente nos Indutores Boost ao longo das etapas de operação . . . . .                                 | 59  |

| Tabela 4 – Corrente nos Indutores Boost Reescritas ao longo das etapas de operação                                | 59  |

| Tabela 5 – Parâmetros de Projeto . . . . .                                                                        | 81  |

| Tabela 6 – Novos Parâmetros de Projeto . . . . .                                                                  | 87  |

| Tabela 7 – Resultados do projeto do indutor $L_{in}$ . . . . .                                                    | 99  |

| Tabela 8 – Resultados do projeto do indutor $L_c$ . . . . .                                                       | 100 |

| Tabela 9 – Resultados da escolha do diodo da ponte retificadora . . . . .                                         | 104 |

| Tabela 10 – Resultados da escolha do MOSFET . . . . .                                                             | 109 |

| Tabela 11 – Resultados da escolha de $C_f$ . . . . .                                                              | 115 |

| Tabela 12 – Resultados da escolha de $C_b$ . . . . .                                                              | 116 |

| Tabela 13 – Resultados da escolha do Capacitor $C_o$ . . . . .                                                    | 117 |

| Tabela 14 – Divisão em Percentual de Perdas para Carga Nominal por Tipo de Componente . . . . .                   | 118 |

| Tabela 15 – Volume de Componentes Passivos e seus Materiais . . . . .                                             | 118 |

| Tabela 16 – Parâmetros de projeto do conversor BCCM . . . . .                                                     | 121 |

| Tabela 17 – Diodos de Retificação da topologia SPT <i>versus</i> BCCM . . . . .                                   | 122 |

| Tabela 18 – Interruptores do SPT <i>versus</i> BCCM . . . . .                                                     | 123 |

| Tabela 19 – Diodos Boost do SPT <i>versus</i> BCCM . . . . .                                                      | 125 |

| Tabela 20 – Indutor Boost do SPT <i>versus</i> BCCM . . . . .                                                     | 126 |

| Tabela 21 – Capacitor de Barramento da topologia SPT <i>versus</i> BCCM . . . . .                                 | 127 |

| Tabela 22 – capacitor de filme $C_f$ topologia SPT . . . . .                                                      | 127 |

| Tabela 23 – capacitor de filme $C_b$ topologia SPT . . . . .                                                      | 128 |

| Tabela 24 – Indutor $L_c$ do SPT <i>versus</i> BCCM . . . . .                                                     | 128 |

| Tabela 25 – Parâmetros de projeto do BCCM . . . . .                                                               | 130 |

| Tabela 26 – Parâmetros de Qualidade de Energia em Carga Nominal . . . . .                                         | 130 |

| Tabela 27 – Principais características do isolador 4170G para encapsulamento TO-220132                            |     |

| Tabela 28 – Principais características do isolador 4180G para encapsulamento TO-247132                            |     |

| Tabela 29 – Componentes do Circuito de Sensoreamento . . . . .                                                    | 139 |

| Tabela 30 – Tabela Verdade para Sinais de Gatilho no UCC5390S . . . . .                                           | 139 |

| Tabela 31 – Componentes do Circuito de <i>Driver</i> . . . . .                                                    | 141 |

| Tabela 32 – Componentes do Circuito de Proteção do A/D . . . . .                                                  | 141 |

| Tabela 33 – Limites totais de ruídos EMI conduzidos na entrada do retificador conforme a norma CISPR 14 . . . . . | 146 |

| Tabela 34 – Limite para harmônicos enquadrados na Classe A da norma IEC 61000-3-2147                              |     |

| Tabela 35 – Variáveis do modelo de alta frequência do diodo retificador . . . . .                                 | 148 |

|                                                                                    |     |

|------------------------------------------------------------------------------------|-----|

| Tabela 36 – Variáveis do modelo de alta frequência do mosfet . . . . .             | 148 |

| Tabela 37 – Variáveis do modelo de alta frequência do capacitor . . . . .          | 149 |

| Tabela 38 – Variáveis do modelo de alta frequência do indutor de único enrolamento | 149 |

| Tabela 39 – Variáveis do modelo de alta frequência do indutor de único enrolamento | 150 |

| Tabela 40 – Componentes do Filtro de EMI . . . . .                                 | 156 |

| Tabela 41 – Principais características dos filtros <i>Feedback</i> . . . . .       | 160 |

| Tabela 42 – Principais características dos filtros <i>Feedback</i> . . . . .       | 161 |

| Tabela 43 – Principais características dos filtros <i>Feedback</i> . . . . .       | 162 |

| Tabela 44 – Principais características dos filtros <i>Feedback</i> . . . . .       | 162 |

| Tabela 45 – Componentes Passivos do Filtro Ativo . . . . .                         | 165 |

| Tabela 46 – Comparação Teórica e Simulada sobre os Esforços nos Componentes .      | 174 |

## LISTA DE ABREVIATURAS E SIGLAS

|           |                                                |

|-----------|------------------------------------------------|

| CA        | Corrente Alternada                             |

| CC        | Corrente Contínua                              |

| THD       | <i>Total Harmonic Distortion</i>               |

| PF        | <i>Power Factor</i>                            |

| PFC       | <i>Power Factor Corrector</i>                  |

| CCM       | <i>Continuous Conduction Mode</i>              |

| DCM       | <i>Descontinuous Conduction Mode</i>           |

| ZVS       | <i>Zero Voltage Switching</i>                  |

| ZCS       | <i>Zero Current Switching</i>                  |

| PWM       | <i>Pulse Width Modulation</i>                  |

| SPT       | <i>Single Phase Taipei</i>                     |

| BCCM      | <i>Boost in Continuos Conduction Mode</i>      |

| BIDCM     | <i>Boost Interleaved DCM</i>                   |

| TLI - DCM | <i>Three-Level Interleaved DCM</i>             |

| MLT       | <i>Mean Length of a Turn</i>                   |

| EMF       | <i>Eletromotive Force</i>                      |

| GSE       | <i>Generalized Steinmetz Equation</i>          |

| iGSE      | <i>Improved Generalized Steinmetz Equation</i> |

| MSE       | <i>Modified Steinmetz Equation</i>             |

| FOM       | <i>Figure Of Merit</i>                         |

| UF        | <i>Ultra Fast</i>                              |

| FM        | <i>Frequency Modulation</i>                    |

| SiC       | <i>Silicon Carbide</i>                         |

| PTH       | <i>Plated-Through Holes</i>                    |

| SMD       | <i>Surface Mount Tecnology</i>                 |

|      |                                                   |

|------|---------------------------------------------------|

| GaN  | <i>Gallium Nitride</i>                            |

| PET  | Polietileno Tereftaleno                           |

| PP   | Polipropileno                                     |

| PEN  | Polietileno Naftaleno                             |

| ESL  | <i>Equivalent Series Inductance</i>               |

| ESR  | <i>Equivalent Series Resistance</i>               |

| DF   | <i>Dissipation Factor</i>                         |

| FFT  | <i>Fast Fourier Transform</i>                     |

| VCO  | <i>Voltage Controlled Oscillator</i>              |

| NPC  | <i>Neutral Point Clamped Converter</i>            |

| PM   | <i>Phase Modulation</i>                           |

| FTLA | Função de Transferência de Laço Aberto            |

| MF   | Margem de Fase                                    |

| CI   | Circuito Integrado                                |

| EMI  | <i>Electromagnetic Interference</i>               |

| CM   | <i>Common Mode</i>                                |

| DM   | <i>Differential Mode</i>                          |

| EMC  | <i>Electromagnetic Interference Compatibility</i> |

| LISN | <i>Line Impedance Stabilization</i>               |

| IL   | <i>Insertion Loss</i>                             |

## LISTA DE SÍMBOLOS

|           |                                                              |

|-----------|--------------------------------------------------------------|

| $P$       | Potência Ativa                                               |

| $Q$       | Potência Reativa                                             |

| $S$       | Potência Aparente                                            |

| $V_{RMS}$ | Tensão Eficaz                                                |

| $I_{RMS}$ | Corrente Eficaz                                              |

| $K_\phi$  | Deslocamento Angular                                         |

| $\phi_V$  | Defasagem Tensão                                             |

| $\phi_I$  | Defasagem Corrente                                           |

| $C_f$     | Capacitor do Filtro de Entrada                               |

| $L_{in}$  | Indutor Boost                                                |

| $D$       | Diodo Retificador                                            |

| $S$       | Chave                                                        |

| $C_b$     | Capacitor Boost                                              |

| $L_m$     | Indutância de Magnetização do Indutor Acoplado de Modo Comum |

| $C_o$     | Capacitor de Barramento                                      |

| $R_o$     | Carga Resistiva                                              |

| $I_f$     | Corrente de Condução Direta                                  |

| $V_{RRM}$ | Máxima Tensão de Bloqueio Repetitivo no Diodo                |

| $V_{max}$ | Máxima Tensão de Bloqueio na Chave                           |

| $P_{CC}$  | Potência Comutada no Diodo                                   |

| $P_{CC}$  | Potência Comutada na Chave                                   |

| $A_e A_w$ | Produto entre a Seção e a Janela de um Núcleo Magnético      |

| $L$       | Indutância                                                   |

| $E_L$     | Energia de um Indutor                                        |

| $I_{pk}$  | Corrente de Pico                                             |

|               |                                                 |

|---------------|-------------------------------------------------|

| $\Delta_V$    | Ondulação de Tensão de Baixa Frequência         |

| $C$           | Capacitância                                    |

| $E_C$         | Energia de um Capacitor                         |

| $C_{oss}$     | Capacitância de Saída do Mosfet/IGBT/SiC/GaN    |

| $V_{in}$      | Tensão de Entrada                               |

| $N$           | Número de espiras                               |

| $g$           | gatilho                                         |

| $V_o$         | Tensão de Saída                                 |

| $Z_o$         | Impedância Natural do Filtro                    |

| $\omega_{o1}$ | Frequência Angular do Filtro LC de Entrada      |

| $\mu_o$       | Fator de Ressonância do Filtro                  |

| $\omega_s$    | Frequência Angular                              |

| $f_s$         | Frequência de Comutação                         |

| $f_r$         | Frequência da Rede Elétrica                     |

| $\Delta t_1$  | Duração da Etapa 1                              |

| $\Delta t_2$  | Duração da Etapa 2                              |

| $\Delta t_3$  | Duração da Etapa 3                              |

| $\Delta t_4$  | Duração da Etapa 4                              |

| $\Delta t_5$  | Duração da Etapa 5                              |

| $T_s$         | Período de Chaveamento                          |

| $T_r$         | Período da Rede Elétrica                        |

| $t_d$         | Tempo de Desmagnetização                        |

| $\alpha$      | Razão entre a tensão no capacitor $C_f$ e $V_o$ |

| $M$           | Indutância Mútua                                |

| $V_{LM}$      | Tensão Sobre a Indutância de Magnetização       |

| $k$           | Fator de Acoplamento                            |

|                 |                                                                |

|-----------------|----------------------------------------------------------------|

| $\Delta I_{LM}$ | Ondulação de Corrente de Alta Frequência na Indutância $L_M$   |

| $\Delta V_{Cb}$ | Ondulação de Tensão de Alta Frequência Sobre o Capacitor $C_b$ |

| $C_{out}$       | Capacitor Equivalente de Barramento                            |

| $P_{in}$        | Potência de Entrada                                            |

| $P_o$           | Potência de Saída                                              |

| $Q_{rr}$        | Carga de Portadores Minoritárias                               |

| $C_j$           | Capacitância da Junção do Diodo                                |

| $V_f$           | Tensão de Condução Direta                                      |

| $L_c$           | Indutor Acoplado                                               |

| $L_{lk}$        | Indutância de Dispersão                                        |

| $B_{max}$       | Máxima Indução Eletromagnética                                 |

| $V_c$           | Volume do Núcleo                                               |

| $V_g$           | Volume do Entreferro                                           |

| $l_c$           | Comprimento do Contorno de Linha de Campo do Núcleo            |

| $l_g$           | Comprimento do Contorno de Linha de Campo do Entreferro        |

| $\mu_o$         | Permeabilidade Eletromagnética no Vácuo                        |

| $\mu_r$         | Permeabilidade Relativa do Material                            |

| $g$             | Entreferro                                                     |

| $W_c$           | Energia do Núcleo                                              |

| $A_w$           | Seção Transversal de um Fio                                    |

| $W_a$           | Área da Janela do Núcleo                                       |

| $k_u$           | Fator de Ocupação do Núcleo                                    |

| $J_o$           | Densidade de Corrente Elétrica                                 |

| $\Delta_\phi$   | Variação de Fluxo Magnético                                    |

| $\Delta_T$      | Variação de Tempo                                              |

| $\mu_{eff}$     | Permeabilidade Efetiva                                         |

|                 |                                                     |

|-----------------|-----------------------------------------------------|

| $n_{cond}$      | Número de Condutores                                |

| $n_{cabolitz}$  | Número de Cabos Litz                                |

| $n_{fios,litz}$ | Número de Fios em um Cabo Litz                      |

| $R_{DC}$        | Resistência DC ou Contínua                          |

| $T_{max}$       | Temperatura Máxima                                  |

| $T_{amb}$       | Temperatura Ambiente                                |

| $P_{DC}$        | Perdas DC no Enrolamento                            |

| $\rho_o$        | Resistividade do Cobre                              |

| $\Delta_{Temp}$ | Variação de Temperatura                             |

| $\delta(f)$     | Profundidade de Penetração do Efeito <i>Skin</i>    |

| $R_{AC}$        | Perdas AC no Enrolamento                            |

| $\eta$          | Rendimento                                          |

| $P_{fe}$        | Perdas no Núcleo                                    |

| $\Delta B$      | Variação de Indução Eletromagnética                 |

| $P_{V-major}$   | Perdas no <i>Major Loop</i>                         |

| $P_{V-minor}$   | Perdas no <i>Minor Loop</i>                         |

| $R_\theta$      | Resistência Térmica                                 |

| $R_{ds}$        | Resistência de Condução entre Dreno e <i>Source</i> |

| $Q_{gd}$        | Carga entre <i>Gate</i> e Dreno                     |

| $Q_g$           | Carga de <i>gate</i>                                |

| $V_D$           | Tensão de Bloqueio do Diodo                         |

| $T_j$           | Temperatura de Junção                               |

| $C_j$           | Capacitância na Junção                              |

| $I_g$           | Corrente de Gatilho                                 |

| $C_{gs}$        | Carga entre <i>Gate</i> e <i>Source</i>             |

| $I_{gs}$        | Corrente entre <i>Gate</i> e <i>Source</i>          |

|                |                                                               |

|----------------|---------------------------------------------------------------|

| $I_{gd}$       | Carga entre <i>gate</i> e Dreno                               |

| $V_{GS}$       | Tensão entre <i>Gate</i> e <i>Source</i> ou Tensão de Gatilho |

| $V_{DS}$       | Tensão entre Dreno e <i>Source</i>                            |

| $C_{iss}$      | Capacitância de Entrada                                       |

| $I_{DS}$       | Corrente entre Dreno e <i>Source</i>                          |

| $V_{GS(th)}$   | Tensão de <i>Threshold Nominal</i>                            |

| $V_{GS(pl)}$   | Tensão de <i>Plateau</i>                                      |

| $R_{G(on)}$    | Resistência de Gatilho para Entrada em Condução               |

| $R_{G(off)}$   | Resistência de Gatilho para Entrada em Bloqueio               |

| $R_{G(int)}$   | Resistência de Gatilho Intrínseca                             |

| $C_{rss}$      | Capacitância de Transferência Reversa                         |

| $E_{on}$       | Energia de Entrada em Condução do Mosfet                      |

| $E_{off}$      | Energia de Entrada em Bloqueio do Mosfet                      |

| $P_{S(on)}$    | Potência na Entrada em Condução do Mosfet                     |

| $P_{S(off)}$   | Potência na Entrada em Bloqueio do Mosfet                     |

| $P_{cap,low}$  | Potência Dissipada em Baixa Frequência                        |

| $P_{cap,high}$ | Potência Dissipada em Alta Frequência                         |

| $P_D$          | Potência Dissipada no Díodo                                   |

| $P_S$          | Potência Dissipada na Chave                                   |

| $T_c$          | Temperatura no Encapsulamento                                 |

| $T_h$          | Temperatura no Dissipador                                     |

| $R_{jc}$       | Resistência Térmica entre Junção e Encapsulamento             |

| $R_{ch}$       | Resistência Térmica entre Encapsulamento e Dissipador         |

| $R_{ha}$       | Resistência Térmica entre Dissipador e Ambiente               |

| $C_{mod}$      | Capacitor do modulador VCO                                    |

| $IDC$          | Corrente de Referência no VCO                                 |

|                 |                                       |

|-----------------|---------------------------------------|

| $R_w$           | Resistência Intrínseca do Condutor    |

| $\Delta V_o$    | Variação da Tensão de Saída           |

| $A_d$           | Ganho do Amplificador Diferencial     |

| $f_p$           | Frequência do Polo                    |

| $I_{OH}$        | Máxima <i>Source Current</i>          |

| $I_{OL}$        | Máxima <i>Sink Current</i>            |

| $T_{am}$        | Período de Amostragem                 |

| $T_{delay}$     | Atraso de Propagação                  |

| $L_p$           | Indutância do Pino do Encapsulamento  |

| $C_f$           | Capacitância entre Espiras            |

| $R_m$           | Resistência Dielétrica entre Fios     |

| $\varepsilon_o$ | Permissividade Eletrostática no Vácuo |

| $\varepsilon_r$ | Constante Dielétrica do Isolante      |

| $C_X$           | Capacitor DM                          |

| $C_Y$           | Capacitor CM                          |

| $f_c$           | Frequência de Corte                   |

| $A_{asym}$      | Atenuação Assintótica                 |

| $I_{terra,rms}$ | Corrente Eficaz de Fuga               |

| $A$             | Ganho do Filtro Ativo                 |

| $z_s$           | Impedância da LISN                    |

| $z_n$           | Impedância Interna da Fonte           |

| $i_n$           | Fonte de Ruído                        |

| $I_{in}$        | Corrente de Entrada                   |

## SUMÁRIO

|          |                                                                                                     |           |

|----------|-----------------------------------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>INTRODUÇÃO . . . . .</b>                                                                         | <b>33</b> |

| 1.1      | CONTEXTUALIZAÇÃO E MOTIVAÇÃO DO TRABALHO . . . . .                                                  | 33        |

| 1.2      | OBJETIVO DO TRABALHO . . . . .                                                                      | 39        |

| 1.3      | ORGANIZAÇÃO DO TRABALHO . . . . .                                                                   | 40        |

| <b>2</b> | <b>ANÁLISE DA TOPOLOGIA . . . . .</b>                                                               | <b>41</b> |

| 2.1      | INTRODUÇÃO . . . . .                                                                                | 41        |

| 2.2      | TOPOLOGIA PROPOSTA . . . . .                                                                        | 41        |

| 2.3      | COMPARAÇÃO ENTRE AS PRINCIPAIS TOPOLOGIAS DO TIPO<br>BOOST <i>INTERLEAVED</i> MONOFÁSICAS . . . . . | 42        |

| 2.3.1    | Esforços e Custos com Semicondutores . . . . .                                                      | 42        |

| 2.3.2    | Volume e Custos com Componentes Passivos . . . . .                                                  | 43        |

| 2.3.3    | Principais Conclusões . . . . .                                                                     | 46        |

| 2.4      | ETAPAS DE OPERAÇÃO . . . . .                                                                        | 48        |

| 2.4.1    | Primeira Etapa de Operação . . . . .                                                                | 49        |

| 2.4.2    | Segunda Etapa de Operação . . . . .                                                                 | 49        |

| 2.4.3    | Terceira Etapa de Operação . . . . .                                                                | 49        |

| 2.4.4    | Quarta Etapa de Operação . . . . .                                                                  | 50        |

| 2.4.5    | Quinta Etapa de Operação . . . . .                                                                  | 51        |

| 2.4.6    | Sexta Etapa de Operação . . . . .                                                                   | 51        |

| 2.4.7    | Sétima Etapa de Operação . . . . .                                                                  | 51        |

| 2.4.8    | Oitava Etapa de Operação . . . . .                                                                  | 52        |

| 2.5      | ANÁLISE QUANTITATIVA . . . . .                                                                      | 55        |

| 2.5.1    | Filtro LC de Entrada . . . . .                                                                      | 55        |

| 2.5.2    | Tempos das Etapas de Operação . . . . .                                                             | 56        |

| 2.5.2.1  | <i>Primeira Etapa de Operação</i> . . . . .                                                         | 56        |

| 2.5.2.2  | <i>Segunda Etapa de Operação</i> . . . . .                                                          | 58        |

| 2.5.2.3  | <i>Terceira Etapa de Operação</i> . . . . .                                                         | 58        |

| 2.5.2.4  | <i>Quinta, Sexta e Sétima Etapas de Operação</i> . . . . .                                          | 58        |

| 2.5.3    | Característica de Saída . . . . .                                                                   | 60        |

| 2.5.4    | Indutância $L_{in}$ . . . . .                                                                       | 61        |

| 2.5.5    | Capacitância do Filtro de Entrada . . . . .                                                         | 62        |

| 2.5.6    | Indutor Acoplado . . . . .                                                                          | 63        |

| 2.5.7    | Capacitor Boost . . . . .                                                                           | 65        |

| 2.5.8    | Capacitores de Barramento . . . . .                                                                 | 65        |

| 2.5.9    | Corrente de Entrada . . . . .                                                                       | 67        |

| 2.5.10   | Potência, Fator de Potência e Taxa de Distorção Harmônica .                                         | 68        |

|          |                                                      |            |

|----------|------------------------------------------------------|------------|

| 2.6      | ESFORÇOS NOS COMPONENTES . . . . .                   | 69         |

| 2.6.1    | Metodologia . . . . .                                | 69         |

| 2.6.2    | Capacitor de Filtro . . . . .                        | 70         |

| 2.6.3    | Díodo da Ponte Retificadora . . . . .                | 71         |

| 2.6.4    | Indutor Boost . . . . .                              | 71         |

| 2.6.5    | Interruptor . . . . .                                | 71         |

| 2.6.6    | Díodo Intrínseco . . . . .                           | 72         |

| 2.6.7    | Capacitor Boost . . . . .                            | 72         |

| 2.6.8    | Capacitor de Saída . . . . .                         | 72         |

| 2.6.9    | Indutor Acoplado . . . . .                           | 73         |

| 2.7      | ANÁLISE DE COMUTAÇÃO . . . . .                       | 73         |

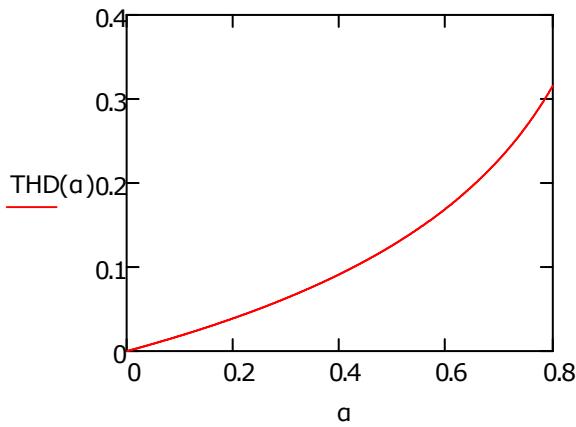

| 2.7.1    | Comutação com Perdas e Comutação Suave . . . . .     | 73         |

| 2.7.2    | <i>Comutação ZVS nos Interruptores</i> . . . . .     | 74         |

| 2.7.3    | Retificação Síncrona . . . . .                       | 74         |

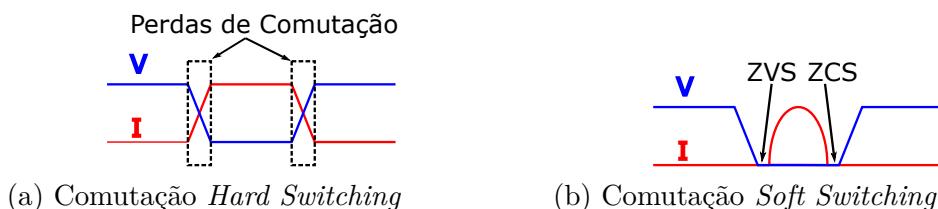

| 2.7.4    | Comutação Suave nos Diodos . . . . .                 | 75         |

| 2.7.5    | Tempo Morto Mínimo para Assegurar ZVS . . . . .      | 76         |

| <b>3</b> | <b>PROJETO DO CONVERSOR . . . . .</b>                | <b>81</b>  |

| 3.1      | ESCOLHA DOS PARÂMETROS . . . . .                     | 81         |

| 3.2      | DIMENSIONAMENTO DOS ELEMENTOS MAGNÉTICOS . . . . .   | 87         |

| 3.2.1    | <b>Indutor Boost . . . . .</b>                       | <b>88</b>  |

| 3.2.1.1  | <i>Tamanho Mínimo do Núcleo</i> . . . . .            | 88         |

| 3.2.1.2  | <i>Entreferro</i> . . . . .                          | 90         |

| 3.2.1.3  | <i>Número de Espiras</i> . . . . .                   | 90         |

| 3.2.2    | <b>Indutor de Modo Comum . . . . .</b>               | <b>91</b>  |

| 3.2.2.1  | <i>Tamanho Mínimo do Núcleo</i> . . . . .            | 91         |

| 3.2.2.2  | <i>Entreferro</i> . . . . .                          | 92         |

| 3.2.2.3  | <i>Número de Espiras</i> . . . . .                   | 92         |

| 3.2.3    | <b>Seção do Fio e Fator de Ocupação . . . . .</b>    | <b>92</b>  |

| 3.2.4    | <b>Perdas nos Enrolamentos . . . . .</b>             | <b>93</b>  |

| 3.2.4.1  | <i>Perdas DC</i> . . . . .                           | 93         |

| 3.2.4.2  | <i>Perdas AC</i> . . . . .                           | 94         |

| 3.2.5    | <b>Perdas no núcleo . . . . .</b>                    | <b>95</b>  |

| 3.2.6    | <b>Elevação de Temperatura . . . . .</b>             | <b>97</b>  |

| 3.2.7    | <b>Algoritmo e Resultados de Simulação . . . . .</b> | <b>97</b>  |

| 3.3      | <b>DIMENSIONAMENTO DOS SEMICONDUTORES . . . . .</b>  | <b>101</b> |

| 3.3.1    | <b>Figuras de Mérito . . . . .</b>                   | <b>101</b> |

| 3.3.2    | <b>Perdas no Díodo de Retificação . . . . .</b>      | <b>102</b> |

| 3.3.3    | <b>Perdas MOSFET . . . . .</b>                       | <b>104</b> |

| 3.4      | <b>DIMENSIONAMENTO DOS CAPACITORES . . . . .</b>     | <b>109</b> |

|         |                                                                                       |     |

|---------|---------------------------------------------------------------------------------------|-----|

| 3.4.1   | Capacitores de Filme . . . . .                                                        | 109 |

| 3.4.2   | Capacitores $C_f$ e $C_b$ . . . . .                                                   | 111 |

| 3.4.3   | Capacitores Eletrolíticos . . . . .                                                   | 114 |

| 3.4.4   | Capacitor $C_o$ . . . . .                                                             | 115 |

| 3.5     | CONCLUSÕES EM RELAÇÃO AOS PROJETOS . . . . .                                          | 117 |

| 3.6     | SPT <i>VERSUS</i> BCCM . . . . .                                                      | 120 |

| 3.6.1   | <b>Conversor BCCM</b> . . . . .                                                       | 120 |

| 3.6.2   | Diodos Retificadores . . . . .                                                        | 121 |

| 3.6.3   | Interruptores . . . . .                                                               | 122 |

| 3.6.4   | Díodo Boost . . . . .                                                                 | 123 |

| 3.6.5   | Indutor Boost . . . . .                                                               | 124 |

| 3.6.6   | Capacitor de Barramento . . . . .                                                     | 125 |

| 3.6.7   | Outros Componentes, Eficiência e Custos . . . . .                                     | 126 |

| 3.7     | DIMENSIONAMENTO DOS DISSIPADORES . . . . .                                            | 130 |

| 3.8     | ANÁLISE DA METODOLOGIA DE CONTROLE . . . . .                                          | 134 |

| 3.8.1   | Modelagem da Planta . . . . .                                                         | 134 |

| 3.8.2   | Extração da Função de Transferência . . . . .                                         | 134 |

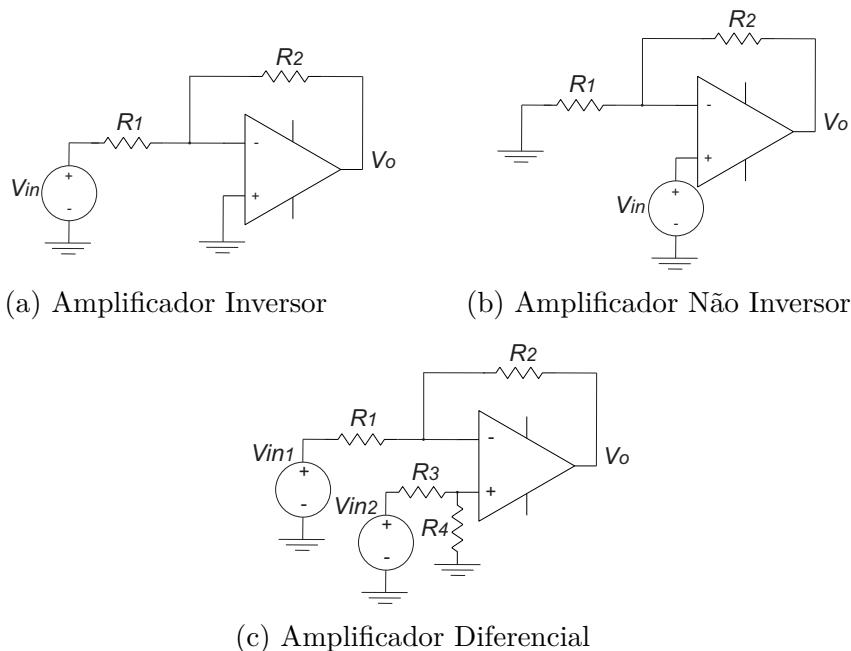

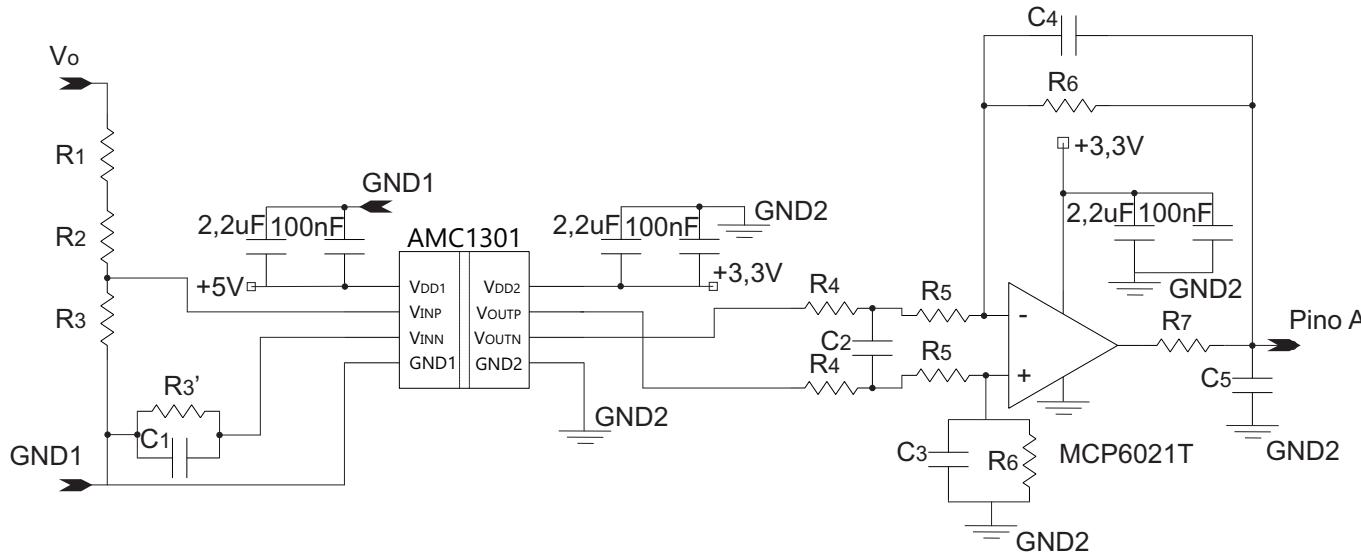

| 3.8.3   | Condicionamento de Sinal . . . . .                                                    | 137 |

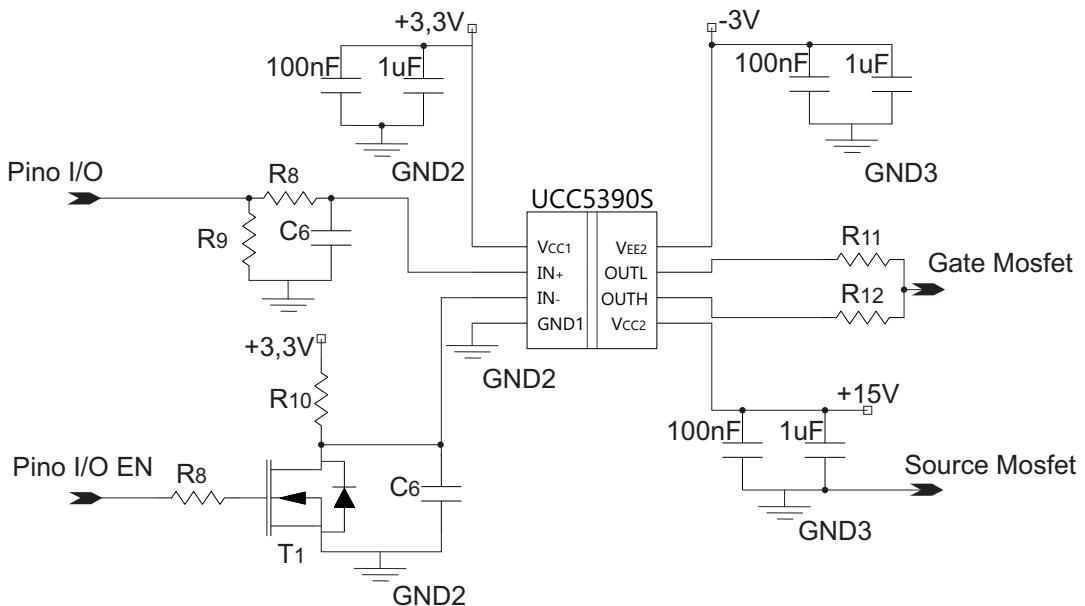

| 3.8.4   | <i>Driver</i> . . . . .                                                               | 138 |

| 3.8.5   | Proteção para o Conversor A/D . . . . .                                               | 140 |

| 3.8.6   | Controle Digital . . . . .                                                            | 142 |

| 3.9     | FILTRO DE EMI . . . . .                                                               | 144 |

| 3.9.1   | Normas . . . . .                                                                      | 145 |

| 3.9.2   | Modelos e Componentes Parasitas . . . . .                                             | 146 |

| 3.9.2.1 | <i>Modelo Semicondutores</i> . . . . .                                                | 147 |

| 3.9.2.2 | <i>Modelo Capacitores</i> . . . . .                                                   | 148 |

| 3.9.2.3 | <i>Modelo Indutores</i> . . . . .                                                     | 149 |

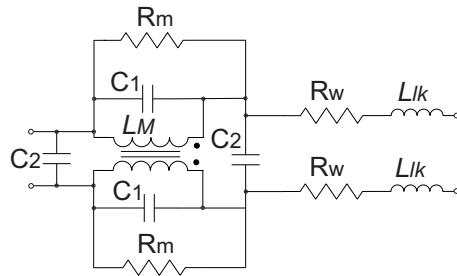

| 3.9.2.4 | <i>Modelo Indutores Acoplados</i> . . . . .                                           | 150 |

| 3.9.2.5 | <i>Modelo de Capacitâncias Parasitas entre Dissipador e Encapsulamentos</i> . . . . . | 150 |

| 3.9.3   | Estimação do Ruído de Entrada . . . . .                                               | 151 |

| 3.9.4   | Filtro de EMI passivo . . . . .                                                       | 152 |

| 3.9.5   | Otimização do Filtro de EMI . . . . .                                                 | 156 |

| 3.9.5.1 | <i>Tipos de Filtros Ativos e Modos de Compensação</i> . . . . .                       | 158 |

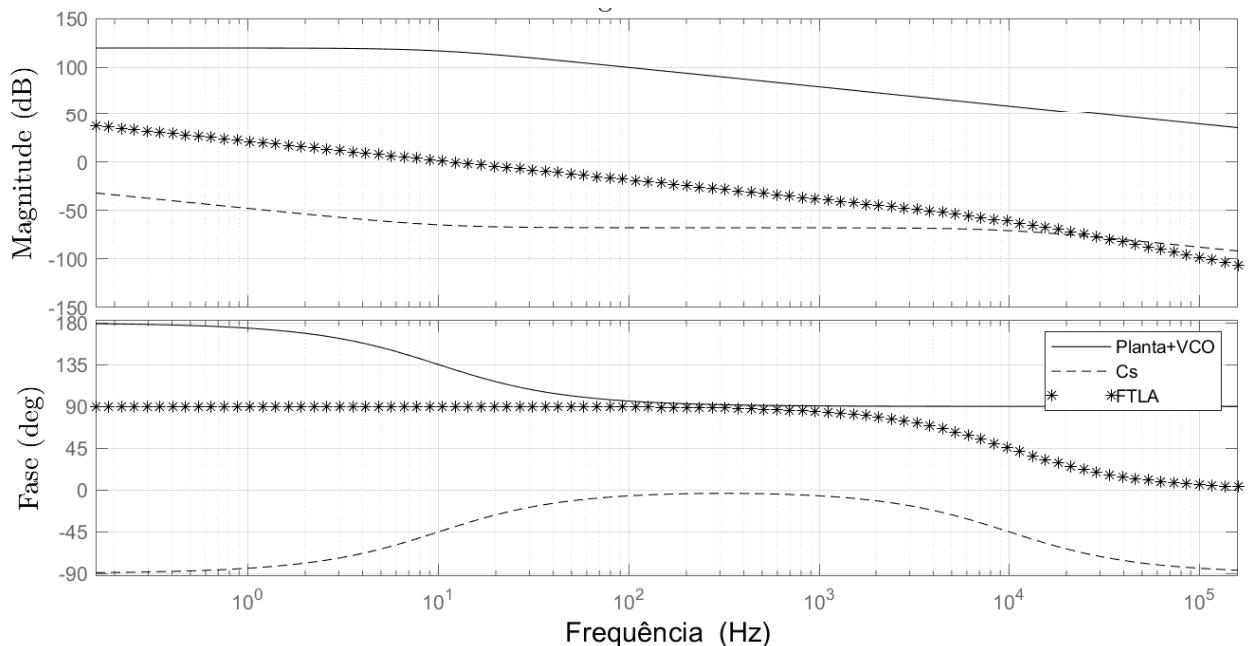

| 3.9.5.2 | <i>Projeto do Filtro Otimizado</i> . . . . .                                          | 163 |

| 4       | <b>RESULTADOS DO PROJETO</b> . . . . .                                                | 167 |

| 4.1     | SIMULAÇÃO DO CONVERSOR . . . . .                                                      | 167 |

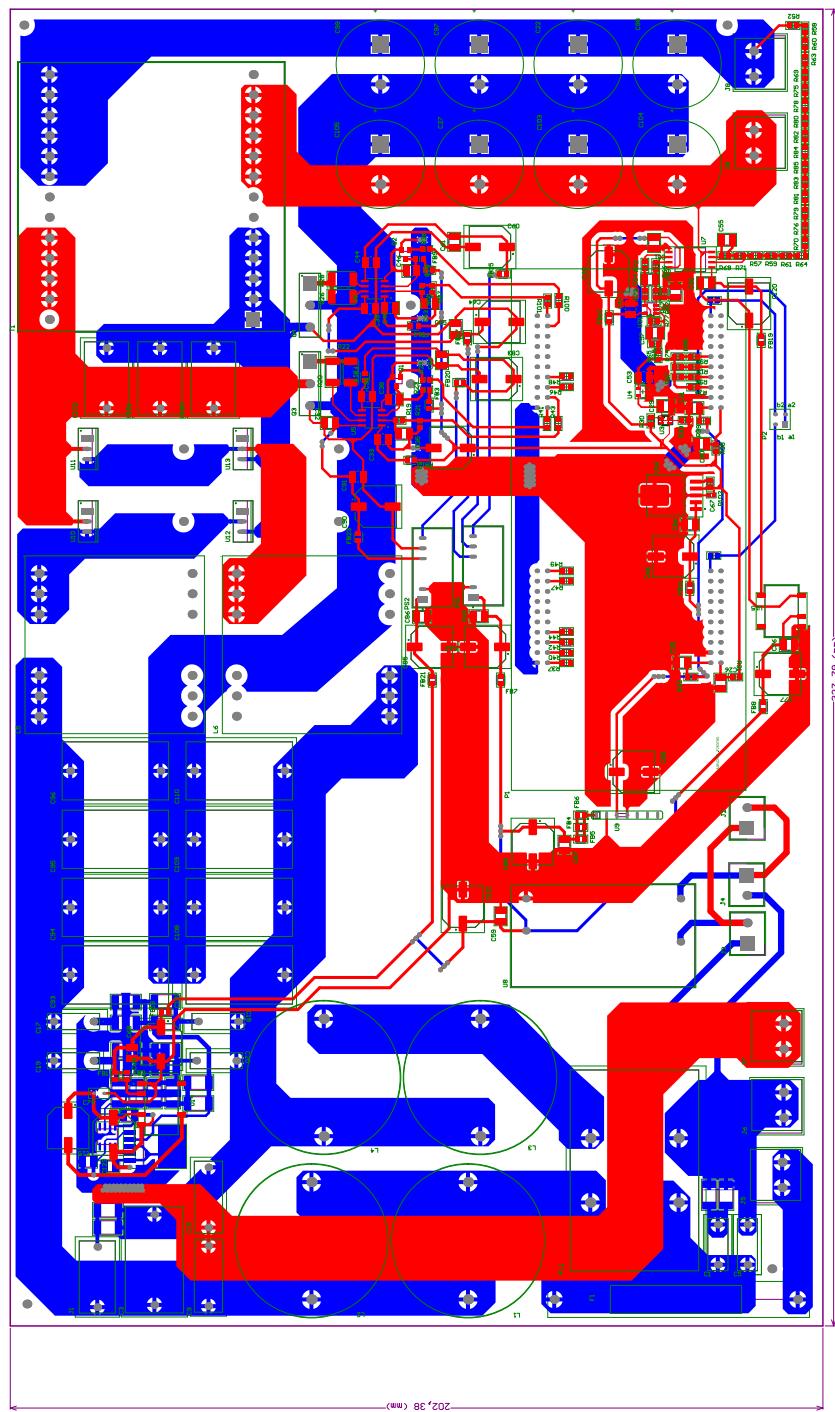

| 4.2     | PROJETO DE LAYOUT . . . . .                                                           | 174 |

| 4.3     | RESULTADOS DO PROTÓTIPO . . . . .                                                     | 176 |

|   |                       |     |

|---|-----------------------|-----|

| 5 | CONCLUSÕES . . . . .  | 177 |

|   | REFERÊNCIAS . . . . . | 179 |

|   | APÊNDICES             | 183 |

## 1 INTRODUÇÃO

### 1.1 CONTEXTUALIZAÇÃO E MOTIVAÇÃO DO TRABALHO

O ser humano está imerso em um mundo tecnológico, cercado por equipamentos elétricos e eletrônicos das mais diversas funções.

Parte desses equipamentos eletrônicos, sejam para aplicação doméstica, comercial ou industrial inclui no mínimo um conversor estático de corrente alternada (CA) para corrente contínua (CC) no primeiro estágio de alimentação, comumente chamado de conversor CA-CC ou retificador.

Diversas pesquisas vêm sendo feitas ao longo dos anos para melhorar a eficiência dos equipamentos eletrônicos, e parte desses esforços estão concentrados na melhoria dos conversores CA-CC. Tais melhorias incluem o aumento do rendimento energético, a redução do volume, diminuição dos custos e de interferências eletromagnéticas causadas por estes na rede elétrica.

Um dos primeiros desafios encontrado pelos pesquisadores é a minimização de energia reativa gerada por reatâncias capacitivas e indutivas presentes nos conversores.

A potência ativa ( $P$ ) de um circuito elétrico, apresentada em (1.1), é definida como a média da potência instantânea drenada pela carga. Também existe a potência reativa ( $Q$ ) (1.3), que é a parcela de potência que circula entre a fonte e a carga do circuito, sem realizar trabalho, suprindo os campos elétricos e magnéticos de capacitores e indutores, respectivamente. A energia reativa gera uma defasagem entre os fatores de tensão e corrente de entrada. Nesse defasamento, o sinal de corrente está atrasado em relação ao de tensão quando o circuito tem predominância indutiva, ou adiantado quando o circuito tem predominância capacitativa. Quanto maior for o deslocamento angular entre esses dois sinais, maior é a quantidade de potência reativa circulando no circuito, e consequentemente, menor é a parcela de potência útil drenada pela carga.

$$P = \frac{1}{T} \int_0^T v(t)i(t)dt \quad (1.1)$$

$$S = V_{RMS}I_{RMS} \quad (1.2)$$

$$Q = \sqrt{S^2 - P^2} \quad (1.3)$$

O somatório das potências ativa e reativa resultam na potência aparente ( $S$ ), descrita em (1.2), pelo produto de tensão e corrente eficaz drenado pela carga. Já o deslocamento

angular pode ser quantificado pela razão entre a potência ativa e aparente do circuito (1.4).

$$K_\phi = \cos(\phi_V - \phi_I) = \frac{P}{S} \quad (1.4)$$

Outro desafio é a minimização da distorção da corrente de entrada, ocasionada por componentes não lineares (semicondutores) do estágio de retificação. Ao comutá-los em alta frequência a forma de onda da corrente é alterada, deixando de ser puramente senoidal na frequência fundamental<sup>1</sup>. Essa distorção é resultado do somatório de  $n$  senoides múltiplos a frequência fundamental que se somam à forma de onda.

O problema disso, é que é necessário que haja sinais de tensão e corrente nas mesmas frequências para gerar potência ativa, algo que não ocorre para a maioria desses harmônicos. Portanto, a distorção harmônica causa a redução do valor da componente fundamental da corrente e diminui a quantidade de potência ativa entregue à carga.

A quantidade total de distorção (*Total Harmonic Distortion* - THD) é mensurada pelo somatório dos harmônicos contidos nas formas de ondas da tensão/corrente de entrada através do cálculo do valor eficaz<sup>2</sup> (*Root Mean Square* - RMS) das componentes senoidais divididas pela componente fundamental.

$$I_{RMS} = \sqrt{\sum_1^{\infty} \left[ \frac{1}{T_i} \int_0^{T_i} i_i^2 dt \right]} \quad (1.5)$$

$$THD_i = \frac{\sqrt{\sum_{i=2}^{\infty} I_i^2}}{I_1} \quad (1.6)$$

$$V_{RMS} = \sqrt{\sum_1^{\infty} \left[ \frac{1}{T_i} \int_0^{T_i} v_i^2 dt \right]} \quad (1.7)$$

$$THD_v = \frac{\sqrt{\sum_{i=2}^{\infty} V_i^2}}{V_1} \quad (1.8)$$

Os harmônicos de corrente são limitados por normas e recomendações que buscam assegurar que a THD gerada por equipamentos eletrônicos não prejudiquem a rede elétrica ou demais equipamentos conectados a ela (causam aumento de perdas e mal funcionamento). As principais normas são a IEC 61000-3-2 e IEC 61000-3-4, que se aplicam a equipamentos alimentados por tensão senoidal na faixa de 220V a 415V, onde o primeiro é destinado a fontes com corrente de até 16A, e o segundo acima 16A.

<sup>1</sup> frequência fundamental corresponde a frequência de tensão/corrente do sinal base, nesse caso da fonte de alimentação

<sup>2</sup> No cálculo do valor eficaz é incluído as componentes harmônicas além da componente fundamental

Os conceitos de deslocamento angular e taxa de distorção harmônica são incorporados no cálculo do fator de potência (*Power Factor* - PF) e servem de base para mensurar a qualidade da energia processada pelo conversor CA-CC. É desejável que o retificador entregue o máximo de potência ativa à carga, mantendo os sinais de tensão e corrente de entrada praticamente em fase e com um formato senoidal.

$$FP = \frac{\cos(\phi_{vi})}{\sqrt{1 + THD_i^2}} \quad (1.9)$$

O fator de potência pode ser melhorado de duas formas, utilizando componentes passivos para filtrar os harmônicos de frequência mais elevada e corrigir o deslocamento angular, ou utilizando componentes ativos, que cumprem o mesmo papel, incorporados em conversores estáticos, conhecidos como retificadores para correção de fator de potência (*Power Factor Corrector* - PFC).

Ambas as formas de correção podem ser implementadas, e a escolha do método varia conforme a carga, custos e aplicação desejada. Normalmente, o método de correção ativa é mais utilizado, pois alcança valores de PF mais elevados e exige componentes reativos menos volumosos, tornando uma solução mais econômica.

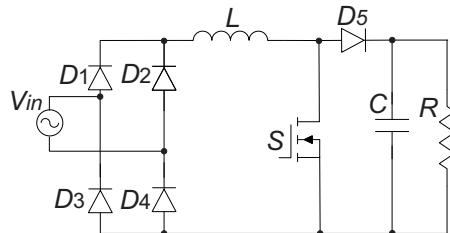

O retificador PFC mais difundido na literatura é o conversor DC-DC do tipo Boost associado a uma ponte retificadora, podendo operar em modo de condução contínua (*Continuous Conduction Mode* - CCM) quanto descontínua (*Descontinuous Conduction Mode* - DCM), a diferença entre os dois casos está no formato da corrente no indutor que pode ou não zerar a cada ciclo de comutação. Entre as diversas vantagens desse retificador está o número reduzido de componentes e o fator de potência elevado.

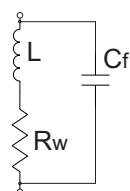

Figura 1 – Retificador Boost para Correção de Fator de Potência

Fonte: Elaborado pelo Autor

Embora essa topologia seja bastante promissora, há uma contínua procura por aprimoramentos, sendo comum a modificação dessa estrutura base em busca de algum benefício específico. Uma modificação bem comum é a implementação da técnica *Interleaved*.

*Interleaved Converter* ou Conversor Intercalado, é a aplicação de dois ou mais retificadores idênticos conectados em paralelo (descritos como células), controlados pela mesma malha de controle de forma intercalada na mesma frequência de comutação. A técnica já vem sendo aplicada a décadas em conversores do tipo Boost com o objetivo

de diminuir a ondulação de alta frequência (*ripple*) da corrente de entrada, através do cancelamento de componentes harmônicas entre os indutores, reduzindo emissão eletromagnética e gastos com filtros. Com a diminuição do *ripple* de corrente, o valor eficaz também diminui, reduzindo as perdas no núcleo e cobre, possibilitando o uso de elementos magnéticos reduzidos.

Conforme (CORUH et al., 2011), o emprego de retificadores *interleaved* proporciona uma eficiência maior ao conversor, reduz o volume do circuito de potência e melhora problemas de compatibilidade eletromagnética, embora exija um aumento no número de semicondutores e indutores proporcional a quantidade de retificadores em paralelo.

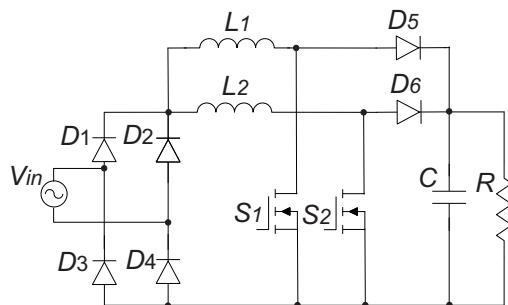

A Figura 2 apresenta a topologia mais comum do Boost *Interleaved*, empregada normalmente em aplicações de baixa potência. Conforme (CHAN; PONG, 1997), a ondulação na corrente de entrada pode ser eficientemente reduzida utilizando de 2 a 3 células em paralelo, utilizar um número maior que 3 células não implica necessariamente na redução efetiva da ondulação de corrente, mas propicia o uso de semicondutores com esforços menores, já que a corrente dos indutores é dividida pelos semicondutores de cada célula. Em (CHAN; PONG, 1997), foi obtido redução de até 50% do *ripple* em uma topologia com duas células empregando frequência de comutação fixa e uma redução de até 72% ao utilizar frequência de comutação variável.

Em (LEE et al., 2000) apresenta a possibilidade de acoplar os indutores de cada célula integrando um único núcleo, detendo as características de uma topologia *Interleaved*, ao passo que reduz volume de magnéticos se comparado com uma topologia boost tradicional com as mesmas características de projeto.

Figura 2 – Retificador Boost Interleaved Clássico com Duas Células Paralelas

Fonte: Elaborado pelo Autor

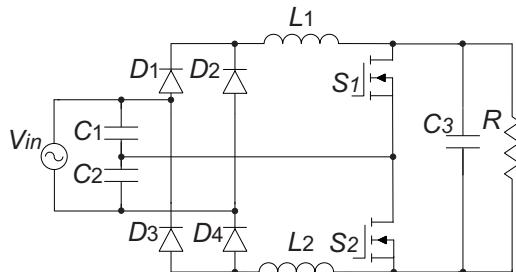

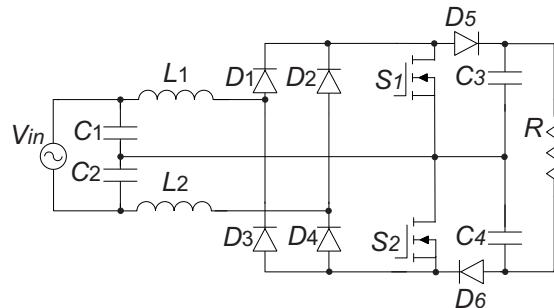

Outra solução do tipo *Interleaved* para o Retificador Boost é apresentada em (NABAE; NAKANO; ARAI, 1994), conhecido popularmente como Retificador Nabae e composto por duas células Boost DCM, apresentado na Figura 3.

A topologia apresenta alta imunidade para correntes de interferência eletromagnética de modo comum devido a simetria do circuito de potência em relação ao aterramento. Tal benefício implica no uso de um divisor capacitivo no lado AC da ponte retificadora, onde o ponto central é constituído por um neutro virtual que separa as duas células.

A simplicidade dos circuitos de controle e modulação dos interruptores é outro ponto atrativo. A corrente nos indutores segue naturalmente o sinal senoidal da tensão de entrada, necessitando somente de controle de tensão para o barramento DC, além disso, os interruptores operam de forma complementar com razão cíclica fixa em 50% utilizando modulação em frequência para controlar a transferência de potência.

As perdas de comutação são minimizadas, pois os interruptores são acionados com tensão nula (Zero Voltage Switching - ZVS). Os diodos boosts da topologia clássica não são empregados nessa estrutura, esse papel é cumprido pelos diodos intrínsecos aos MOSFETs/IGBTs. Também não há preocupação com perdas por recuperação reversa nos diodos devido ao formato descontínuo da corrente no indutor. A grande desvantagem da topologia são as perdas de condução causadas pelo modo de operação DCM. O capacitor de barramento é volumoso por causa do elevado conteúdo harmônico gerado pela magnetização dos indutores das células boost. Além disso, o conversor não é recomendado para tensões de barramento acima de 600V, pois a tensão dos interruptores é proporcional ao barramento.

No artigo é montado um protótipo de 75 W com frequência de comutação nominal (para 100 V de entrada) de 10 kHz. Foi obtido valores de THD de 14,2%, 8,16% e 6,013% sem a utilização de filtro de interferência eletromagnética, com carga nominal e tensão de entrada nominal, 150% e 200% respectivamente.

Figura 3 – Retificador Nabae

Fonte: Elaborado pelo Autor

Em (TAO; LEE, 2000) é apresentado uma modificação na topologia Nabae, de forma que o divisor capacitivo ligado ao neutro virtual seja realocado para o lado CC (Figura 4), após a ponte retificadora. Tal modificação possibilita o emprego de capacitores eletrolíticos, uma solução atrativa caso a topologia seja destinada a aplicações em potência elevada, aonde capacitores de filme acabam agregando bastante nos custos. Essa solução exige a adição de dois diodos em série com os indutores boost, elevando as perdas de condução.

O controle é análogo ao do conversor Nabae, controlando a tensão de barramento e fazendo a transferência de potência com variação de frequência, mantendo sempre os dois interruptores com razão cíclica fixa em 50%.

É montado um protótipo de 85W para tensão de entrada de 200 V, com frequência

de comutação de 52 kHz. O conversor atende a norma IEC1000-3-2 com THD de 9,2%, fator de potência de 0,994 e eficiência de 83%, com concentração de perdas na condução nos diodos.

Figura 4 – Retificador Nabae com capacitores eletrolíticos no filtro de entrada

Fonte: Elaborado pelo Autor

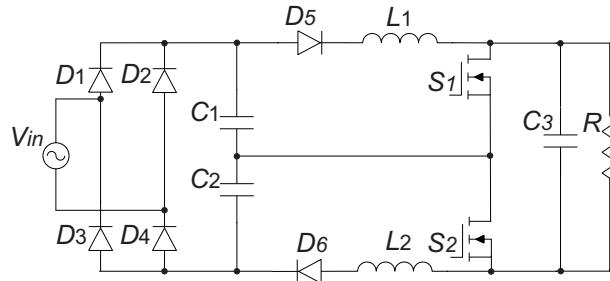

Em (GRANZA; FONT; GULES, 2015) é apresentado outra modificação na topologia Nabae (Figura 5) com o acréscimo de dois diodos entre o barramento DC e os interruptores, reduzindo os esforços de tensão nos interruptores pela metade, mas exigindo o acréscimo de dois diodos e um capacitor de barramento. O tipo de modulação é alterado, fazendo uso de PWM (*Pulse Width Modulation*) assimétrica<sup>3</sup> modificada, aonde os comandos dos interruptores são invertidos a cada meio ciclo da rede elétrica para manter a tensão nos capacitores de saída equilibrada.

Não é possível manter o acionamento ZVS dos interruptores com a modulação PWM, pois para valores menores de razão cíclica a energia acumulada no indutor boost não é o suficiente para descarregar completamente a capacitância de saída do interruptor.

Os autores montaram um protótipo de 1 kW, com tensão de entrada de 127 V, de saída 400 V e frequência de 40 kHz. O THD da corrente de entrada fica em 10,5%, atendendo a classe A da norma IEC61000-3-2, com fator de potência de 0,99 e eficiência de 90 %.

Figura 5 – Retificador Nabae com tensão reduzida nos interruptores

Fonte: Elaborado pelo Autor

<sup>3</sup> Os interruptores são modulados com frequência de comutação fixa e com razões cíclicas complementares, uma delas com razão cíclica D e a outra com (1-D)

## 1.2 OBJETIVO DO TRABALHO

Esse trabalho apresenta o estudo de um retificador PFC monofásico com solução ativa para aplicação em fontes de alimentação acima de 1 kW. A topologia utiliza a técnica *Interleaved* e possui semelhança ao retificador Nabae quanto a estrutura e modo de condução. Emprega ZVS para acionar os interruptores e ZCS (*Zero Current Switching*) no bloqueio dos diodos, havendo poucas perdas de comutação e possibilitando comutar os semicondutores em frequências mais elevadas para redução do volume de elementos magnéticos.

O cancelamento da ondulação de corrente de alta frequência entre os indutores gera uma corrente contínua na entrada, com baixo conteúdo harmônico se comparado com o Boost PFC DCM, por consequência, o filtro de entrada pode ser otimizado.

O circuito de controle é semelhante ao proposto por Nabae, com modulação em frequência nos interruptores. Isso é necessário caso seja desejável manter o acionamento via ZVS, e implica no deslocamento do espectro de harmônicos de corrente para frequências mais elevadas, como é apresentado por (CREBIER; REVOL; FERRIEUX, 2005). Por causa disso, certos cuidados devem ser tomados no projeto do filtro de interferências eletromagnéticas.

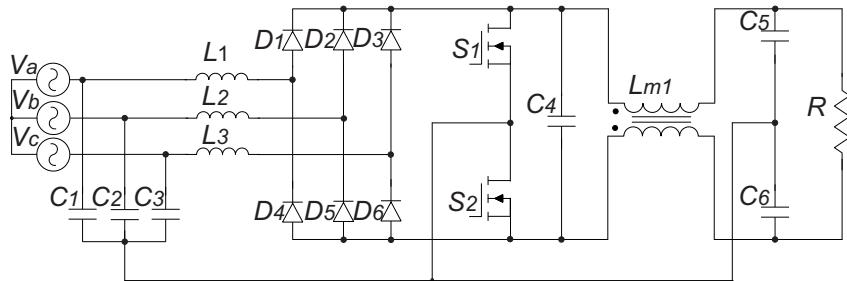

A ideia do trabalho surgiu a partir do conversor criado por Yungtaek Jang e Millan M. Jovanovic, que projetaram um retificador DCM *Interleaved* Boost com ponto central trifásico, denominado de retificador Taipei (Figura 6) e patenteado pela *Delta Products Corporation*. O conversor possui as mesmas vantagens citadas para a topologia a ser estudada, uma breve caracterização dela é apresentada em (Yungtaek Jang; JOVANOVIĆ, 2013), com resultados experimentais para um protótipo de 2,8 kW que alcança fator de potência 0,9967, THD de 1,43 % e eficiência de 97,51 % para valores nominais de operação.

Esses resultados são feitos com a utilização de um filtro de interferência eletromagnética do tipo  $\pi$  de dois estágios acoplado na entrada do conversor. É utilizado semicondutores com tecnologia SiC tanto para os interruptores quanto para os diodos, e os elementos magnéticos são construídos em núcleos de ferrite.

Devido ao número de vantagens e resultados atrativos alcançados pela estrutura trifásica, surgiu a dúvida, uma versão monofásica do retificador Taipei seria atrativa para indústria? Seria possível replicar os bons resultados de eficiência e ter poucos gastos com a estrutura?

Figura 6 – Topologia do Retificador Taipei

Fonte: Elaborado pelo Autor

### 1.3 ORGANIZAÇÃO DO TRABALHO

No estudo da nova topologia, os principais objetivos são:

- Estudo comparativo de retificadores semelhantes ao proposto, analisando parâmetros de eficiência, volume, complexidade de controle, número de componentes e entre outros.

- Estudo qualitativo do retificador com análise das etapas de operação e extração das principais equações para dimensionamento dos componentes.

- Elaboração de algoritmo para seleção de semicondutores levando em consideração eficiência e custo.

- Elaboração de algoritmo para projeto e seleção de indutores de forma a minimizar volume de material magnético e cobre mantendo a eficiência alta.

- Estudo da faixa de operação mais atrativa, bem como do potencial comercial da estrutura perante a outros retificadores já utilizados na indústria em faixas de potência semelhante.

- Estudo da interferência eletromagnética conduzida gerada pela topologia, bem como filtros para solucionarem esse problema.

- Estudo e obtenção de modelos matemáticos que caracterizam o comportamento dinâmico do conversor e a implementação destes em um circuito de controle.

- Construção e experimentação de um protótipo para validação dos estudos.

## 2 ANÁLISE DA TOPOLOGIA

### 2.1 INTRODUÇÃO

Esse capítulo apresenta o estudo matemático e o funcionamento do conversor, detalhando as etapas de operação juntamente com as principais formas de onda. Também são deduzidas as equações para dimensionamento dos componentes.

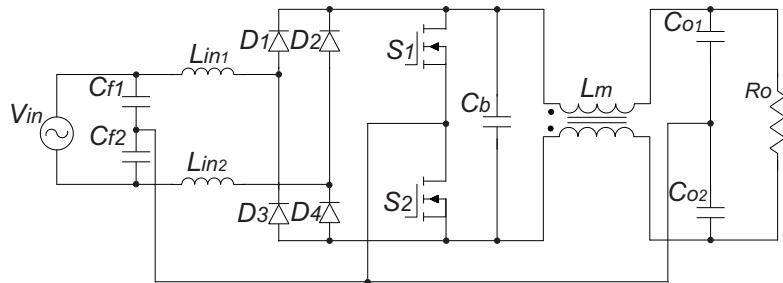

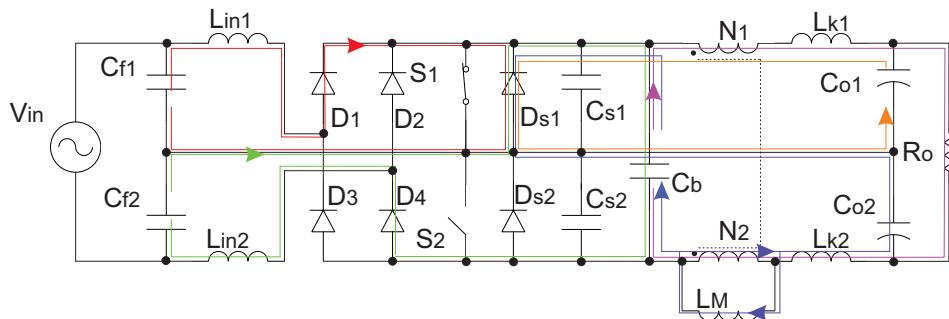

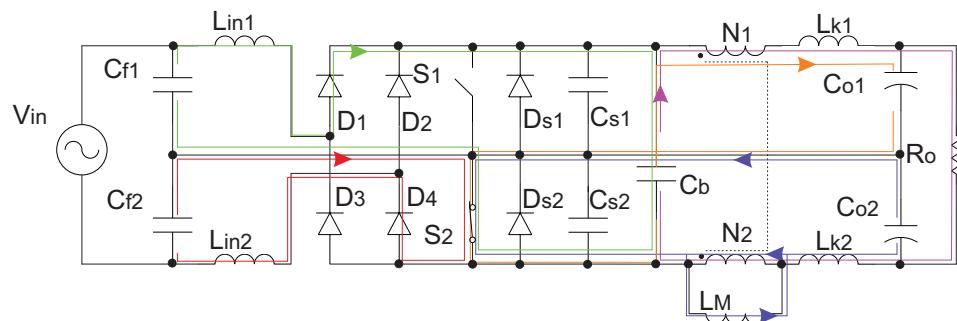

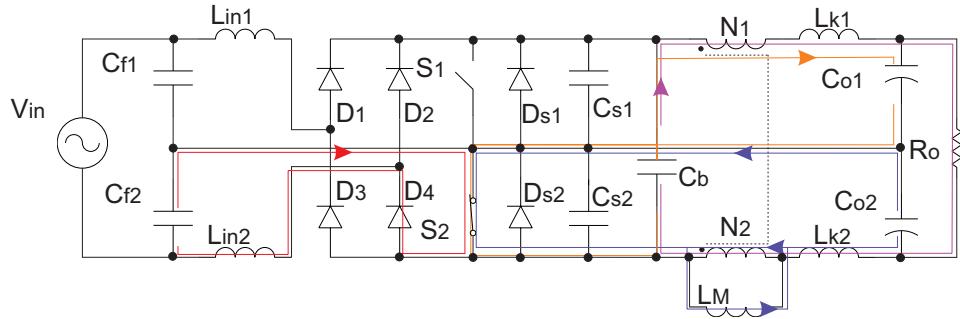

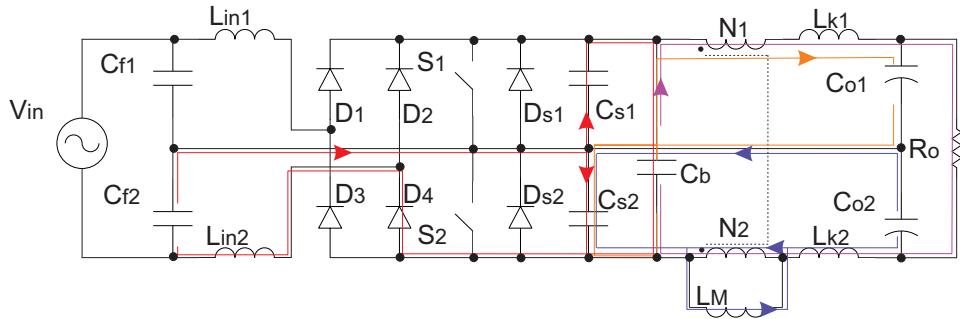

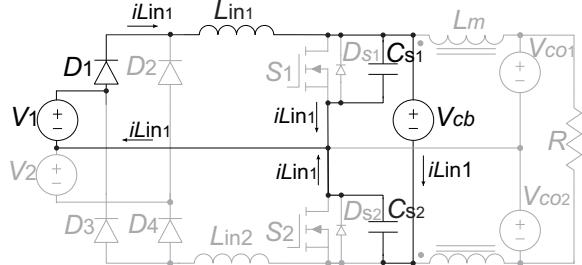

### 2.2 TOPOLOGIA PROPOSTA

A topologia a ser estudada é apresentada na Figura 7. O estágio de entrada é muito semelhante a topologia proposta por Nabae, a diferença é que os indutores são alocados a montante da ponte retificadora. Isso não influencia no modo de operação e é feito para diminuir a máxima tensão de bloqueio nos diodos retificadores. Esse valor ocorre no semiciclo em que eles não entram em condução, nesse caso, com o indutor a montante, a tensão máxima é proporcional ao barramento (limitada por  $C_b$ ). Com o indutor a jusante, o valor fica superior a tensão de barramento (Soma das tensões de  $C_b$  e de  $L_{in}$  sendo magnetizado).

Os interruptores operam de forma complementar, com razão cíclica fixa de 50% e modulação variando a frequência. O capacitor  $C_b$ , além de limitar a tensão nos diodos de retificação, absorve a corrente de desmagnetização de  $L_{in1}$  e  $L_{in2}$ . Reciprocamente, ele transfere energia aos capacitores de barramento  $C_{o1}$  e  $C_{o2}$  de forma intercalada, regulando a tensão de saída.

O indutor  $L_M$  é adicionado entre  $C_b$  e  $C_o$  com função de reduzir a corrente de modo comum gerada por  $C_b$ , que sofre elevadas variações de tensão conforme recebe e transfere energia ao barramento a cada desmagnetização de  $L_{in}$ . Portanto, a impedância de  $L_M$  reduz o conteúdo harmônico das correntes de desmagnetização, acabando com a desvantagem existente no retificador Nabae e seus semelhantes, o elevado valor de corrente eficaz nos capacitores de barramento. O indutor  $L_M$  é montado de forma que os fluxos de correntes diferentes se anulam, possibilitando projetar elevados valores de indutância de magnetização com um espaçamento de entreferro pequeno sem que o núcleo corra risco de saturação.

Os capacitores  $C_{o1}$  e  $C_{o2}$  compartilham o neutro virtual que divide as duas células boost, caracterizando o retificador como uma topologia com três níveis de tensão de saída. O balanceamento de  $C_o$  é facilmente mantido pela modulação em frequência, pois mantém igual as razões cíclicas nos dois interruptores.

O acionamento dos interruptores em ZVS é feito através da ressonância entre as capacitâncias intrínsecas dos interruptores e os respectivos indutores  $L_{in}$ , não sendo necessário a adição de componentes extras.

Os diodos da ponte retificadora e intrínsecos aos interruptores entram em bloqueio via ZCS, eliminando perdas por recuperação reversa.

Por ser um retificador derivado do Nabae e com as mesmas características do Taipei, a topologia será referenciada como SPT (*Single Phase Taipei* ou *Taipei Monofásico*).

Figura 7 – Topologia do Taipei Monofásico Proposta

Fonte: Elaborado pelo Autor

## 2.3 COMPARAÇÃO ENTRE AS PRINCIPAIS TOPOLOGIAS DO TIPO BOOST INTERLEAVED MONOFÁSICAS

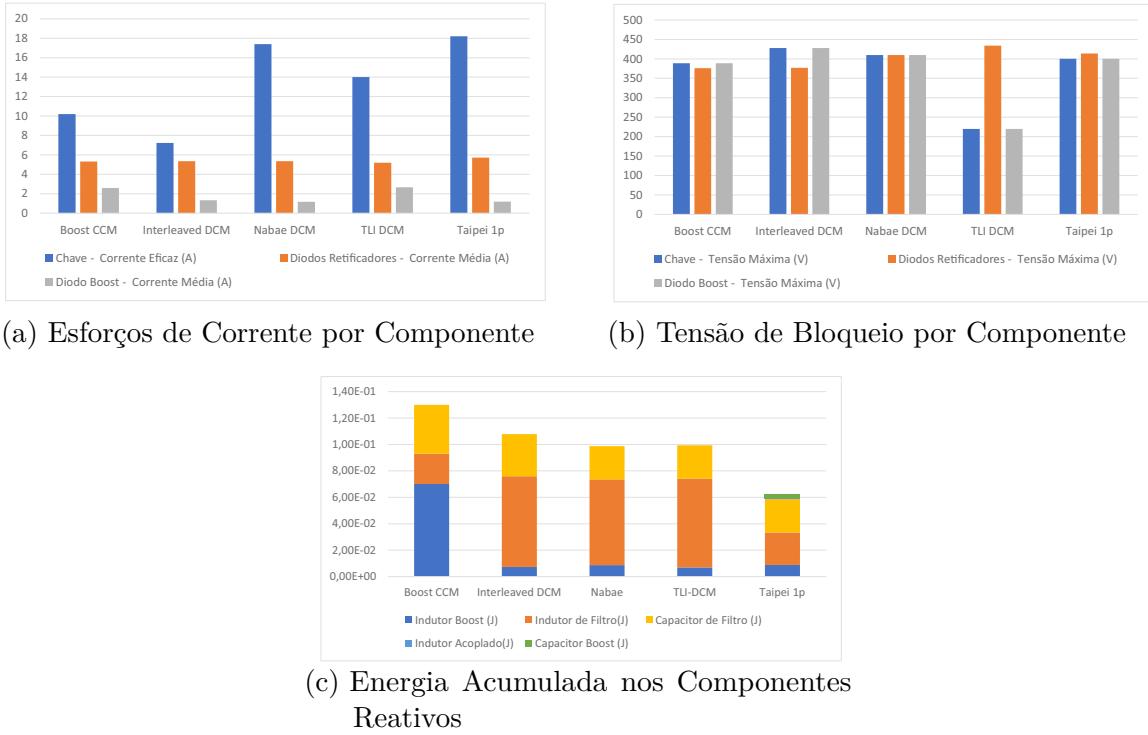

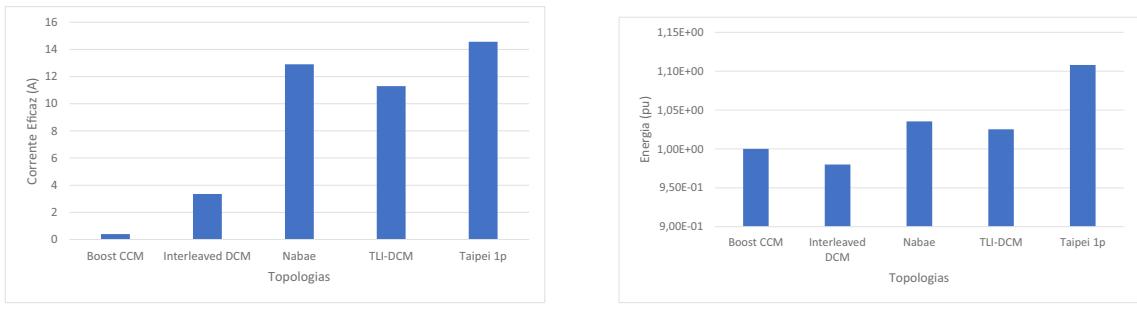

Com o intuito de explorar as vantagens econômicas e construtivas do SPT, ele foi comparado com alguns concorrentes que detém características semelhantes quanto ao modo de operação, faixa de potência e eficiência.

Na comparação o conversor BCCM (*Boost in Continuous Conduction Mode*) (Figura 1) é referenciado como o principal concorrente, por ser a topologia mais difundida na indústria para retificadores de baixa e média potência. Mas como o SPT opera em DCM, também é comparado com topologias que possuem o mesmo modo de operação, portanto também são analisados o retificador Nabae (Figura 3), o Boost *Interleaved DCM* (BIDCM) (Figura 2) e o *Three-Level Interleaved DCM* (TLI - DCM) (Figura 5).

Todos os retificadores são projetados para as mesmas condições de operação, isso pode ser injusto, pois os parâmetros escolhidos podem não ser o ponto ótimo de projeto para todos os retificadores listados, mas essa análise ajuda a esclarecer as diferenças entre os tipos de componentes que deverão ser empregados para cada estrutura, que é o foco principal da comparação. Os parâmetros de projeto são sumarizados na Tabela 1.

### 2.3.1 Esforços e Custos com Semicondutores

Nos semicondutores foi analisado o esforço de corrente e a tensão máxima de bloqueio, visando os limites físicos dos componentes. Também foi analisada a potência comutada, que ajuda a ter noção da potência instalada de semicondutores e possíveis gastos com dissipadores.

Tabela 1 – Parâmetros de Projeto