## **DESENVOLVIMENTO DE ALGORITMO PARA TOLERÂNCIA A FALHAS EM SISTEMAS CHAVEADOS**

Rafael Barbosa Sandoval Prado<sup>1</sup>, Tiago Jackson May Dezuo<sup>2</sup>

<sup>1</sup> Acadêmico do Curso de Engenharia Elétrica – CCT – bolsista PIVIC/UDESC

<sup>2</sup> Orientador, Departamento de Engenharia Elétrica – CCT – [tiago.dezuo@udesc.br](mailto:tiago.dezuo@udesc.br)

Palavras-chave: Algoritmo. Detecção de Falhas. Tratamento de Falhas

Sistemas chaveados abrange diversas áreas. A integridade do sistema é um dos fatores que, se fazem cada vez mais fundamental, para que a funcionalidade do complexo não seja comprometida.

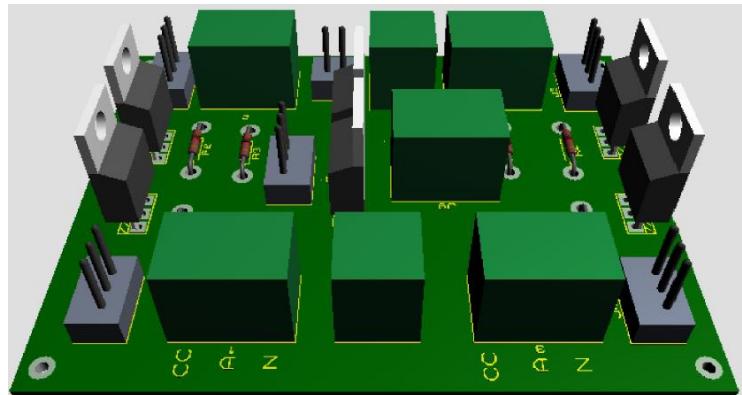

Existem diversas estruturas já consolidadas que visam garantir a integridade de um sistema chaveado como podemos observar na Figura 1 nos itens “b”, “c”, “d” e “e”, que consiste basicamente na adição de outras chaves. Caso uma chave falhe, as demais chaves ainda conseguem manter o sistema funcionando. As topologias diferem-se basicamente em como estas chaves estão associadas umas com as outras (Série, Paralelo, Série/Paralelo ou Paralelo/Série).

O propósito da pesquisa foi desenvolver um algoritmo para o controle de um modelo híbrido (Figura 1 item “f”), que foi proposto após revisões bibliográficas sobre as dificuldades das topologias já existentes. Esta nova topologia foi desenvolvida visando uma maximização da confiabilidade e da utilização das chaves para ambos os tipos de falhas: circuito aberto e curto-circuito.

Após esse modelo estabelecido, iniciou-se o desenvolvimento de um algoritmo com o intuito de reconhecer, identificar e isolar qualquer falha que possa vir a afigir a estrutura. Para realizar a detecção, o algoritmo irá comparar o estado das saídas e de cada chave com o comando de chaveamento, caso haja alguma divergência, será detectado que houve uma falha na estrutura. Após a identificação da falha, o *software* começará a identificação do modo de falha que afigiu o sistema (curto-circuito ou circuito aberto). Após o reconhecimento da falha e do seu tipo, o algoritmo irá isolar em qual dos componentes a mesma ocorreu.

Após o processo de identificação e isolamento, o programa irá manter registrado o tipo de falha de forma com que o software, ao selecionar a próxima sequência de chaveamento leve em consideração o erro, evitando a mesma ou a utilizando dependendo do tipo de chaveamento necessário e o tipo do estado de falha do componente.

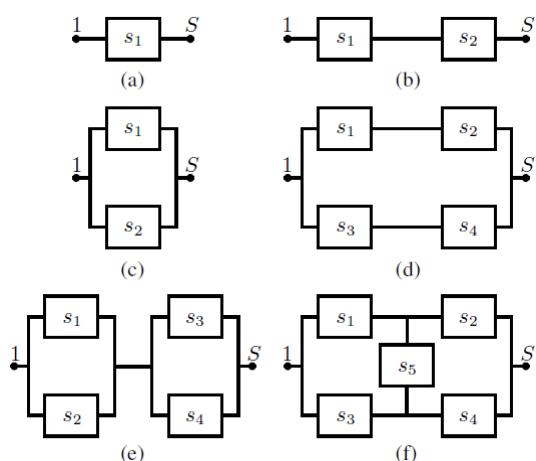

Para realizar a validação do *software* iniciou-se o projeto de uma placa de circuito impresso com a mesma topologia da Figura 1 item “f”, que pode ser observada na Figura 2. Esta placa foi projetada com o intuito de emular situações de curto circuito e circuito aberto e o funcionamento normal das chaves para a que se fosse possível impor defeitos no sistema a fim de aferir se o código desenvolvido fosse capaz de reconhecer erros no chaveamento, determinar qual foi o tipo de falha e indicar o seu local. Um dos pontos principais a serem testados é o fato do

código se adaptar a nova condições das chaves para poder gerar uma nova sequência de chaveamentos independente das falhas existentes assegurar a integridade do sistema.

Para poder emular um curto-circuito e um circuito aberto foi colocado uma chave manual em paralelo com o transistor. Esta chave em paralelo permite que o usuário imponha uma falha ao sistema enquanto o transistor está sendo operado normalmente em paralelo. Para facilidade na obtenção de dados da placa foi colocado pinos na mesma para um acesso mais fácil com qualquer equipamento de medição.

Um dos fatores a ser levado em consideração, para o algoritmo selecionar qual será a próxima sequência de chaveamento, é a utilização do mínimo de chaves possíveis, a fim de diminuir a complexidade do chaveamento e o uso desnecessário de componentes. Outro ponto importante, considerado para a definição do chaveamento, é a periodicidade com qual cada chave será acionada visando não sobrecarregar nenhum componente.

Para futuros estudos, a implementação de uma leitura térmica das chaves para a identificação de qual está sendo mais utilizada e quais estão ociosas, determinando qual chave será utilizada no próximo chaveamento é algo interessante de se analisar, pois estará sendo levado em consideração para o chaveamento mais do que o estado das chaves, mas sim, todo o funcionamento da mesma.

Um ponto interessante que se pode trabalhar é a possibilidade do sistema chaveado entregar na saída uma tensão diferente da de entrada na qual o usuário possa determinar este nível de tensão. Esse controle da tensão de saída poderá ser feito variando a frequência com que cada chave irá trabalhar, podendo assim implicar qual será o tempo em aberto e o tempo em fechado de cada uma das estruturas para se chegar a um valor médio de tensão desejado, como nos conversores CC/CC, ainda assim mantendo a característica de tolerância a falhas.

Figura 1: Topologias utilizadas para aumentar a confiabilidade do sistema

Figura 2: Modelo 3D do projeto da placa de circuito impresso para a emulação e validação do software